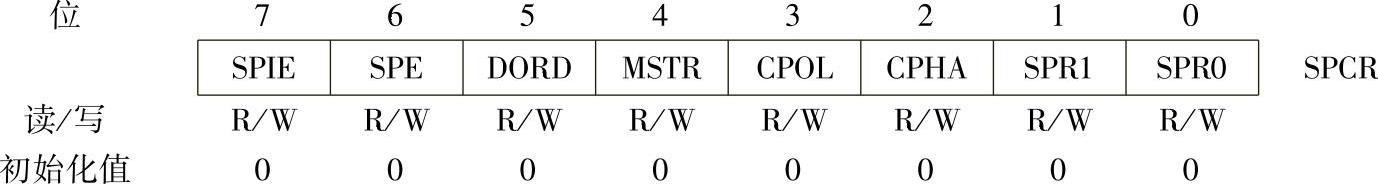

1.SPI控制寄存器——SPCR

(1)位7——SPIE:使能SPI中断

置位后,只要SPSR寄存器的SPIF和SREG寄存器的全局中断使能位置位,就会引发SPI中断。

(2)位6——SPE:使能SPI

SPE置位将使能SPI。进行任何SPI操作之前必须置位SPE。

(3)位5——DORD:数据次序

DORD置位时数据的LSB首先发送;否则数据的MSB首先发送。

(4)位4——MSTR:主/从选择MSTR置位时选择主机模式,否则为从机。如果MSTR为“1”, 配置为输入,但被拉低,则MSTR被清零,寄存器SPSR的SPIF置位。用户必须重新设置MSTR进入主机模式。

配置为输入,但被拉低,则MSTR被清零,寄存器SPSR的SPIF置位。用户必须重新设置MSTR进入主机模式。

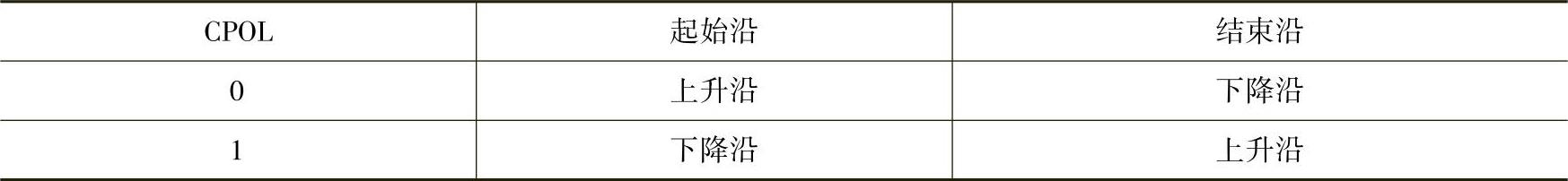

(5)位3——CPOL:时钟极性

CPOL置位表示空闲时SCK为高电平;否则空闲时SCK为低电平。请参考表10-2与表10-3,CPOL功能总结如下:

(6)位2——CPHA:时钟相位

CPHA决定数据是在SCK的起始沿采样还是在SCK的结束沿采样。请参考表10-2与表10-3。

表10-2 CPHA功能

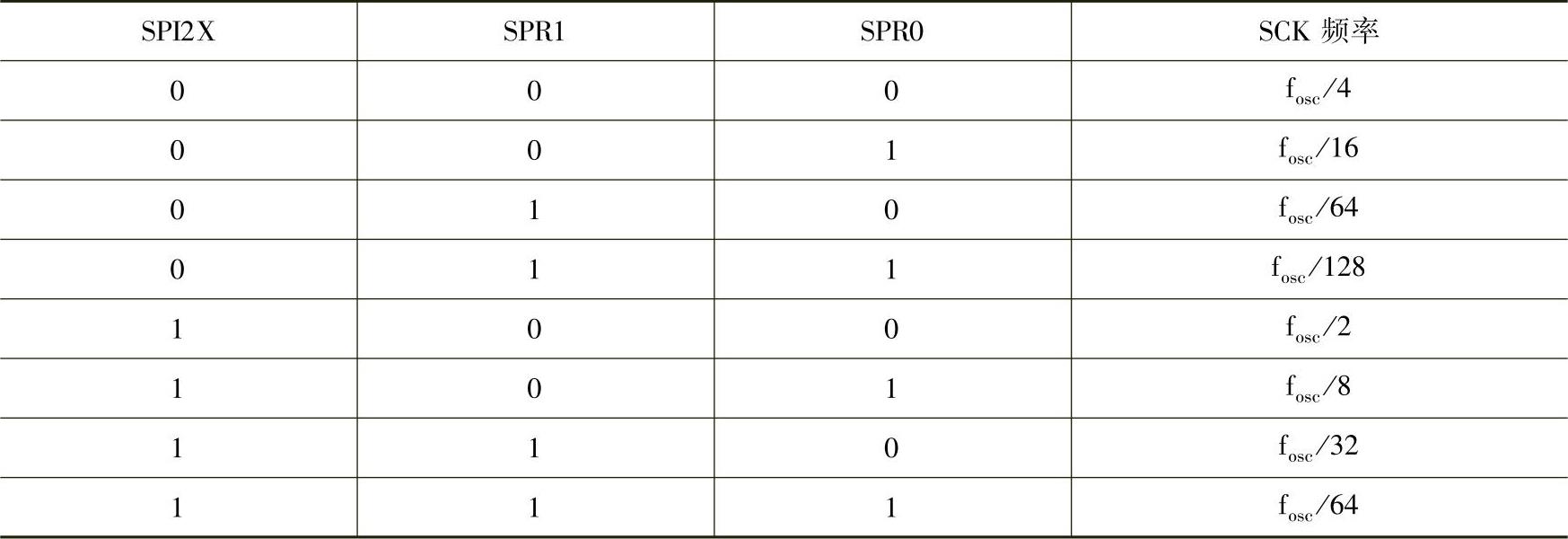

(7)位[1∶0]——SPR[1∶0]:SPI时钟速率选择1与0

确定主机的SCK速率。SPR1和SPR0对从机没有影响。SCK和振荡器的时钟频率fosc的关系如表10-3所示。(https://www.xing528.com)

表10-3 SCK和振荡器频率的关系

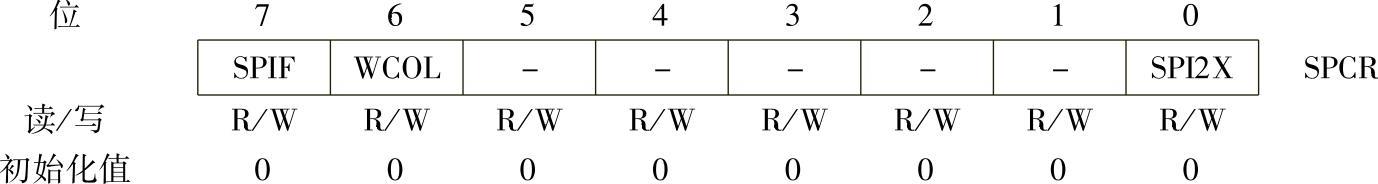

2.SPI状态寄存器——SPSR

(1)位7——SPIF:SPI中断标志

串行发送结束后,SPIF置位。若此时寄存器SPCR的SPIE和全局中断使能位置位,SPI中断即产生。如果SPI为主机, 配置为输入,且被拉低,SPIF也将置位。进入中断服务程序后SPIF自动清零。或者可以通过先读SPSR,紧接着访问SPDR来对SPIF清零。

配置为输入,且被拉低,SPIF也将置位。进入中断服务程序后SPIF自动清零。或者可以通过先读SPSR,紧接着访问SPDR来对SPIF清零。

(2)位6——WCOL:写冲突标志

在发送当中对SPI数据寄存器SPDR写数据将置位WCOL。WCOL可以通过先读SPSR,紧接着访问SPDR来清零。

(3)位[5∶1]——Res:保留

保留位,读操作返回值为零。

(4)位0——SPI2X:SPI倍速

置位后SPI的速度加倍,见表10-3。若为主机,则SCK频率可达CPU频率的一半。若为从机,只能保证fosc/4。

ATmega16的SPI接口同时还用来实现程序和EEPROM的下载和上传。

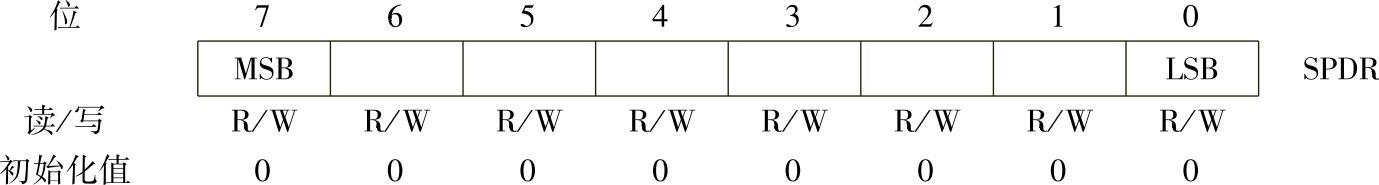

3.SPI数据寄存器——SPDR

SPI数据寄存器为读/写寄存器,用来在寄存器文件和SPI移位寄存器之间传输数据。写寄存器将启动数据传输,读寄存器将读取寄存器的接收缓冲器。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。