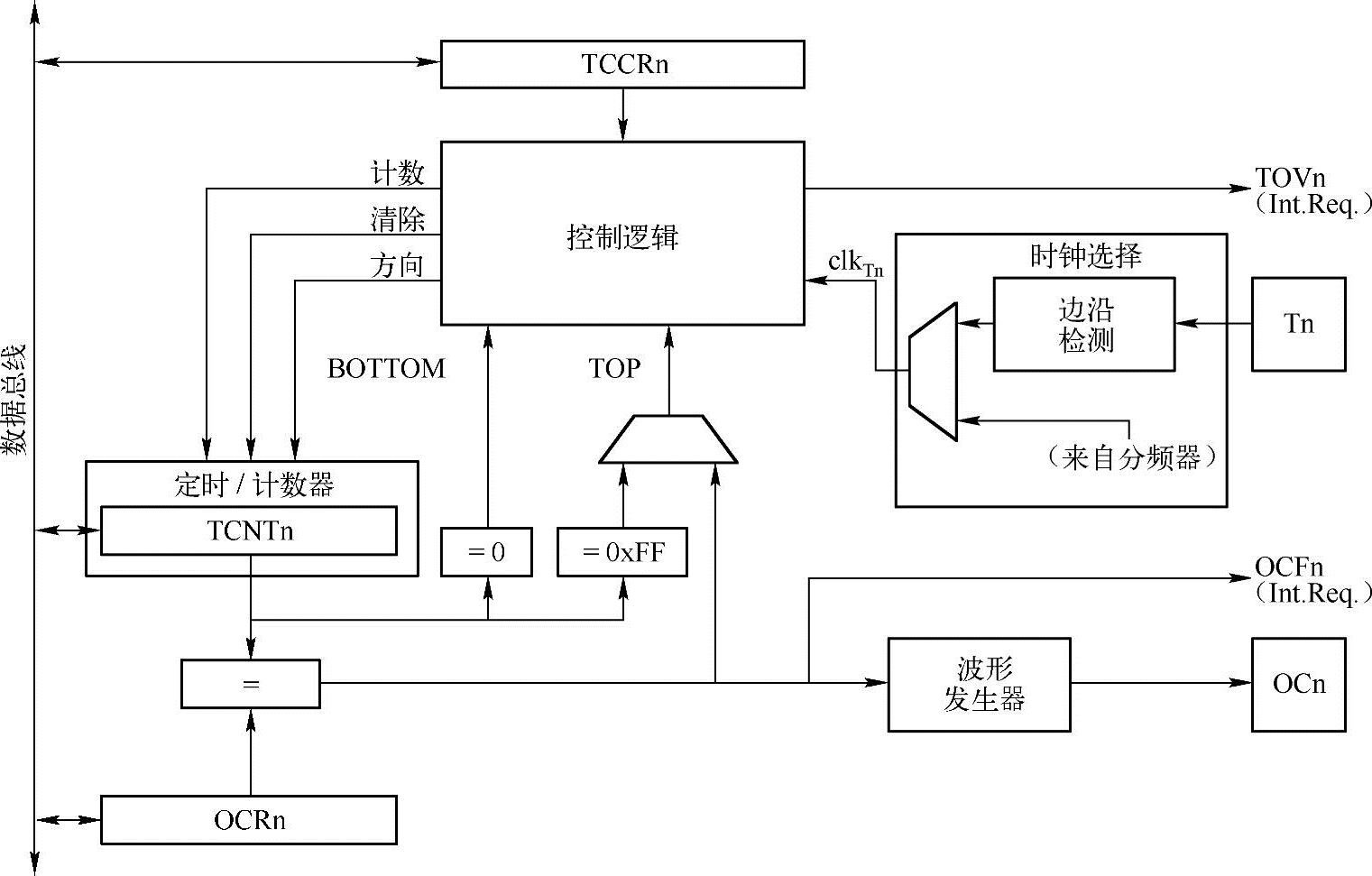

图7-1为8位定时计数器T/C0的硬件结构框图。

1.寄存器

T/C0(TCNT0)和输出比较寄存器(OCR0)为8位寄存器。中断请求(图中简写为Int.Req.)信号在定时器中断标志寄存器TIFR都有反映。所有中断都可以通过定时器中断屏蔽寄存器TIMSK单独进行屏蔽。由于TIFR和TIMSK由几个定时器单元共享,所以图7-1中没有给出TIFR和TIMSK。

图7-1 8位T/C0的结构框图

T/C0可以通过预分频器由内部时钟源驱动,或者是通过T0引脚的外部时钟源来驱动。时钟选择逻辑模块控制使用哪一个时钟源与什么边沿来增加(或降低)T/C的数值。如果没有选择时钟源T/C0就不工作。时钟选择模块的输出定义为定时器时钟clkT0。

双缓冲的输出比较寄存器OCR0一直与T/C0的数值进行比较。比较的结果可用来产生PWM波,或在输出比较引脚OC0上产生变化频率的输出,比较匹配事件还将置位比较标志OCF0。此标志可以用来产生输出比较中断请求。

2.定义

本文的许多寄存器及其各个位以通用的格式表示。小写的“n”取代了T/C的序号,在此即为0。小写的“x”取代了输出比较单元通道,在此即为通道A。但是在写程序时要使用精确的格式,例如使用TCNT0来访问T/C0计数器值。

BOTTOM、TOP、MAX的定义如下所示。

BOTTOM:计数器计到0x00时即达到BOTTOM。

MAX:计数器计到0xFF(十进制的255)时即达到MAX。

TOP:计数器计到计数序列的最大值时即达到TOP。TOP值可以为固定值0xFF(MAX),或是存储于寄存器OCR0A里的数值,具体由工作模式确定。

3.T/C0的时钟源

T/C0可以由内部同步时钟或外部异步时钟驱动。时钟源是由时钟选择逻辑决定的,而时钟选择逻辑是由位于T/C0控制寄存器TCCR0的时钟选择位CS02∶0控制的。

4.计数器单元

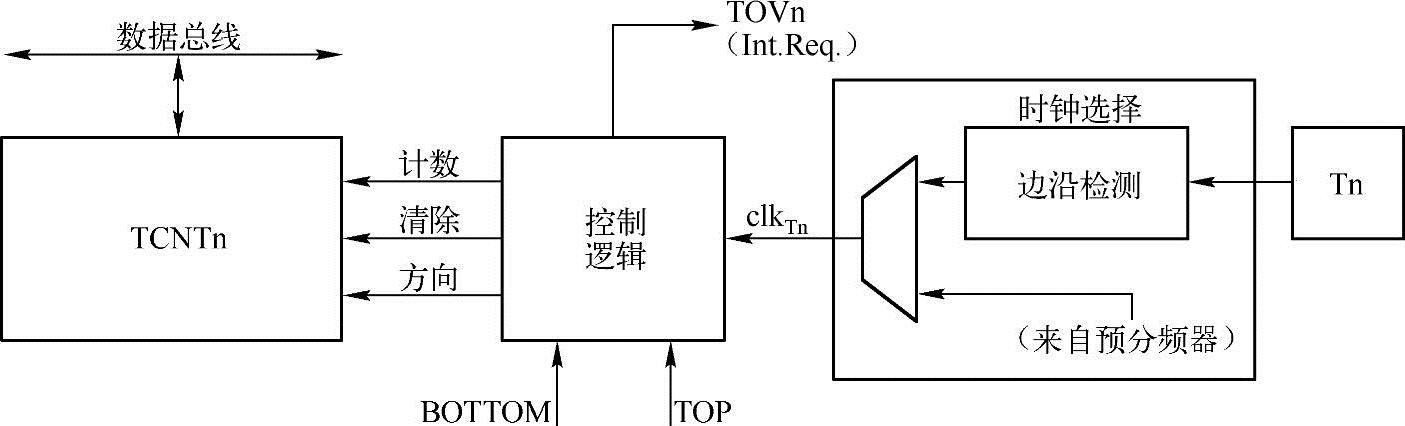

8位T/C的主要部分为可编程的双向计数单元。图7-2即为计数器和周边电路的框图。

图7-2 T/C0计数单元逻辑功能图

图中符号所代表的意义如下:

●计数(count):TCNT0加1或减1。

●方向(direction):加或减的控制。

●清除(clear):清零TCNT0。

●计数时钟(clkT0):C/T0时钟源。(https://www.xing528.com)

●顶部值(TOP):表示TCNT0计数值到达上边界。

●底部值(BOTTOM):表示TCNT0计数值到达下边界(零)。

根据不同的工作模式,计数器针对每一个clkT0实现清零、加1或减1操作。clkT0可以由内部时钟源或外部时钟源产生,具体由时钟选择位CS02∶0确定。没有选择时钟源时(CS02∶0=0)定时器即停止。但是不管有没有clkT0,CPU都可以访问TCNT0。CPU写操作比计数器其他操作(如清零、加减操作)的优先级高。

计数序列由T/C控制寄存器(TCCR0)的WGM01和WGM00决定。计数器计数行为与输出比较OC0的波形有紧密的关系。T/C溢出中断标志TOV0根据WGM01∶0设定的工作模式来设置。TOV0可以用于产生CPU中断。

5.输出比较单元

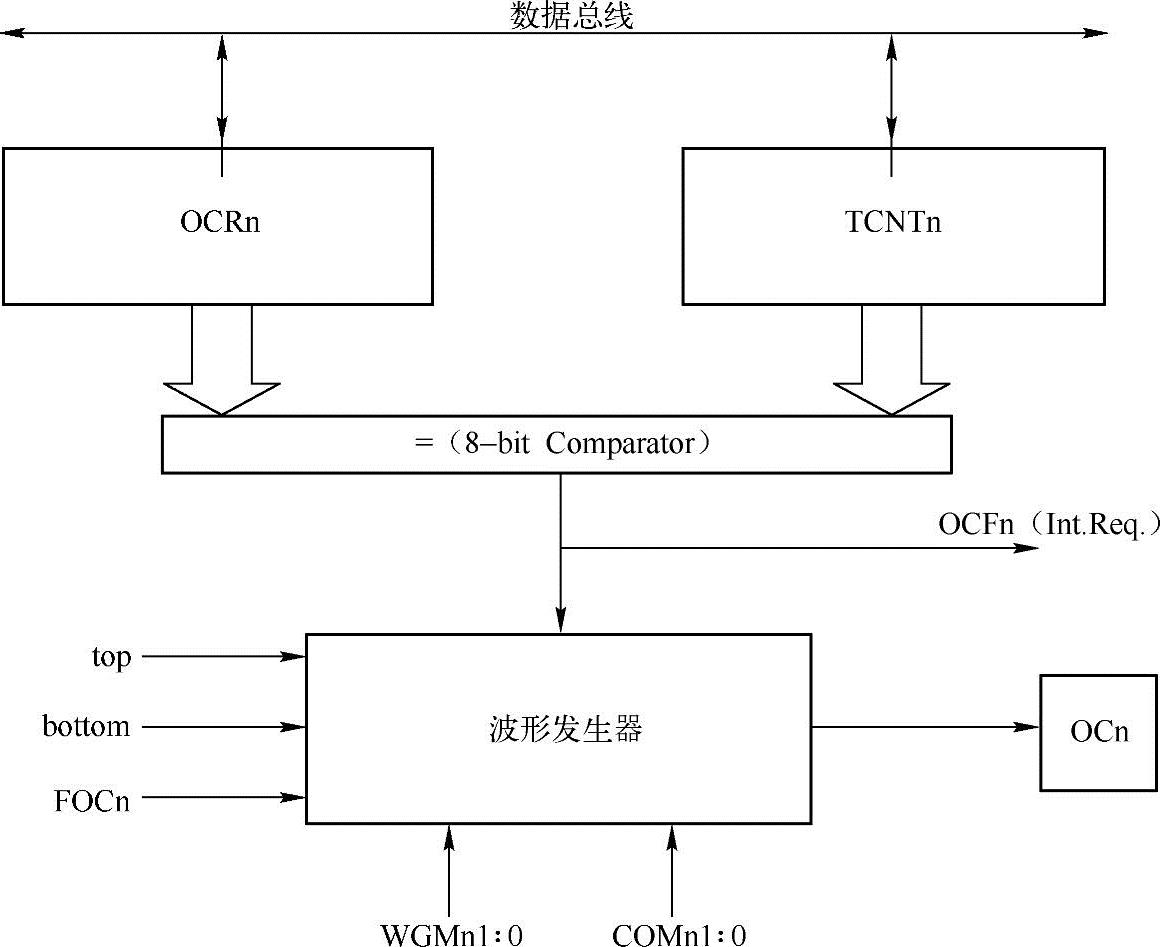

8位比较器持续对TCNT0和输出比较寄存器OCR0进行比较。一旦TCNT0等于OCR0,比较器就给出匹配信号。在匹配发生的下一个定时器时钟周期输出比较标志OCF0置位。若此时OCIE0=1且SREG的全局中断标志I置位,CPU将产生输出比较中断。执行中断服务程序时OCF0自动清零,或者通过软件写“1”的方式来清零。根据由WGM21∶0和COM01∶0设定的不同的工作模式,波形发生器利用匹配信号产生不同的波形。同时,波形发生器还利用max和bottom信号来处理极值条件下的特殊情况。图7-3为输出比较单元的框图。

使用PWM模式时OCR0寄存器为双缓冲寄存器;而在正常工作模式和匹配时清零模式双缓冲功能是禁止的。双缓冲可以将更新OCR0寄存器与top或bottom时刻同步起来,从而防止产生不对称的PWM脉冲,消除了干扰脉冲。

访问OCR0寄存器看起来很复杂,其实不然。使能双缓冲功能时,CPU访问的是OCR0缓冲寄存器;禁止双缓冲功能时CPU访问的则是OCR0本身。

使用注意事项:

1)强制输出。比较工作于非PWM模式时,可以通过对强制输出比较位FOC0写“1”的方式来产生比较匹配。强制比较匹配不会置位OCF0标志,也不会重载/清零定时器,但是OC0引脚将被更新,好像真的发生了比较匹配一样(COM0[1∶0]决定OC0A是置位、清零,还是“0”与“1”交替变化)。

图7-3 T/C0输出比较单元逻辑功能图

2)写TCNT0操作将阻止比较匹配。CPU对TCNT0寄存器的写操作会在下一个定时器时钟周期阻止比较匹配的发生,即使此时定时器已经停止了。这个特性可以用来将OCR0初始化为与TCNT0相同的数值而不触发中断。

3)使用输出比较单元。由于在任意模式下写TCNT0都将在下一个定时器时钟周期里阻止比较匹配,在使用输出比较时改变TCNT0就会有风险,不论T/C此时是否在运行。如果写入的TCNT0的数值等于OCR0,比较匹配就被丢失了,造成不正确的波形发生结果。类似地,在计数器进行降序计数时不要对TCNT0写入等于BOTTOM的数据。

OC0的设置应该在设置数据方向寄存器之前完成。最简单的设置OC0的方法是在普通模式下利用强制输出比较FOC0。即使在改变波形发生模式时OC0寄存器也会一直保持它的数值。

注意COM0[1∶0]和比较数据都不是双缓冲的。COM0[1∶0]的改变将立即生效。

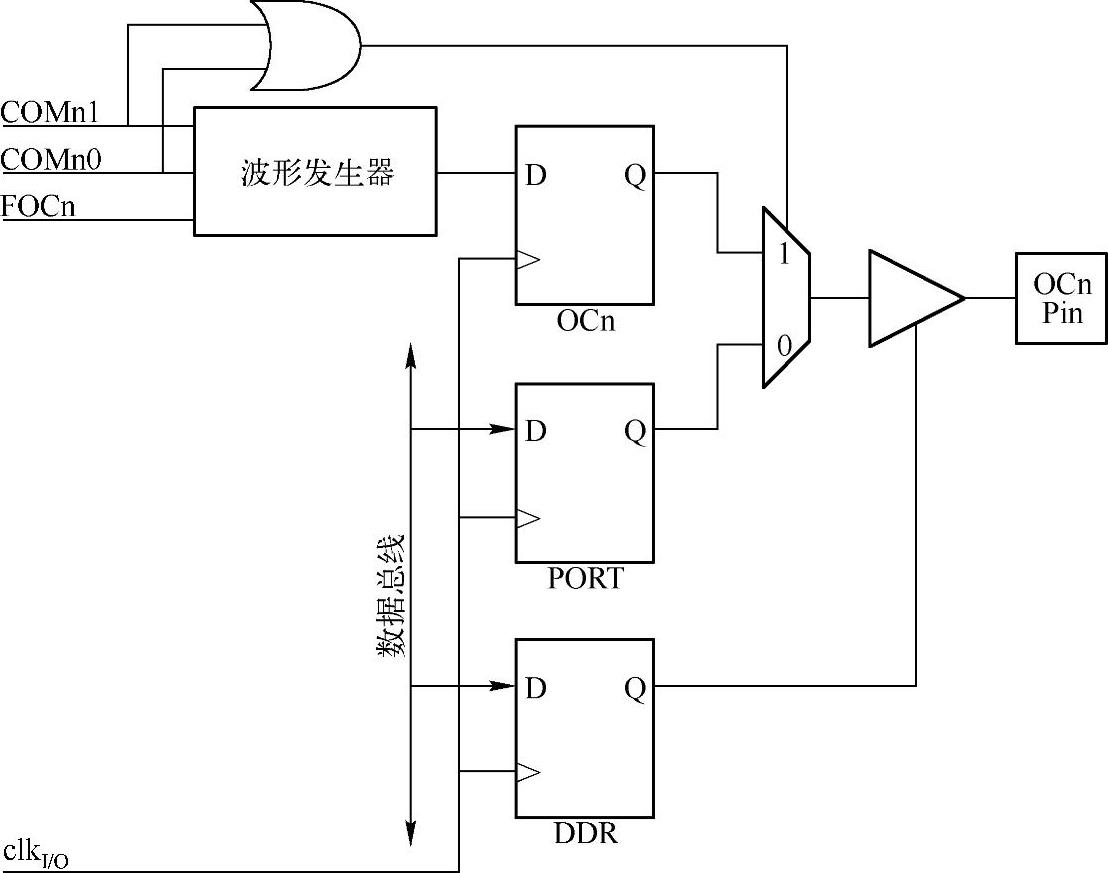

4)比较匹配输出单元。比较匹配模式控制位COM0[1∶0]具有双重功能。波形发生器利用COM0[1∶0]来确定下一次比较匹配发生时的输出比较状态(OC0);COM0[1∶0]还控制OC0引脚输出信号的来源。图7-4为受COM0[1∶0]设置影响的简化逻辑框图。I/O寄存器、I/O位和I/O引脚以粗体表示。图中只给出了受COM0[1∶0]影响的通用I/O端口控制寄存器(DDR和PORT)。当谈及OC0状态时指的是内部OC0寄存器,而不是OC0引脚。系统复位时OC0寄存器清零。

如果COM0[1∶0]不全为零,通用I/O口功能将被波形发生器的输出比较功能取代。但OC0引脚为输入还是输出仍然由数据方向寄存器DDR控制。在使用OC0功能之前首先要通过数据方向寄存器的DDR_OC0位将此引脚设置为输出。端口功能与波形发生器的工作模式无关。

图7-4 T/C0比较匹配输出单元逻辑图

输出比较逻辑的设计允许OC0状态在输出之前首先进行初始化。要注意某些COM0[1∶0]设置保留给了其他操作类型。

5)比较输出模式和波形产生。波形发生器利用COM0[1∶0]的方法在普通模式、CTC模式和PWM模式下有所区别。对于所有的模式,设置COM0[1∶0]=0表明比较匹配发生时波形发生器不会操作OC0寄存器。改变COM0[1∶0]将影响写入数据后的第一次比较匹配。对于非PWM模式,可以通过使用FOC0来立即产生效果。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。