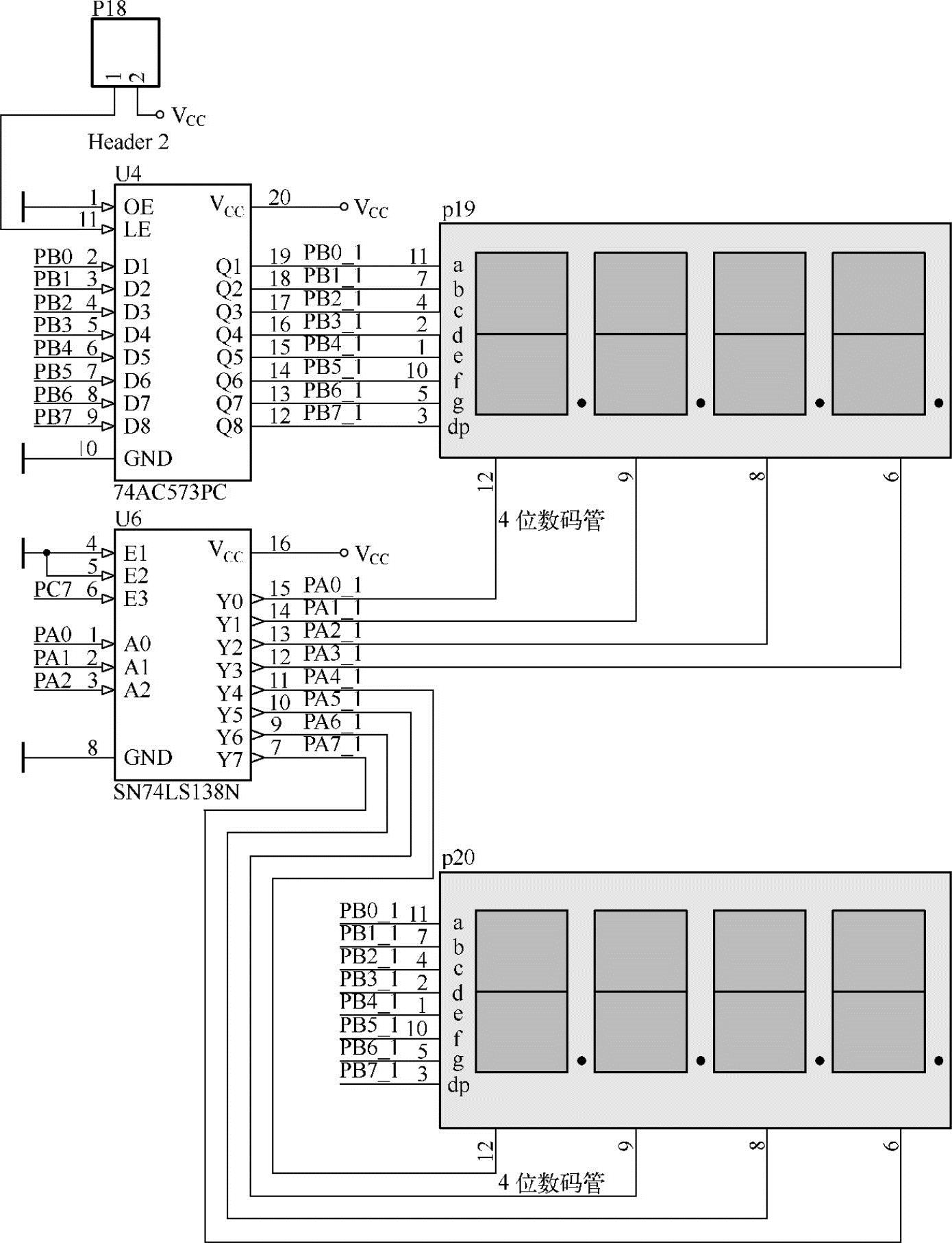

图6-11所示为ATmega16端口与两个4位数码管的连接图。本例中的数码管采用共阴型的数码管,显示方式采用动态扫描方式,并可配合按键控制输出的数据。

电路图中,单片机PB端口通过一个锁存器573驱动两个数码管的段码控制端,PA端口通过一个译码器138控制两个数码管的位码控制端。

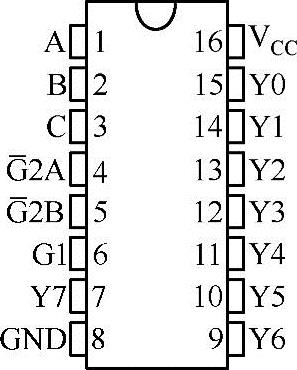

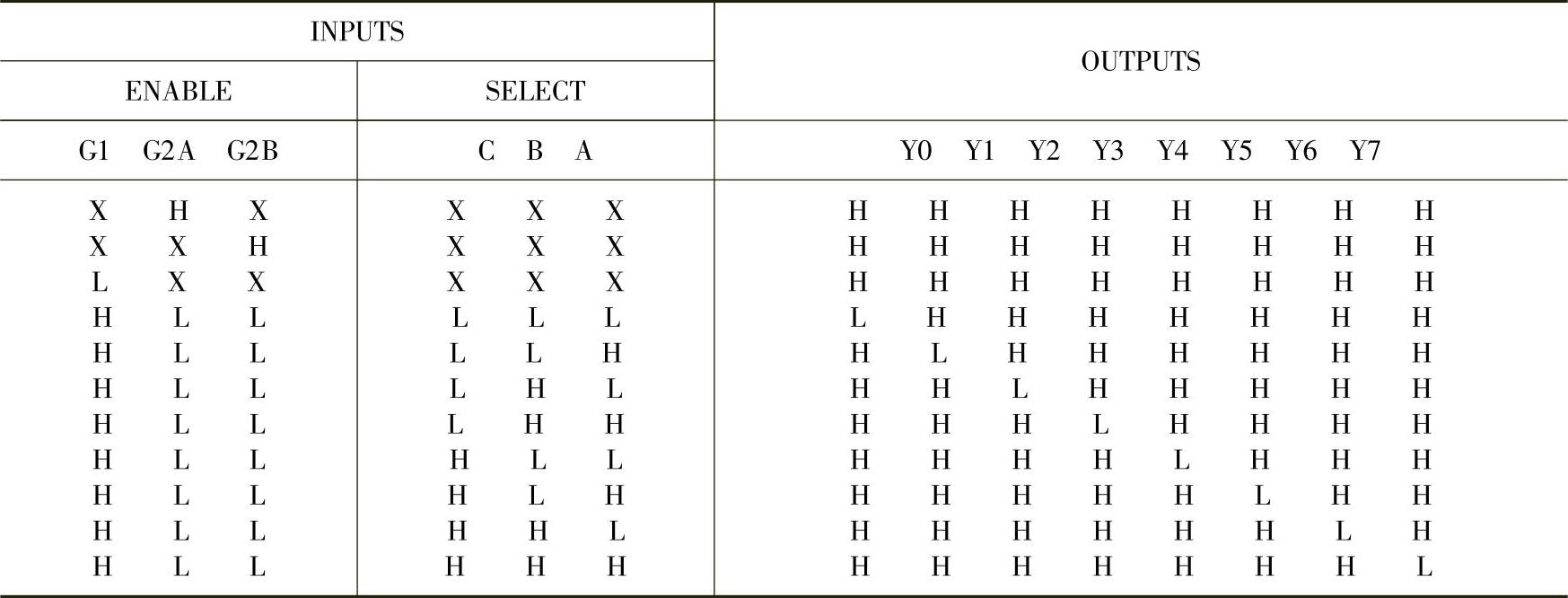

其中74LS138是常用的3/8译码器,即对3个输入信号进行译码,得到8个输出状态。A、B、C为数据允许输入端,G2A、G2B低电平有效。G1高电平有效。Y0~Y7为译码信号输出端。74LS138译码器封装图如图6-12所示,真值表如表6-4所示。读者在编程时可以参考该真值表。

图6-11 数码管实例原理图

图6-12 74LS138译码器封装图

表6-4 74LS138译码器真值表

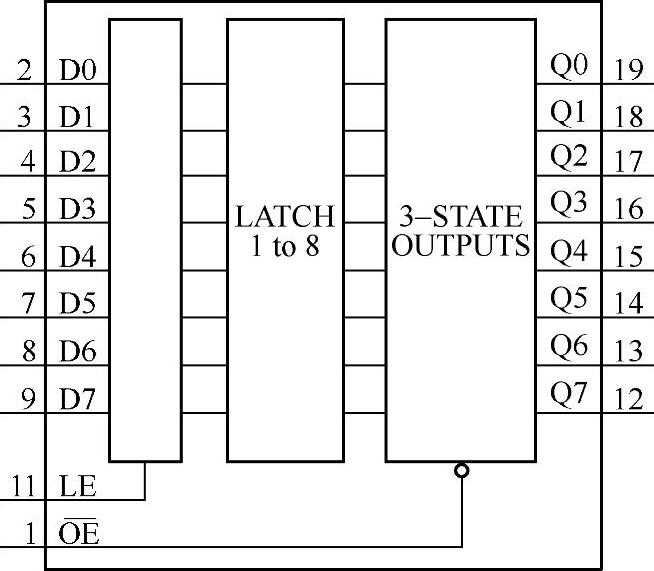

74HC573是一款高速CMOS器件,74HC573引脚兼容低功耗肖特基TTL(LSTTL)系列。74HC573包含八路D型透明锁存器,每个锁存器具有独立的D型输入,以及适用于面向总线的应用的三态输出。所有锁存器共用一个锁存使能(LE)端和一个输出使能(OE)端。其逻辑原理图如图6-13所示。当LE为高时,数据从Dn输入到锁存器,在此条件下,锁存器进入透明模式,也就是说,锁存器的输出状态将会随着对应的D输入每次的变化而改变。当LE为低时,锁存器将存储D输入上的信息一段就绪时间,直到LE的下降沿来临。

当OE为低时,8个锁存器的内容可被正常输出;当OE为高时,输出进入高阻态。OE端的操作不会影响锁存器的状态。

图6-13 74HC573逻辑原理图(https://www.xing528.com)

74HC573特性总结如下:

●输入输出分布在芯片封装的两侧,为微处理器提供简便的接口。

●用于微控制器和微型计算机的输入输出口。

●三态正相驱动输出,用于面向总线的应用。

●共用三态输出使能端。

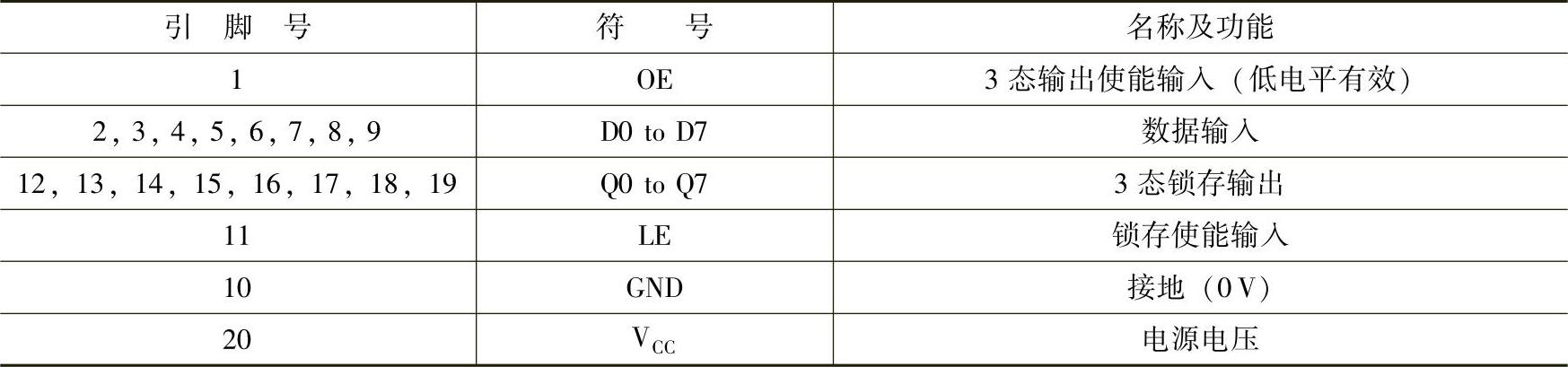

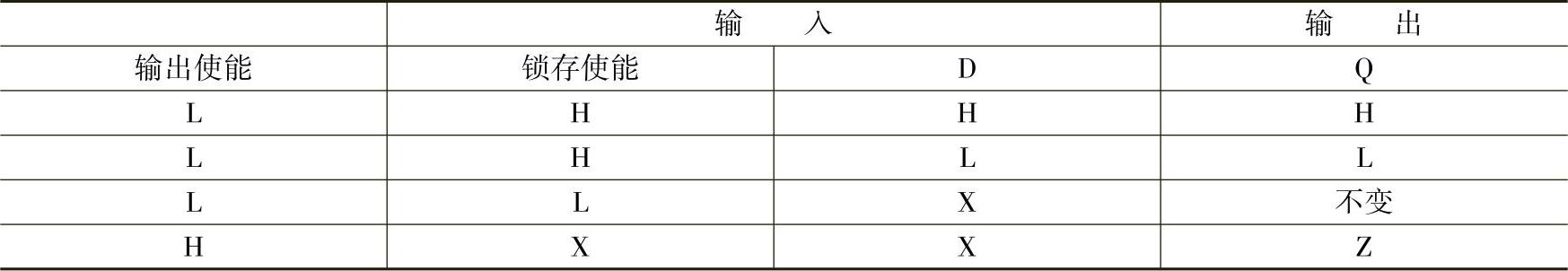

74HC573的引脚说明表如表6-5所示,真值表如表6-6所示,读者在阅读过程中,有关3/8译码器和锁存器中有不明白的地方,可参考本书附带光盘中的Datasheet。

表6-5 74HC573的引脚说明表

表6-6 74HC573的真值表

其中:X=不用关心Z=高阻抗

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。