图6-1为AVR单片机通用I/O口的基本结构示意图。每组I/O口均配备3个8位寄存器,它们分别是方向控制寄存器DDRx,数据寄存器PORTx,和输入引脚寄存器PINx(x=A/B/C/D)。I/O口的工作方式和表现特征由这3个I/O口寄存器控制。

方向控制寄存器DDRx用于控制I/O口的输入输出方向,即控制I/O口的工作方式为输出方式还是输入方式。

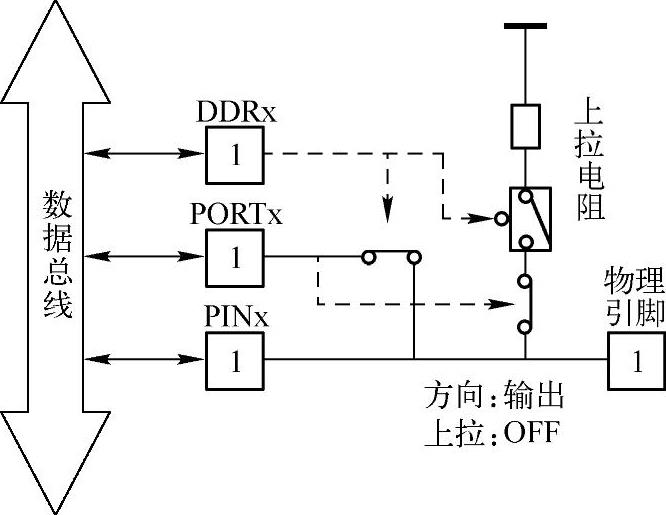

当DDRx=1时,I/O口为输出工作方式。此时数据寄存器PORTx中的数据通过一个推挽电路输出到外部引脚,如图6-2所示。AVR的输出采用推挽电路提高了I/O口的输出能力,当PORTx=1时,I/O引脚呈现高电平,同时可提供输出20mA的电流;而当PORTx=0时,I/O引脚呈现低电平,同时可吸纳20mA电流。因此,AVR的I/O在输出方式下提供了比较大的驱动能力,可以直接驱动LED等小功率外围器件。

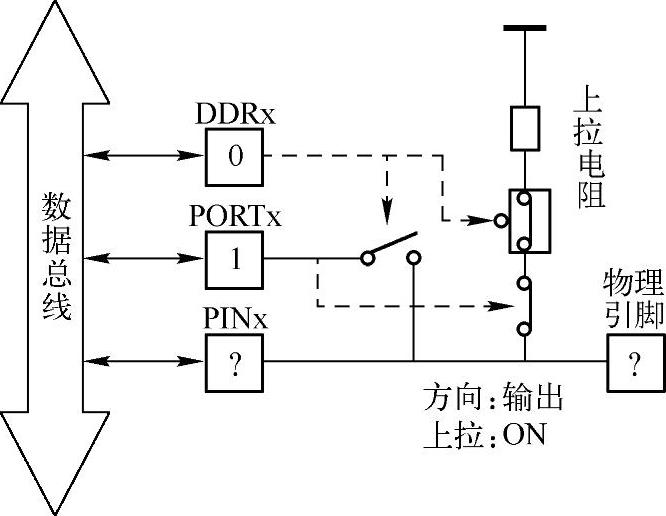

当DDRx=0时,I/O处于输入工作方式。此时引脚寄存器PINx中的数据就是外部引脚的实际电平,通过读I/O指令可将物理引脚的真实数据读入MCU。此外,当I/O口定义为输入时(DDRx=0),通过PORTx的控制,可使用或不使用内部的上拉电阻,如图6-3所示。

图6-2 通用I/O口输出工作方式示意图

图6-3 通用I/O口输入工作方式示意图(带内部上拉电阻)

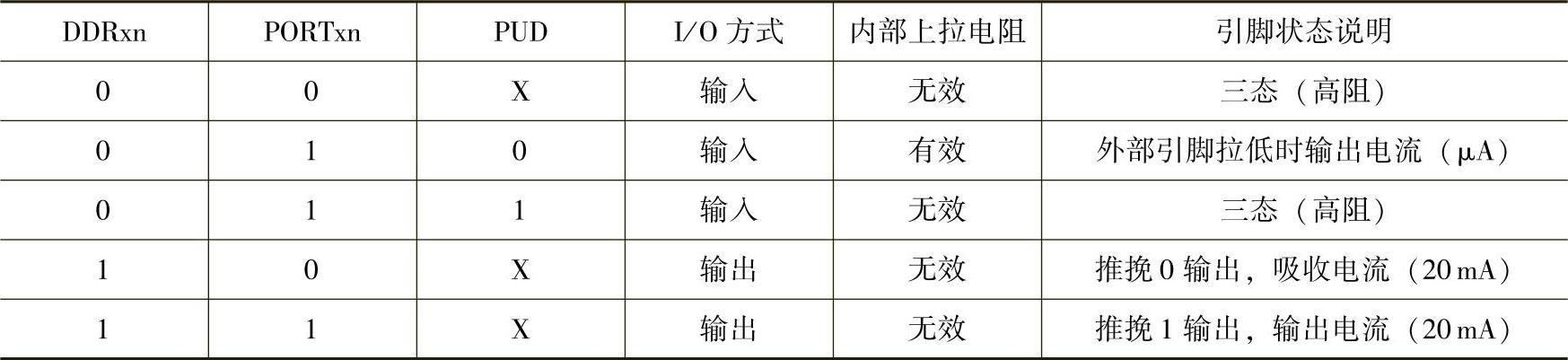

表6-1是AVR通用I/O端口的引脚配置情况。

表6-1 I/O口引脚配置表

表中的PUD为寄存器SFIOR中的一位,它的作用相当AVR全部I/O口内部上拉电阻的总开关。当PUD=1时,AVR所有I/O内部上拉电阻都不起作用(全局内部上拉电阻无效);而PUD=0时,各个I/O口内部上拉电阻取决于DDRXn的设置。

AVR通用I/O端口的主要特点如下:

(1)双向可独立位控的I/O口(https://www.xing528.com)

ATmega16的PA、PB、PC、PD四个端口都是8位双向I/O口,每一位引脚都可以单独的进行定义,相互不受影响。如用户可以在定义PA口第0、2、3、4、5、6位用于输入的同时定义第1、7位用于输出,互不影响。

(2)Push-Pull大电流驱动(最大40mA)

每个I/O口输出方式均采用推挽式缓冲器输出,提供大电流的驱动,可以输出(吸入)20mA的电流,因而能直接驱动LED显示器。

(3)可控制的引脚内部上拉电阻

每一位引脚内部都有独立的,可通过编程设置的,设定为上拉有效或无效的内部上拉电阻。当I/O口被用于输入状态,且内部上拉电阻被激活(有效)时,如果外部引脚被拉低,则构成电流源输出电流(μA量级)。

(4)DDRx可控的方向寄存器

AVR的I/O端口结构同其他类型单片机的明显区别是,AVR采用3个寄存器来控制I/O端口。一般单片机的I/O仅有数据寄存器和控制寄存器,而AVR还多了一个方向控制器,用于控制I/O的输入输出方向。由于输入寄存器PINx实际不是一个寄存器,而是一个可选通的三态缓冲器,外部引脚通过该三态缓冲器与MCU的内部总线连接,因此,读PINx时是读取外部引脚上的真实和实际逻辑值,实现了外部信号的同步输入。这种结构的I/O端口,具备了真正的读-修改-写(Read-Modify-Write)特性。

图6-1为AVR一个(位)通用I/O口的逻辑功能图。右上面的两个D触发器为方向控制寄存器和数据寄存器。

使用AVR的I/O口,首先要正确设置其工作方式,确定其工作在输出方式还是输入方式。

当I/O工作在输入方式,要读取外部引脚上的电平时,应读取PINxn的值,而不是PORTxn的值。

当I/O工作在输入方式,要根据实际情况使用或不使用内部的上拉电阻。

一旦将I/O口的工作方式由输出设置成输入方式后,必须等待一个时钟周期后才能正确地读到外部引脚PINxn的值。

上面的第4点是由于在PINxn和AVR内部数据总线之间有一个同步锁存器(图6-3中的SYNCHRONIZER)电路,使用该电路避免了当系统时钟变化的短时间内外部引脚电平也同时变化而造成的信号不稳定的现象,但它有产生大约一个时钟周期(0.5~1.5)的时延。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。