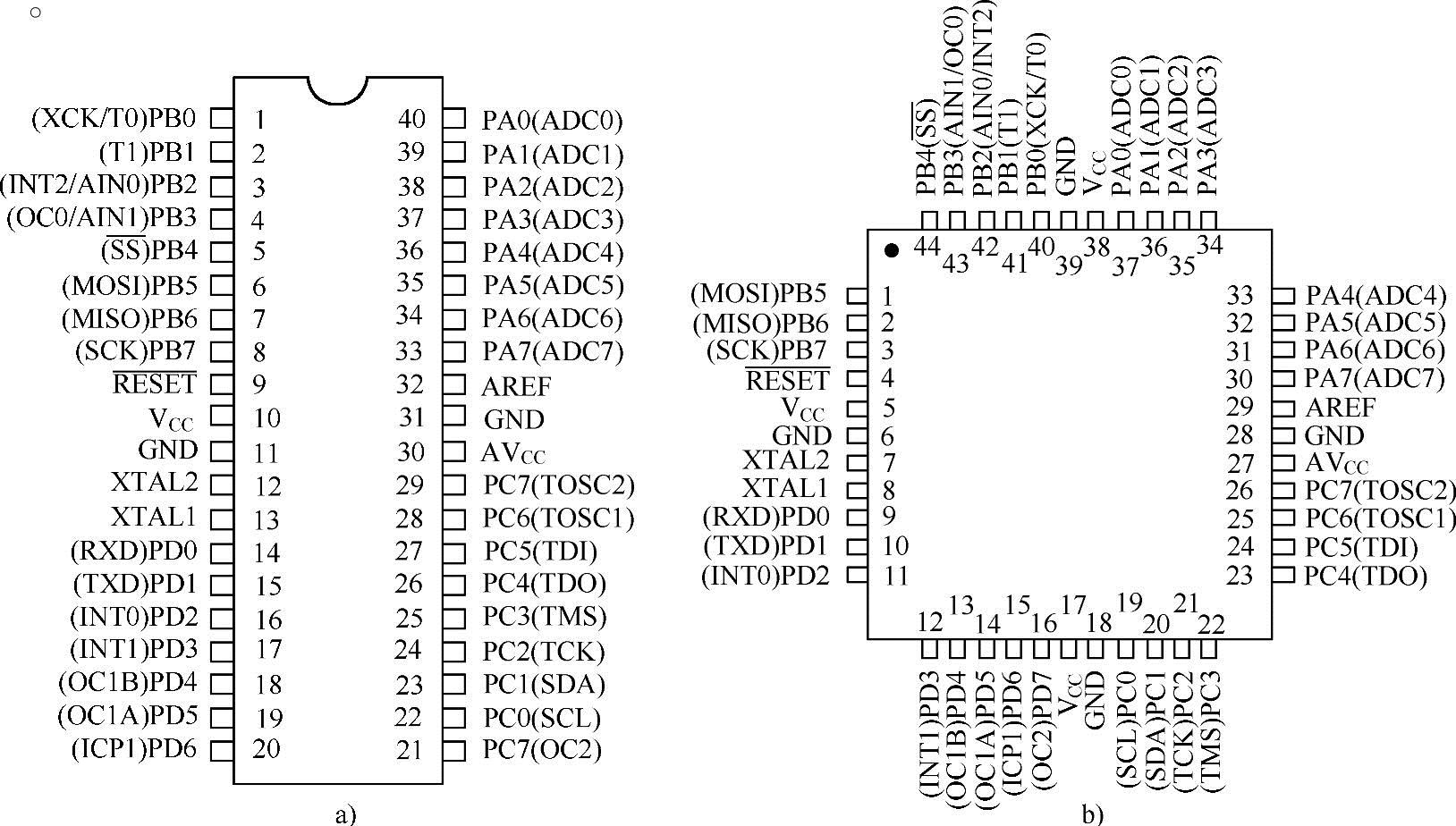

ATmega16单片机具有三种不同的封装形式:40引脚PDIP封装、44引脚TQFP封装与44引脚MLF封装。常用的是40引脚PDIP封装、44引脚TQFP封装,其外形封装如图1-7所示。引脚图如图1-8所示。

图1-7 ATmega16单片机封装图

a)PDIP-40封装 b)TQFP-44封装

图1-8 ATmega16单片机引脚图

a)PDIP-40封装 b)TQFP-44封装

下面以常用的PDIP(40引脚)封装来介绍ATmega16的引脚定义,其引脚排列分布如图1-8所示。

1.端口VCC

数字电路的电源。

2.端口GND

数字电路的地。

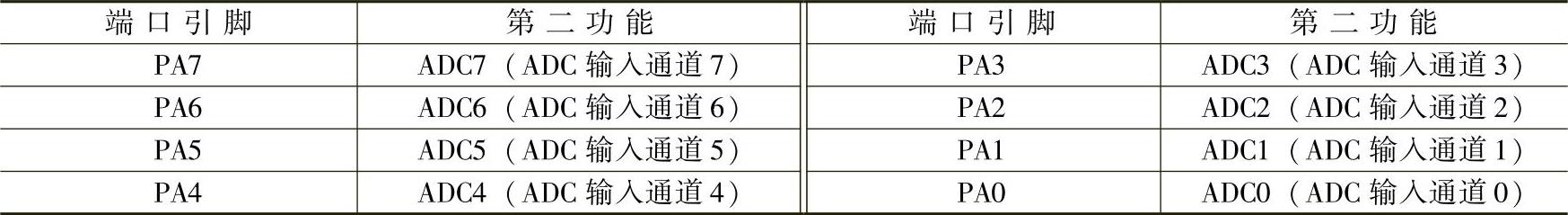

3.端口A(PA7..PA0)

端口A为8位双向I/O口,具有可编程的内部上拉电阻。其输出缓冲器具有对称的驱动特性,可以输出和吸收大电流。作为输入使用时,若内部上拉电阻使能,则端口被外部电路拉低时将输出电流。在复位过程中,即使系统时钟还未起振,端口A处于高阻状态,端口A可作为A/D转换器的模拟输入端,其第二功能如表1-1所示。

表1-1 端口A第二功能

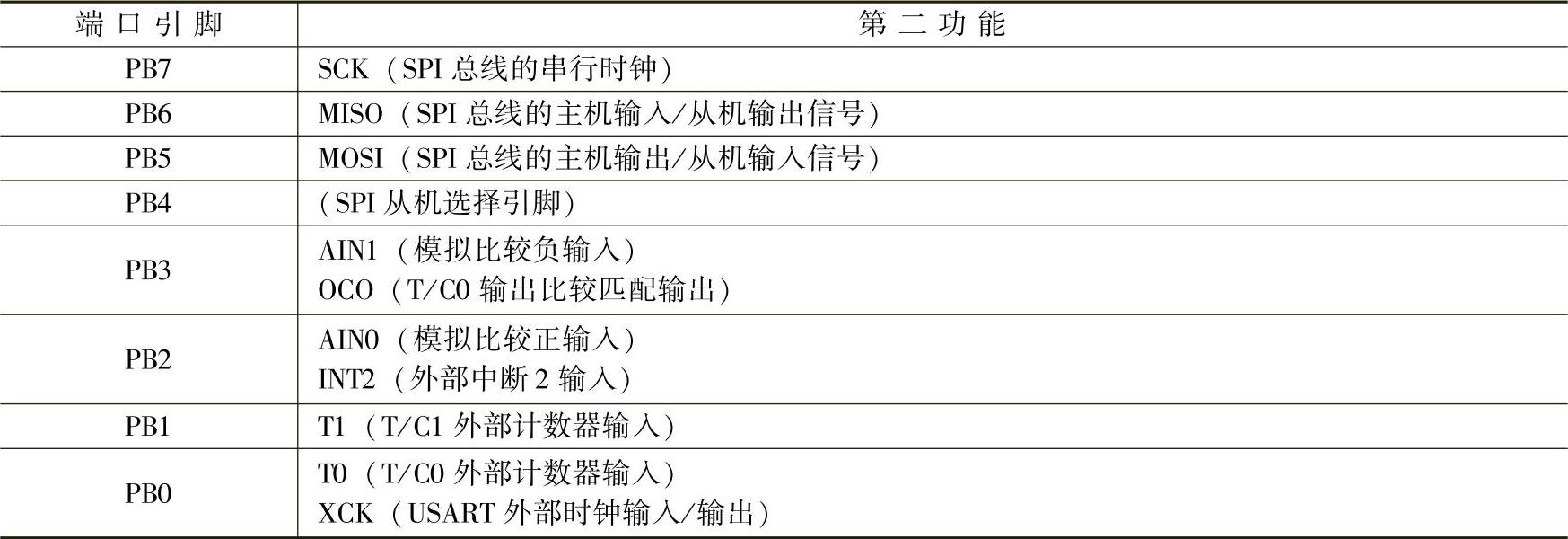

4.端口B(PB7..PB0)

端口B为8位双向I/O口,具有可编程的内部上拉电阻。其输出缓冲器具有对称的驱动特性,可以输出和吸收大电流。作为输入使用时,若内部上拉电阻使能,则端口被外部电路拉低时将输出电流。在复位过程中,即使系统时钟还未起振,端口B处于高阻状态,端口B也可以用做其他不同的特殊功能,端口B的第二功能如表1-2所示。

表1-2 端口B第二功能

5.端口C(PC7..PC0)(https://www.xing528.com)

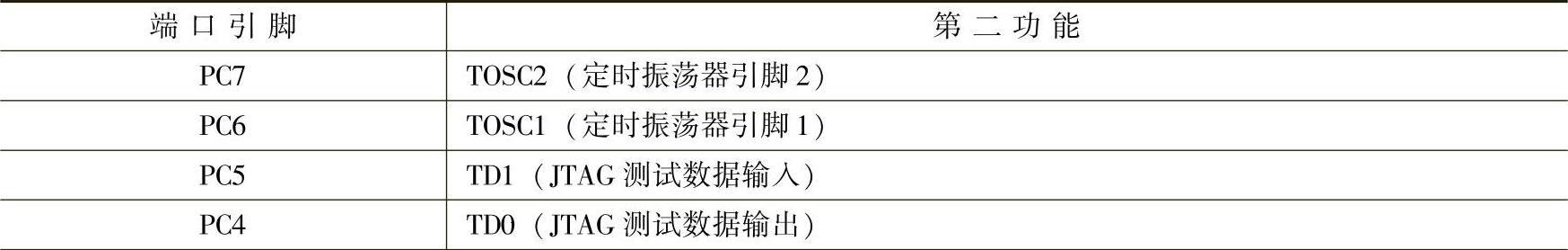

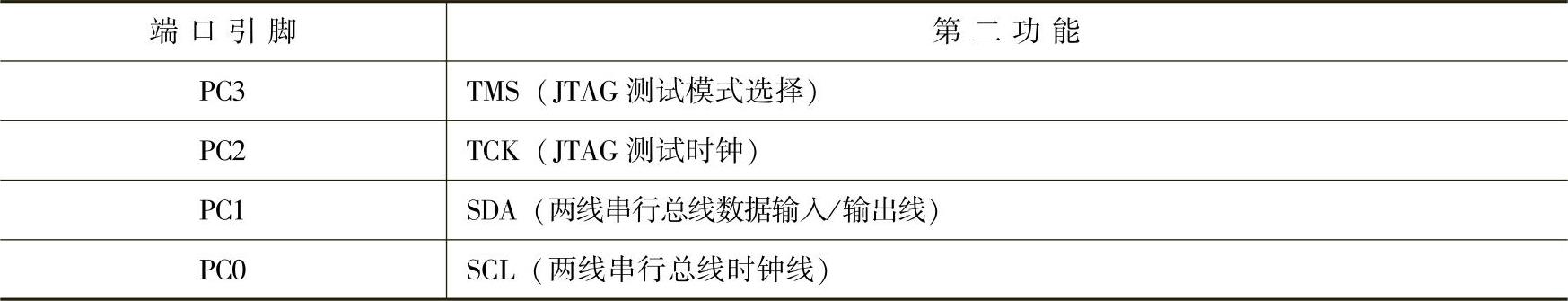

端口C为8位双向I/O口,具有可编程的内部上拉电阻。其输出缓冲器具有对称的驱动特性,可以输出和吸收大电流。作为输入使用时,若内部上拉电阻使能,则端口被外部电路拉低时将输出电流。在复位过程中,即使系统时钟还未起振,端口C处于高阻状态。如果JTAG接口使能,即使复位出现,引脚PC5(TDI)、PC3(TMS)与PC2(TCK)的上拉电阻被激活。端口C的第二功能如表1-3所示。

表1-3 端口C第二功能

(续)

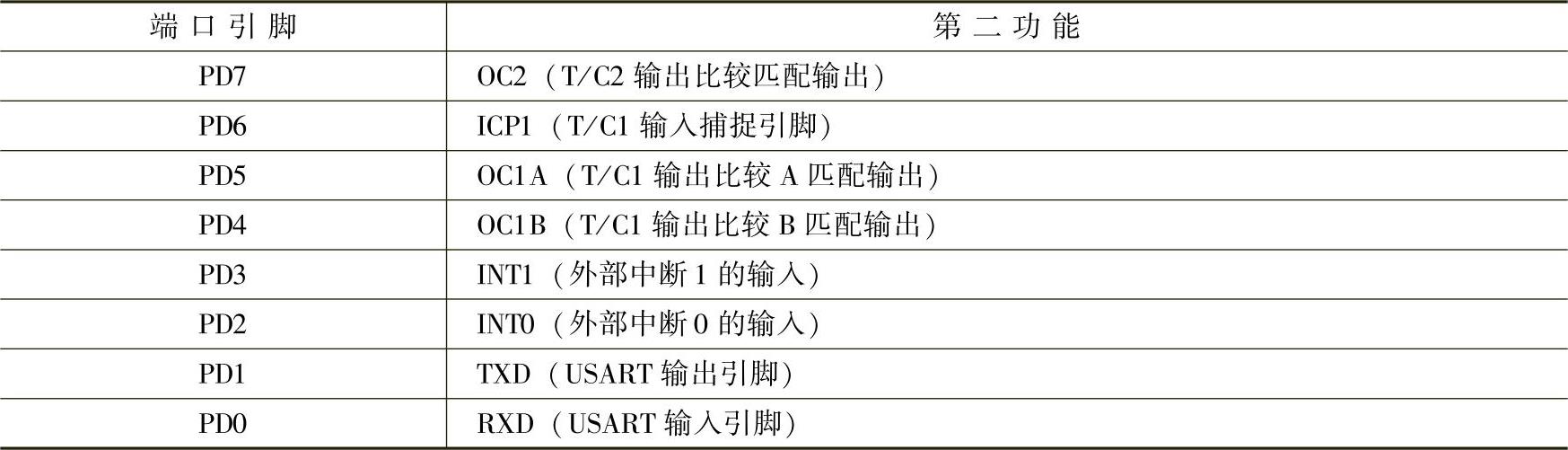

6.端口D(PD7..PD0)

端口D为8位双向I/O口,具有可编程的内部上拉电阻。其输出缓冲器具有对称的驱动特性,可以输出和吸收大电流。作为输入使用时,若内部上拉电阻无效,则端口被外部电路拉低时将输出电流。在复位过程中,即使系统时钟还未起振,端口D处于高阻状态,端口D也可以用做其他不同的特殊功能,端口D的第二功能如表1-4所示。

表1-4 端口D第二功能

7.端口RESET

复位输入引脚。持续时间超过最小门限时间的低电平将引起系统复位。持续时间小于门限间的脉冲不能保证可靠复位。

8.端口XTAL1

反向振荡放大器与片内时钟操作电路的输入端。

9.端口XTAL2

反向振荡放大器的输出端。

10.端口AVCC

AVCC是端口A与A/D转换器的电源。不使用ADC时,该引脚应直接与VCC连接。使用ADC时应通过一个低通滤波器与VCC连接。

11.端口AREF

A/D的模拟基准输入引脚。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。