用户对单片机中断系统的操作是通过控制相关寄存器来实现的。MCS-51的中断系统从面向用户的角度来看,有以下4个特殊功能寄存器:

(1)定时器控制寄存器TCON;

(2)串行口控制寄存器SCON;

(3)中断允许寄存器IE;

(4)中断优先级寄存器IP。

其中TCON和SCON只有一部分位用于中断控制。通过对以上各特殊功能寄存器的有关位进行置位(置1)或复位(清0)等操作,可实现各种中断控制功能。

1.中断请求标志

(1)定时/计数器控制寄存器TCON中的中断标志位。

TCON为定时计数器T0、T1的控制寄存器,同时也锁存了T0、T1的溢出中断源和外部中断请求源等,字节地址为88H。与中断有关的位如下:

各控制位的含义如下:

IE0:外部中断0标志位,若IE0=1,则表示外部中断0![]() 向CPU提出了请求中断。

向CPU提出了请求中断。

IT0:外部中断0触发方式控制位。当IT0=0,外部中断0![]() 控制为电平触发方式。在这种方式下,CPU在每个机器周期的S5P2期间采样

控制为电平触发方式。在这种方式下,CPU在每个机器周期的S5P2期间采样![]() (P3.2)的输入电平,若采到低电平,则认为有中断请求,随即由硬件置IE0=1。若采到高电平,则认为无中断请求或中断请求已撤除,随即对IE0清0。在电平触发方式中,CPU响应中断后不能自动使IE0清0,也不能由软件使IE0清0,故在中断返回前必须清除

(P3.2)的输入电平,若采到低电平,则认为有中断请求,随即由硬件置IE0=1。若采到高电平,则认为无中断请求或中断请求已撤除,随即对IE0清0。在电平触发方式中,CPU响应中断后不能自动使IE0清0,也不能由软件使IE0清0,故在中断返回前必须清除![]() 引脚上的低电平,否则会再次响应中断造成出错。

引脚上的低电平,否则会再次响应中断造成出错。

当IT0=1,外部中断0![]() 控制为边沿触发方式,CPU在每个机器周期的S5P2期间采样

控制为边沿触发方式,CPU在每个机器周期的S5P2期间采样![]() 的输入电平,相继两次采样,若一个周期采样为高电平,接着的下一个周期采样为低电平,则由硬件置IE0=1,表示外部中断0

的输入电平,相继两次采样,若一个周期采样为高电平,接着的下一个周期采样为低电平,则由硬件置IE0=1,表示外部中断0![]() 正在向CPU请求中断,直到该中断被CPU响应时,IE0由硬件自动清0,在边沿触发方式中,为了保证CPU在两个机器周期内检测到先高后低的负跳变,输入高低电平的持续时间起码要保持1个机器周期。

正在向CPU请求中断,直到该中断被CPU响应时,IE0由硬件自动清0,在边沿触发方式中,为了保证CPU在两个机器周期内检测到先高后低的负跳变,输入高低电平的持续时间起码要保持1个机器周期。

触发方式的比较:

电平触发方式时,外部中断源的有效低电平必须保持到请求获得响应时为止,不然就会漏掉;在中断服务结束之前,中断源的有效低电平必须撤除,否则中断返回之后将再次产生中断。该方式适合于外部中断输入为低电平,且在中断服务程序中能清除外部中断请求源的情况。

边沿触发方式时,在相继两次采样中,先采样到外部中断输入为高电平,下一个周期采样到为低电平,则在IE0或IE1中锁存一个逻辑1。若CPU暂时不能响应此中断请求,中断申请标志也不会丢失,直到CPU响应此中断时才清0。边沿触发方式适合于以负脉冲形式输出的外部中断请求。

IE1:外部中断1标志位,功能与IE0类似。

IT1:外部中断1触发方式控制位,功能与IT0类似。

TF0:定时/计数器T0溢出中断标志,在启动定时/计数器后,T0从初值开始加1计数,当计满溢出时,由硬件置TF0=1,向CPU请求中断,CPU响应TF0中断后,由硬件对TF0清0,TF0也可由软件(指令)清0。

TF1:T1溢出中断标志,功能与TF0类似。

当MCS-51系统复位后,TCON各位均清0。

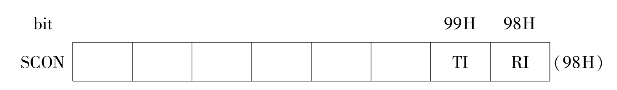

(2)串行口控制寄存器SCON中的中断标志位。

SCON为串行口控制寄存器,字节地址为98H,SCON的低2位TI和RI锁存串行口的接收中断和发送中断标志。其格式如下:

TI:串行口发送中断标志。CPU将8位数据写入发送缓冲器SBUF时,就启动发送,每发送完一帧串行数据后,由硬件置TI=1,向CPU提出中断请求,CPU响应中断时,不会对TI清0,必须由软件(指令)清0。(https://www.xing528.com)

RI:串行口接收中断标志。若串行口接收器允许接收,每接收完一串行帧,硬件置RI=1。RI=1表示串行口接收器正在向CPU请求中断。同样CPU响应中断时不会对RI清0,必须由软件(指令)清0。

2.中断允许控制

中断源中断请求的开放与禁止是由中断允许寄存器IE中的相应位进行控制的,IE的字节地址为A8H。其格式如下:

EA:CPU的中断开放标志。EA=1,CPU开放中断;EA=0,CPU禁止(屏蔽)所有的中断请求。

ES:串行口的中断允许位。ES=1,允许串行口中断;ES=0,禁止串行口中断。

ET1:定时/计数器T1的溢出中断允许位。ET1=1,允许T1中断;ET1=0,禁止T1中断。

EX1:外部中断1![]() 的中断允许位。EX1=1,允许外部中断1中断;EX1=0,禁止外部中断1中断。

的中断允许位。EX1=1,允许外部中断1中断;EX1=0,禁止外部中断1中断。

ET0:定时/计数器T0的溢出中断允许位。ET0=1,允许T0中断,ET0=0,禁止T0中断。

EX0:外部中断0![]() 的中断允许位,EX0=1,允许外部中断0中断;EX0=0,禁止外部中断0中断。

的中断允许位,EX0=1,允许外部中断0中断;EX0=0,禁止外部中断0中断。

MCS-51单片机系统复位后,IE中各位均被清0,即禁止所有中断。

3.中断优先级控制

MCS-51单片机有两个中断优先级,对于每一个中断源的中断请求可编程为高优先级中断或低优先级中断,可实现二级中断嵌套。一个正在执行的低优先级中断能被高优先级中断请求所中断,但不能被另一个同优先级的中断请求所中断,一直执行到结束,遇到中断返回指令RETI后返回主程序后再执行一条指令才能响应新的中断请求。

MCS-51单片机内有一个优先级寄存器IP,字节地址为B8H,用指令改变其内容,就可对各中断源的中断优先级别进行设置。其格式如下:

PS:串行口中断优先级控制位。PS=1,串行口中断设置为高优先级中断;PS=0,设置为低优先级中断。

PT1:T1中断优先级控制位。PT1=1,定时/计数器T1设置为高优先级中断;PT1=0,设置为低优先级中断。

PX1:外部中断1中断优先级控制位。PX1=1外部中断1设置为高优先级中断;PX1=0,设置为低优先级中断。

PT0:T0中断优先级控制位。PT0=1,定时/计数器T0设置为高优先级中断;PT0=0,设置为低优先级中断。

PX0:外部中断0中断优先级控制位。PX0=1外部中断0设置为高优先级中断;PX0=0,设置为低优先级中断。

MCS-51单片机系统复位后,IP各位均为0,各中断源均设定为低优先级中断。

MCS-51单片机的中断系统有两个不可寻址的“优先级有效”触发器。其中一个指示某高优先级的中断正在执行,所有后来的中断请求都被阻止。另一个触发器指示某低优先级的中断正在执行,所有的同级中断请求都被阻止,但不阻止高优先级的中断请求。

若同时收到几个同一优先级的中断请求时,哪一个先得到服务,取决于中断系统内部的查询顺序。这相当于在每个优先级内,还同时存在另一个辅助优先级结构。MCS-51单片机中各中断源的优先顺序以及对应的入口地址见表5.1。

表5.1 中断优先顺序及对应入口地址表

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。