信号完整性(Signal Integrity,SI)指的是信号线上的信号质量。信号完整性问题主要包括时延、阻抗不匹配及串扰。这些问题不是由单一因素造成的,而是由板级设计中多种因素共同引起的。破坏信号完整性的原因包括反射、振铃、地弹、串扰等。随着信号工作频率的不断提高,信号完整性问题已经成为高速印制电路板上十分重要和突出的问题,成为工程师关注的焦点。

1.信号时延

信号时延是指信号从驱动器间的输出引脚经过印制导线到达接收端的衰减。其大小为

式中,c为真空中的光速;εreff为有效的相介电常数;lp为信号线长度。

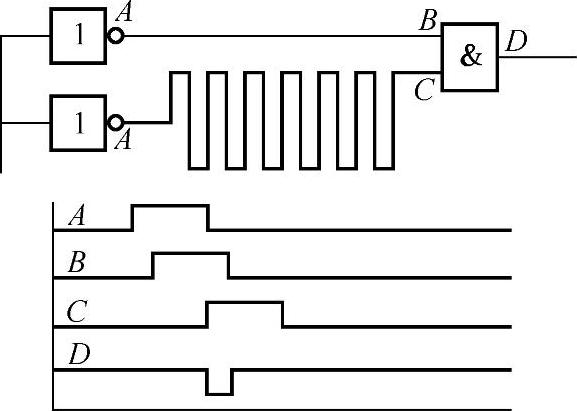

εreff与传输线周围介质有关,对于微带传输线来说,介于板的相对介电常数与空气相对介电常数之间。在大多数系统中,信号传输线长度是影响时钟脉冲相位差的最直接因素。时钟脉冲相位差是指同时产生的两个时钟信号,到达接收端的时间不同步。时钟脉冲相位差降低了信号沿到达的可预测性,如果时钟脉冲相位差太大,会在接收端产生错误的信号。传输线时延对信号的影响如图5-24所示。信号时延的时间已经成为影响时钟脉冲周期的重要部分。

图5-24 传输线时延对信号的影响

2.阻抗不匹配

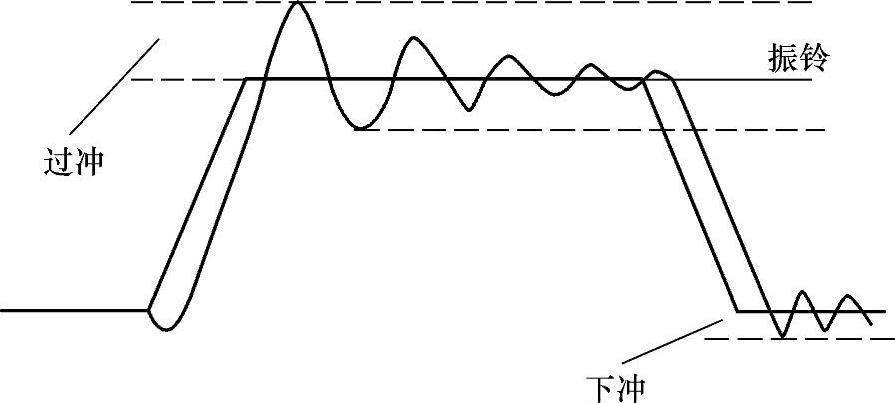

阻抗不匹配是信号线负载或信号源阻抗与信号线的特性阻抗不相等。特性阻抗与信号线的宽度、地线层的距离及板材的介电常数等因素有关,是信号线的固有特性。阻抗不匹配的主要原因是信号在走线过程中自身特性阻抗发生了变化,如走线的宽窄不同、走线扭弯、经过过孔等。阻抗不连续导致反射和阻尼振荡,当源端与负载端阻抗不匹配时,负载将一部分电压反射回源端。如果负载阻抗小于源阻抗,反射电压为负;如果负载阻抗大于源阻抗,反射电压为正。反射回来的信号还会在源端再次形成反射,从而形成振荡。而反射会引起信号的振铃现象,即产生相对理想的稳态信号电压过冲和下冲现象,如图5-25所示。为了将电压的过冲/下冲限制在合理的范围内(不超出稳态值的10%~15%),应该遵循下面的原则:信号的上升时间要小于信号在印制板导线上来回引起的传输时延,这样允许的信号传输线的最大长度(m)为

式中,tr为信号的上升时间(ns);v为电磁波在印制电路板导线上的传输速度,v=(1.4~2)×10-9m/s;k为经验常数,一般取k=4~5。

图5-25 反射引起的振铃现象

由于存在传输线效应,从反射的角度来看,会出现以下信号完整性问题:

(1)信号反射形成信号振荡 反射回来的信号会在源端和终端之间形成多次反射,加上传输线效应引起的过大的电感和电容,会导致信号振荡,即在一个逻辑电平附近上下振荡。这种现象尤其会出现在周期性的时钟信号上,从而导致系统失败。

(2)信号反射会形成信号过冲和下冲 虽然一般来说每个信号的输入端都具有保护作用的齐纳二极管,但过冲电平有时会远远超过元器件电源电压范围,损坏元器件。(https://www.xing528.com)

(3)多次跨越逻辑电平门限 信号在跳变的过程中可能多次跨越逻辑电平门限,它是信号振荡的一种特殊的形式,即信号的振荡发生在逻辑电平门限附近,多次跨越逻辑电平门限会导致逻辑功能紊乱。

要消除反射现象,首先在布线时应注意少使用过长的信号线,同时减少过孔的数量。在走线拐角处进行圆弧处理或者以135°角度的导线连接。另外从传输线理论可知,当传输线的波阻抗与负载阻抗匹配时,电路的终端无反射。由于大多数终端的负载阻抗极大,因此也可能通过采用降低终端负载阻抗、控制传输线长度的方法来减少反射。

3.串扰

在高速信号系统设计中,反射属于单信号线现象,当然包括地平面问题。但串扰不同,它是两条信号线之间以及地平面之间的耦合,所以又称为三线系统。形成串扰的根本原因是信号变化引起周边的电磁场发生变化,特别是对于高速信号,信号的上升和下降沿的时间可以达到皮秒级,高频分量非常丰富,信号线之间的寄生电容和电感容易成为串扰信号的耦合通道。

传输线上分布着电感分量和电容分量,所以整个信号之间的串扰由两部分组成,即容性耦合干扰和感性耦合干扰。容性耦合干扰是由于骚扰源(Aggressor)上的电压变化在被干扰对象(Victim)上引起感应电流从而导致的电磁干扰,两条存在较长接近段的导线是容性耦合的一个典型例子。而感性耦合干扰则是由于骚扰源上的电流变化产生的磁场在被干扰对象上引起感应电压从而导致的电磁干扰。这是两个回路之间的关系,如同变压器的一次绕组和二次绕组。

串扰的大小与很多因素有关,如信号的速率、信号的上升沿和下降沿的速率、印制电路板层的参数、信号线平行长度和间距、驱动端和接收端的电气特性及线端接方式等。

当串扰信号线之间的平行长度增加时,将增加两传输线之间重叠的面积,所以线之间的耦合电容也会增加,从而增大电流串扰。同理,当传输线之间的间距减少时,两个耦合的传输线之间的耦合电容也会增加,从而增加串扰的数值。在高速电路设计中,重要的是减少串扰的数值,这样就要从结构上减小平行的长度,而且线间的间距也不能太小。

在串扰效应中,除了信号本身的传输频率外,影响很大的还有信号上升时间和下降时间,边沿变化越快,串扰越大。在现代设计中,经常会出现几百兆赫兹的时钟信号和数字信号,这样信号的上升沿可以达到皮秒级。在这种情况下,信号的上升时间和下降时间对串扰的影响是不可忽视的。

通常解决串扰的方法主要从减少骚扰源强度和切断干扰路径两个方面进行,有以下几个方法:

1)串扰与信号频率成正比,而且在数字电路中,信号的边沿变化(上升沿和下降沿)对串扰的影响最大,边沿变化越快变频分量越丰富,串扰越大,所以应尽量少地使用dU/dt高的信号,在超高速设计中可以使用低电压差分信号或其他差分信号。

2)在布线空间允许的条件下,在串扰较严重的两条线之间插入一条地线或地平面,可以起到隔离的作用,从而减小串扰。

3)加大线间距,减小线的平行长度,必须时可以采用凹凸(jog)方式布线。

4)对于信号速率比较高的信号,可以将它走线经过的微带线和带状线控制在地平面8mil(1mil=25.4×10-6m)距离内,这样可以显著减少串扰。

5)控制传输线阻抗,减小负载阻抗,加入端接匹配电阻以减小或消除反射,从而减小串扰。

6)感性耦合较难控制,要尽量减少回路数量,减小回路面积,不让信号回路共用一段导线。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。