在PCB电路板中,电磁能通常存在两种形式,差模EMI和共模EMI。电路中器件输出的电流流入一个负载时,就会产生差模EMI。差模辐射的特点取决于闭合环路中的电流特性。电流流经多个导电平面,如PCB上的导线组或电缆,就会产生共模辐射。

共模辐射是由于接地电路中存在电压降,某些部分具有高电位的共模电压,当外接电缆与这些部位连接时,就会产生共模电流,成为辐射电场的天线。这多数是由于接地系统是存在电压降所造成的。共模辐射通常决定了产品的辐射性能。

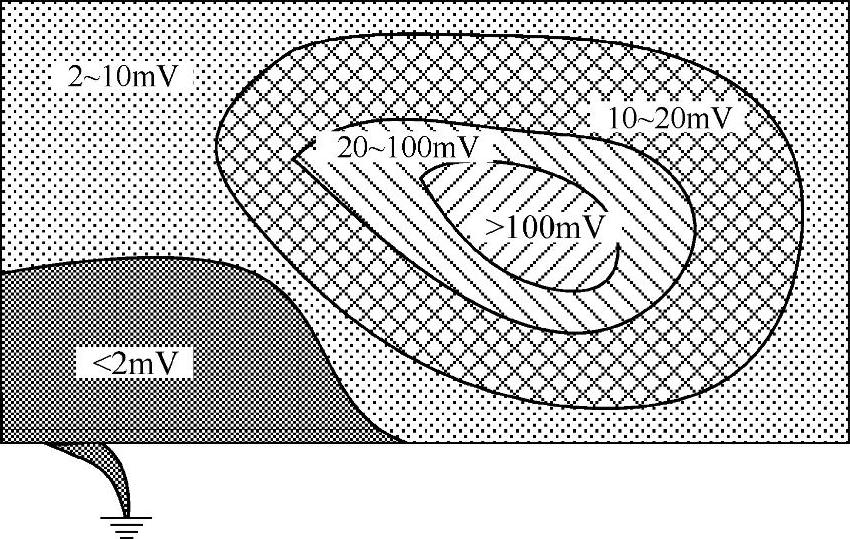

图4-23所示为典型的地电位分布图。

图4-23 地电位分布图

共模辐射主要从电缆上辐射,可用对地电压激励的、长度小于1/4波长的短单极天线来模拟。对于接地平面上长度为L的短单极天线来说,在距离r处辐射场的电磁强度为

E=4π×10-7(f·I·L)(1/r)sinθ (4-30)

式中,E为电磁强度(V/m);f为共模电流频率(Hz);I为共模电流(A);L为电缆长度(m);r为测量天线到电缆的距离(m);θ为测量天线与电缆的夹角(°)。(https://www.xing528.com)

式(4-30)表明,E与f、I和L成正比,因此减小它们的值可以减小辐射。减小共模辐射的方法为

1)尽量减小激励天线的源电压,即地电压。

2)提供与电缆串联的高共模阻抗,即加共模扼流圈。

3)将共模电流旁路到地。

4)电缆屏蔽层与屏蔽壳体作360°端接。

这里,采用接地平面就能有效地减小接地系统中的地电位,为了将共模电流旁路到地,可以在靠近连接处,把PCB的接地平面分割出一块,作为“无噪声”的输入/输出地。为了避免输入/输出地受到污染,只允许输入/输出的去耦电容和外部电缆的屏蔽层与“无噪声”地相连,去耦环路的电感应尽量减小。这样,输入/输出线所携带的PCB的共模电流就被去耦电容旁路到地了,外部骚扰在还未到达元件区域时就被去耦电容旁路到地去,从而保护内部元器件的正常工作。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。