一、数字信号的特性

在讨论各种基本的门电路之前,先介绍一下数字集成电路中数字信号的特性。

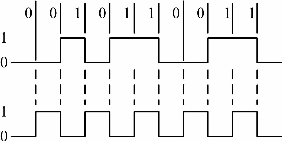

数字电路所要处理的信息是逻辑变量,它有0和1两种状态。当输入或输出电平为低即为V L时,对应于0逻辑状态,当电平为高即为V H时,则对应于1逻辑状态。理想的数字信号波形示于图5-1。

图5-1 理想的数字信号波形

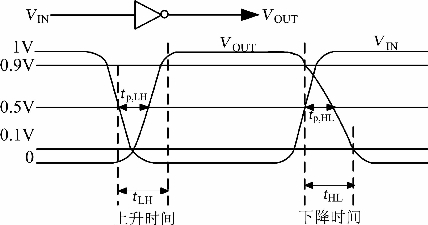

但实际上,在数字电路中的波形都存在一个上升过程和下降过程,而且对于所有的电路,当输入电压发生变化时,输出电压总是需要一段时间后才会响应。图5-2表示了反相器的逻辑符号、输入电压和输出电压的波形。从图中可以看出,当输入电压从高电平变化到低电平时,输出电平要经过一个上升时间才能达到稳定的高电平;同样,当输入从低电平变化到高电平时,输出电平要经过一个下降时间才能达到稳定的低电平。我们把电平从稳定状态高电平时的10%转变到高电平90%所需的时间定义为上升时间t LH;反之把电平从高电平的90%转变到高电平的10%时所需的时间定义为下降时间t HL。

另外一个重要参数称为传播延迟t P,它被定义为当输入电平和输出电平各达到总电平的50%时两者之间的时间差。对于输出电平的上升阶段,传播延迟t p记为t p,LH,对于输出电平的下降阶段,t p记为t p,HL。通常上升边的参数与下降边的不相等。

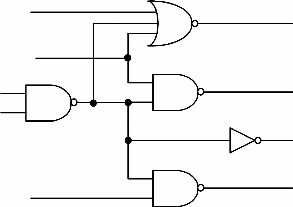

另一个影响电路响应时间的重要因素是电路的负载情况。通常一个门电路的输出连接下一个门电路的输入,如图5-3所示。我们把连接有多少个下一级的输入端数目称为扇出数F(fan-out)。当F增加时,门电路的负载就加重,因而造成响应时间加长。

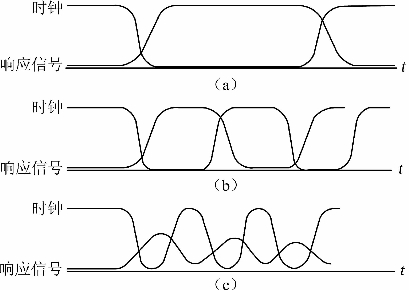

在数字电路中常有一时钟信号来控制各个门电路的工作。一般希望电路的工作频率越高越好,但是当工作频率增大到一定时,必须考虑各个门电路是否有足够的时间完成响应。如果来不及响应,就会导致信息传播过程中发生错误。

图5-2 一个反相器的输入和输出波形

如图5-4所示,当时钟频率较低时,电路能安全可靠地运行。当时钟频率接近于最大工作频率时,信号仍能正常地作出响应,即信号仍能达到规定的高电平和低电平。但当时钟频率超过最大工作频率时,响应信号就发生畸变,即响应信号在未达到规定的高电平时就开始下降,而下降时也不能达到规定的低电平。

图5-3 门电路的输出连接状况

二、电路的主要性能(https://www.xing528.com)

电路的性能包括很多方面,但最重要的是速度、功耗和所占硅片的面积。

1.速度速度是指电路能够可靠工作时的最大频率。一个反相器的最大工作频率可近似表达为电路的速度越高,则电路在每秒内可以处理的数据量就越大。

![]()

图5-4 随着时钟频率的增加,响应信号的变化情况

a-可安全可靠地运行;b-接近于最大时钟频率;c-超过最大时钟频率

一个数字电路中会有成千上万个电路单元,而每个电路单元由于其功能和设计的不同,它们的响应时间会有差异,因此最高时钟频率取决于响应最慢的电路单元或者最慢的通路(path)。

在电路设计中,最重要的任务之一是找出哪一个单元或者哪一条通路的响应时间最长,并且设法缩短它的响应时间以提高整个电路的工作速度。

2.功耗

所有的电路都需要由直流电源供电,从电源中获得的能量在电路中将以热的形式耗散掉。由于硅材料的性质决定了晶体管的性能会随温度有明显的变化,因而通常电路的PN结温度不能超过200℃(一般商用电路,其最高工作温度规定为65℃或75℃),这样就对电路的总功耗有一限制。

电路的功耗有两种成分,一种是静态功耗,另一种是动态功耗。静态功耗取决于电路处于稳定的逻辑状态时的电流,动态功耗则取决于在逻辑状态发生变化的过程中额外的那部分交流电流。

由于电路中器件数目增加时,电路的功耗会随着加大,因此对于集成度大的电路,电路中每一器件的功耗必须设法设计得越小越好。

3.芯片面积

电路的物理版图尺寸将决定芯片面积的大小。芯片尺寸不仅影响成本,还会受到管壳容积的限制,因此应尽可能采用最小的工艺尺寸来减小芯片面积。但是我们从下面的讨论中可以看到,电路单元的物理尺寸还取决于电路设计方法。

一般来讲,要同时做到速度快、功耗低和面积小是很困难的,通常要做一些折中,例如为了达到更快的速度,电路的功耗就只能大一些。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。