一、实验目的

① 掌握TTL与非门逻辑功能的测试方法。

② 熟悉TTL与非门主要参数的测试方法。

二、实验原理

本实验采用4输入双与非门TO63(同74LS20),即在一块集成块内含有两个互相独立的与非门,是一种中速4输入端与非门。其电路图与外引线排列图如图2.2.1所示。

图2.2.1 TO63(同74LS20)与非门电路图与外引线排列图

1.与非门的逻辑功能

与非门的逻辑功能是:当输入端中有一个或一个以上是低电平时,输出端为高电平;只有当输入端全部为高电平时,输出端才是低电平(即有“0”得“1”,全“1”得“0”。),其逻辑表达式为Y = AB4。

2.TTL与非门的主要参数

(1)低电平输出电源电流ICCL

低电平输出电源电流ICCL是指所有输入端悬空、输出端空载时的电源电流。ICCL的大小标志着门电路的功耗PL的大小,PL=UCCICCL。由于电路导通时的功耗大于电路截止时的功耗,所以手册中的规范值通常只列出ICCL的数值。ICCL测试电路如图2.2.2(a)所示。

(2)高电平输出电源电流ICCH

高电平输出电源电流ICCH是指输出端空载,每个门各有一个以上的输入端接地,电源供给器件的电流。通常ICCL>ICCH,ICCH也标志器件静态功耗的大小。ICCH测试电路如图2.2.2(b)所示。

图2.2.2 TTL与非门静态参数测试电路图

(3)低电平输入电流IiL

低电平输入电流IiL又称输入短路电流,是指被测输入端接地,其余输入端悬空时由被测输入端流出的电流。在多级门电路中,IiL相当于前级门输出低电平时,后级向前级门灌入的电流,它关系到前级门的灌电流负载能力,即直接影响前级门电路带负载的个数,因此都希望IiL小些。IiL测试电路如图2.2.2(c)所示。

(4)高电平输入电流IiH

高电平输入电流IiH是指被测输入端接高电平、其余输入端接地时流进输入端的电流。在多级门电路中,它相当于前级门输出高电平时,前级门的拉电流负载,其大小关系到前级门的拉电流负载能力,因此希望IiH小些。由于IiH较小,难以测量,一般不进行测试。IiH测试电路如图2.2.2(d)所示。

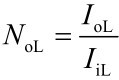

(5)扇出系数No

No是指门电路能驱动同类门的个数,它是衡量门电路负载能力的一个参数。TTL与非门有两种不同性质的负载,即灌电流负载和拉电流负载,因此有两种扇出系数,即低电平扇出系数NoL和高电平扇出系数NoH。因为IiH<IiL,所以NoH>NoL,故常以NoL作为门的扇出系数。

NoL的测试电路如图2.2.3所示,门的输入端全部悬空,输出端接灌电流负载RP。调节RP使IoL增大,UoL随之增高,当UoL达到UoLm(手册中规定低电平规范值0.4 V)时的IoL就是允许灌入的最大负载电流,则 ,通常NoL>8。

,通常NoL>8。

图2.2.3 扇出系数测试电路

图2.2.4 传输特性测试电路

(6)电压传输特性

电压传输特性是反映输出电压uo与输入电压ui之间关系的特性曲线。从电压传输特性上可以读出输出高电平UoH、输出低电平UoL、开门电平Uon、关门电平Uoff、阈值电平UT以及干扰容限等参数。

① 输出高电平UoH是指与非门有一个以上输入端接地或接低电平时的输出电平值。此时门电路处于截止状态。如输出空载,UoH约3.6 V。当输出端接有拉电流负载时,UoH将下降。

② 输出低电平UoL是指与非门的所有输入端均接高电平时的输出电平值。此时门电路处于导通状态。如输出空载,UoL约为0.1 V。当输出接有灌电流负载时,UoL将上升。

③ 开门电平Uon是指输出为标准低电平时,允许输入高电平的最低电平值。只要输入电平稍低于Uon,输出将超出标准的低电平。通常Uon≤1.8 V(测量时可用UoL=0.4 V所对应的输入电平作为Uon)。

④ 关门电平Uoff是指输出为标准高电平时,允许输入低电平的最大值。只要输入电平稍高于Uoff,输出将低于标准的高电平。通常Uoff≥1.0V(测量时可用UoH=2.7 V或2.4 V所对应的输入电平作为Uoff)。

⑤ 阈值电平UT是指与非门的工作点处于电压传输特性中输出电平迅速变化区(转折区)中点时的输入电平值。当与非门工作于这一电平时,输入信号的微小变化将引起电路状态的迅速改变。不同电路的UT值略有差异,一般在1.35 V左右。

(7)平均传输延迟时间tpd

tpd是衡量门电路开关速度的参数,是指输出波形边沿的 0.5Um点至输入波形对应边沿0.5Um点的时间间隔,如图2.2.5所示。(https://www.xing528.com)

图2.2.5 传输延迟特性及tpd测试电路

图2.2.5(a)中的tpdL为导通延迟时间,tpdH为截止延迟时间,平均传输延迟时间为:

tpd的测试电路如图2.2.5(b)所示。由于TTL门电路的延迟时间较小,直接测量时对信号发生器和示波器的性能要求较高,故实验采用测量由奇数个与非门组成的环形振荡器的振荡周期T来求得。其工作原理是:假设电路在接通电源后某一瞬间,A点的逻辑“1”经过三级门的延时后变为逻辑“0”,再经过三级门延时后,A点电平又重新回到逻辑“1”。电路的其他各点电平也跟随变化。这说明使A点发生一个周期的振荡,必须经过6级门的延迟时间,因此平均传输延迟时间为 。

。

三、实验设备与器件

+5 V直流电源;逻辑电平开关;0-1指示器;直流数字电压表;直流毫安表;直流微安表;74LS20×2;电位器1 kΩ,10 kΩ;电阻200 Ω(0.5 W)。

四、实验内容

1. 验证TTL集成与非门74LS20的逻辑功能

按图2.2.6接线,门的四个输入端接逻辑开关输出插口,以提供“0”与“1”电平信号,开关向上,输出逻辑“1”;开关向下,输出逻辑“0”。门的输出端接由LED发光二极管组成的0-1指示器的显示插口。LED亮的为逻辑“1”,不亮为逻辑“0”。按表2.2.1逐个测试集成块中两个与非门的逻辑功能。

注意:TTL电路对电源电压要求较严,电源电压UCC只允许在+5(1±10%)V的范围内工作,超过5.5 V将损坏器件;低于4.5 V器件的逻辑功能将不正常。

图2.2.6 与非门逻辑功能测试电路

表2.2.1 图2.2.6所示测试电路的测试值

2.74LS20主要参数测试

① 分别按图2.2.2,2.2.3和2.2.5(b)接线,测试ICCL,ICCH,IiL,IoL,No,tpd,并将测试结果记入表2.2.2中。

表2.2.2 与非门技术指标测试值

② 按图2.2.4接线,调节电位器RP,使Ui从0 V向高电平变化,逐点测量Ui和Uo的对应值,记入表2.2.3中。

表2.2.3 与非门传输特性测量值

五、思考题

① 测量扇出系数No的原理是什么?为什么只计算输出低电平时的负载电流值,而不考虑输出高电平时的负载电流?

② 为什么TTL电路输入端悬空相当于输入逻辑“1”电平?

③ 讨论TTL与或非门闲置输入端的处置方法。

六、实验报告要求

① 记录实测电路参数,并与器件规范值作比较。

② 用坐标纸画出电压传输特性曲线,从曲线中读出各有关参数值。

③ 讨论TTL与非门闲置输入端的各种处置方法各有什么优缺点。

七、TTL集成电路使用规则

① 接插集成块时,要认清定位标记,不得插反。

② 电源电压使用范围为+4.5~+5.5 V,实验中要求使用+5 V,电源极性绝对不允许接错。

③ 输入端通过电阻接地,电阻值的大小将直接影响电路所处的状态。当R≤680 Ω时,输入端相当于逻辑“0”;当R≥4.7 kΩ时,输入端相当于逻辑“1”。对于不同系列的器件,要求的阻值不同。

④ 输出端不允许并联使用,否则不仅会使电路逻辑功能混乱,并会导致器件损坏。

⑤ 输出端不允许直接接地或直接接+5 V电源,否则将损坏器件。有时为了使后级电路获得较高的输出电平,允许输出端通过电阻R接至UCC,一般取R=3~5.1 kΩ。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。