这里介绍一种高性能的捷变频信号发生器,利用锁相环路和锁频环路相结合的特点,实现快速而精确的跳频输出。单环路小数分频锁相环路实现高分辨率的频率合成,延迟线鉴频器锁频环路利用调频误差信号稳定VCO输出频率,降低调频噪声。锁频环路固有的几兆赫兹的环路带宽,减少了频率转换时间,被用作快速频率切换或跳频信号输出。

延迟线鉴频器由RF功率放大器、功分器、加热延迟线、可控移相器和混频式鉴相器组成,延迟线通路相对于移相器通路产生一个固定的相位移,可用式(2-26)表示:

![]()

式中,Δφ(fm)为瞬时相位起伏,Δf(fm)为瞬时频率起伏,τ为延迟线延迟时间。

大多数鉴相器都是混频器,其输出电压正比于输入信号相位差的余弦函数,为保证在圈作频带内能正常工作,移相器必须保证输入信号正交,即相位相差90°,即鉴相器相位差的余弦函数接近于零。实际应用中,鉴相器工作频率限制在载波频率周围一个小的频率范围内,以保证其响应是比较线性的。

延迟线鉴频器的传输函数,即从输入端的RF调频到输出端的音频解调传输函数G(fm),经过严格的推导可用式(2-27)表示:

![]()

式中,Kφ为鉴相器的鉴相灵敏度,fm为调制频率。

当环路带宽定义为环路增益为1的频率时,环路带宽为:(https://www.xing528.com)

![]()

根据上式分析,延迟线鉴频器锁频环路具有很宽的环路带宽,频率转换时间很短,可以产生频率捷变输出信号。

我们知道,压控振荡器谐振回路的相频特性决定了振荡信号的边带噪声,Q值越高,相频特性越陡峭,偏离谐振频率以外频率的相移越大,越不能满足振荡的相位条件,从而出现在边带上的噪声越小。压控振荡器的相频特性是固定的,Q值的提高非常有限。延迟线鉴频器锁频环路可以看作是压控振荡器的一个附加相移网络,使偏离载波的频率产生附加的相移,破坏其振荡的相位条件,从而大大降低了振荡器的调频噪声,使输出信号的相位噪声得到明显改善。这是延迟线鉴频器锁频环路的另一显著作用,可以提高捷变频合成信号发生器的频谱纯度。

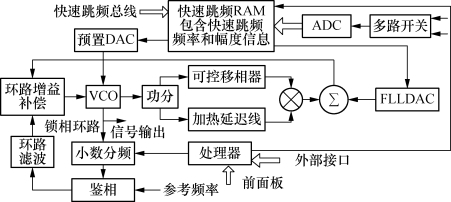

如图2-29所示,锁相环路输出合成射频信号,为锁频环路的校准提供了稳定的输出频率,锁频环路最终锁定在锁相环路输出频率上。此时,锁频环路的调谐电压被测量,并经过A/D转换后,将转换数据存储于快跳速跳频RAM中,称为跳频的学习校准。

图2-29 宽带锁频环路捷变信号发生器原理框图

在学习校准过程中,跳频序列中的每一个频率设置电压都被测量并存储于不同的存储器地址单元中。这些设置参数包括VCO预调电压、锁相环路增益补偿、锁频环路增益补偿。通过环路增益补偿,消除各种因素引起的频率灵敏度的变化,使环路在整个频率范围内达到充分一致的环路增益。跳频时通过调用快速跳频RAM中的存储数据,并经D/A转换后,调谐锁频环路,使VCO输出频率与原始的合成信号频率的误差处于微小的可接受范围内,跳频参数的校准和预置大大缩短了频率转换时间。

可通过下列过程产生跳频输出,首先通过前面板或后面板输入接口,设置所需的跳频信道和跳频序列,锁频环路通过学习校准,存储每个频率点的设置参数。当接到跳频触发命令时,关断锁相环路,只接入锁频环路。这些设置参数重新输入到锁频环路,调谐锁频环路产生期望的跳频输出。所以,跳频输出信号不是相关的合成信号,但是频率稳定的输出信号。

在频率转换时间和频谱纯度指标处于同等数量级的频率合成器中,利用延迟线鉴频器锁频环路可以大大降低成本和复杂度。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。