现代电子对抗技术对信号源的要求:频率覆盖范围宽、频率分辨率高、频率稳定度高、频率切换速度快、频谱纯度高、体积小。只有频率合成器才能满足这些综合要求,而实现频率捷变合成信号发生器的方法主要有3种:直接模拟频率合成法(DAS)、间接频率合成法(锁相环路法(PLL)或锁频环路法(FLL))、直接数字频率合成法(DDS)。

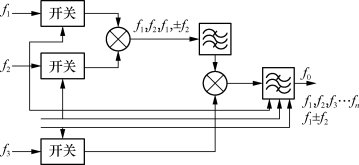

图2-25 直接模拟频率合成原理框图

早期的捷变频合成信号源多采用直接模拟频率合成法,如图2-25所示,这种技术使用了大量的高稳晶体振荡器,通过混频、倍频、分频、带通滤波等方法,完成对频率加、减、乘、除的四则运算和滤波,获得所需的最终频率。其显著特点是频率切换速度快、相位噪声低、输出频率高、工作可靠,是比较理想的模拟捷变频合成信号源,在解决了相位相关性后,估计在电磁环境模拟器中会得到更加广泛的应用。但需要大量的晶体振荡器、混频器、倍频器、分频器和窄带滤波器,造成设备体积庞大、造价高、难以集成,而且杂散信号难以滤除。现在的捷变频合成信号源中已很少采用。

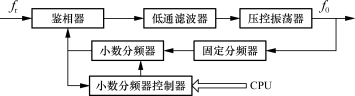

图2-26 锁相环路原理框图

间接频率合成法之一是锁相环路法,如图2-26所示,受控振荡器产生的频率经过分频后送到鉴相器中与参考频率鉴相,产生的误差电压经过环路滤波器滤除高频分量,控制受控振荡器产生与参考频率具有同样准确度和稳定度的频率。锁定时,受控振荡器输出频率的1/N分频率与参考频率的频差为零,相差保持一个常量,即输出频率的相位被锁定到输入参考频率的相位上,输出频率和输入参考频率有如下具体关系:

![]()

式中,f0为输出频率,N为可变分频器的分频比,fr为输入参考频率。

在采用数字分频器后,特别是采用小数分频及相位抖动消除技术后,制造技术产生了质的飞跃,数字锁相环路具有以下主要优点:

①输出频率的长期稳定度达到与参考频率相同的水平,而参考振荡器可采用稳定度高的晶体振荡器或更高的频率标准;

②采用数字分频器后,容易实现程控分频;(https://www.xing528.com)

③只需很少的滤波器,易于集成,体积小,功耗低,因此得到了广泛的应用。

在单环锁相环路中,输出频率f0步进等于输入参考频率fr,降低输入参考频率会引起频转换时间变长和环路稳定性变差等问题,因此频率分辨率不能太高。单环锁相环路由于受参考频率和环路带宽的限制,在频率分辨率、频率转换时间和频谱纯度等指标之间不能兼顾。

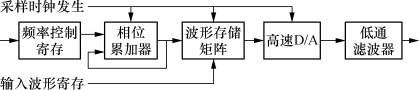

随着现代电子、微电子技术的发展,直接数字频率合成法采用全数字技术,在相位点进行频率合成,如图2-27所示,波形存储矩阵预存一个周期的波形参数,相位累加器在频率控制寄存器及精确时钟的控制下,顺序产生存储器访问地址,使存储器按指定的步进和顺序输出波形数据,经高速D/A转换后,获得所需的波形信号。低通滤波器使输出波形得以平滑,减少了量化噪声。

图2-27 直接数字频率合成原理框图

直接数字频率合成器具有以下主要优点:

①频率分辨率高,从原理上分析,只要相位累加器的位数足够长,理论上频率合成器的频率间隔可以做到任意小,一般可以做到毫赫兹,即零点零零几赫兹。

②频率转换速度快,主要取决于时钟频率、信号取样周期和D/A转换速率,频率转换不存在捕捉稳定过程,只需几个取样时钟周期即可输出稳定频率信号,最快频率转换时间可做到20 ns。

③相位连续而且可控,频率转换时,新的相位增量是在前面取样时刻相位的基础上进行累加,故不会发生相位突变,且通过改变相位预置可以进行调相,相位噪声低。

④采用直接数字频率合成便于和计算机接口,利于应用微机软件系统实现数字信号处理,从而实现各种高性能的数字调制。

其主要缺点是:杂散输出较大,分布较广,不利于滤波;最高输出频率较低,受时钟频率的限制,约为时钟频率的40%。

随着电子对抗技术的不断发展,跳频电台及技侦设备要求合成信号源的转换速度快,跳频范围宽,频率步进间隔小,频谱纯度好,而且要求提高输出频率。综合间接频率合成(即锁相环路)和直接数字频率合成的优势,采用DDS与PLL相结合的方法,PLL用于实现频率合成,提高输出频率,DDS用于实现高速频率转换和一定的跳频带宽。或采用PLL与FLL相结合的方法,利用FLL的宽带特性和低噪声特性,提高跳频速率,改善频谱纯度。二者在一定程度上都可满足设备对捷变频合成信号发生器的要求。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。