1)F-NPLL原理

实现小数分频的F-NPLL结构基本与NPLL相同,其组成如图2-19所示。图的右半部是具有÷N的锁相环,只是在VCO至÷N之间插入了一个脉冲删除电路。脉冲删除电路的功能是在适当的时候删掉一个从VCO至÷N分频器的脉冲,脉冲何时被删除则受左边电路的控制。

在图2-19的左半部,小数值F以BCD(二—十进制数)码写入F寄存器,在输入基准频率fr的作用下,F寄存器的存数与相位累加器的存数在BCD全加器中相加。当BCD全加器达到满度值时就产生溢出。溢出脉冲加到脉冲删除电路删除一个采自VCO的脉冲,使÷N电路少计一个脉冲,相当于分频系数为(N+1)。在溢出的同时,全加器将本次运算的余数存入相位累加器。如果在fr作用下全加器相加的结果达不到满度值,则不会产生溢出,右边锁相环仍按照÷N进行分频,并且本次相加的结果存入累加器,作为全加器的基数,等待下次相加,如此重复进行。在图2-19中,模拟相位内插器根据相位累加器存数情况向锁相环的低通滤波器(LPF)提供相应的直流偏移量,使得锁相环在÷N或÷(N+1)时都能平衡地工作。通常模拟内插器由D/A转换器实现。现在假设F=0.1,那么在第一个Tr周期(Tr=1/fr)中就有0.1在全加器中与相位累加器的内容累加。假如累加器的起始值为0,则经过10次累加之后,全加器溢出,产生一次(N+1)分频,其他9次均为N分频,因此得VCO的输出频率(即锁相环输出频率)为:

图2-19 F-NPLL的组成

再举一个例子。设F=0.32,相位累加器的初值为0。因此,在每一个Tr周期全加器将以0.32与相位累加器的基数相加。直至第4个周期时,全加器溢出使脉冲删除电路消去一个脉冲,而余数为0.32×4-1=0.28。再经过3个Tr周期,将会有0.28+0.32×3=1+0.24产生一次溢出,一共经过25个Tr周期,全加器8次溢出,并且累加器存数为0。因此,图2-19的输出频率f0为:

![]()

从上述讨论可知,小数分频时小数部分位数取决于F寄存器的位数。从原理上来说,小数部分的位数可以任意扩展,位数越多合成器的频率分辨率就越高。例如HP3325信号发生器频率分辨率高达1μHz,该仪器就是采用小数分频锁相环实现的。

再以F=0.1进一步讨论问题。假设fr=1 MHz,N=10。现在N.F=10.1,那么输出频率f0=N.Ffr=10.1 MHz。这就是说,在F-NPLL里,当fr变化一周时,VCO的输出比NPLL(N=10)的输出频率多变化1/10周,从相位来说多变化36°。经过10Tr之后,VCO的输出相位变化累积为360°,多出一个信号周期。为了实现小数分频,每逢相位累积超过360°时,就在VCO的输出删除一个信号周期,这时相当于分频系数为(N+1)。另外,在F=0.1时,图2-19中F寄存器置数为0.1,在fr作用下全加器每一次增量为0.1,经过10次相加将有一个进位信号到脉冲删除电路,控制删除VCO输出信号的一个周期,实现(N+1)分频。然后全加器再从0.1开始累加……这就是小数分频的全过程。当F=0.32时,只要4次累加就有一个进位信号,并且余数为0.28,因此脉冲删除次数比F=0.1时的多,分频系数小数部分的数值也就大(0.32>0.1)。因此,可以认为F寄存器中的置数值就是N.F中的F部分。

2)F-NPLL和NPLL比较(https://www.xing528.com)

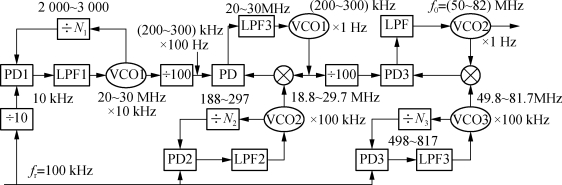

例2.1 要求一频率合成器,输出频率f0=(50~82)MHz,频率分辨率Δf=1 Hz。若用NPLL,根据频率要求,并且希望有较好的相位噪声特性,一般需要3个NPLL和2个相加环共5个环路,如图2-20所示。

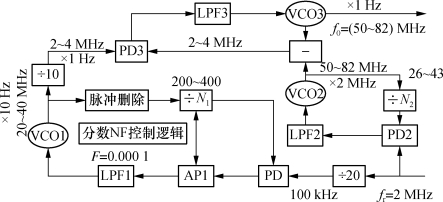

若采用F-NPLL,对于同样要求,只需要3个环路:1个F-NPLL、1个NPLL和1个相加环,如图2-21所示。图中下方AP1即图2-21中的模拟相位内插器。F-NPLL环的倍频系数为200.0001~400。

图2-20 NPLL(50~82)MHz频率合成器框图

对比以上两种频率合成方案可以看出:在达到同样要求的情况下,用F-NPLL要比只用NPLL简洁得多,而且F-NPLL在频率分辨率、频率范围、噪声性能方面都比较优越。由于F-NPLL小数分频部分是由数字电路实现的,可以将小数部分做得很小,以致频率分辨率很高。从理论上讲,可以做到任意分辨率的要求,这取决于小数部分的位数长度,现在使用的位数长度已达12~15位。采用F-NPLL的缺点是环路比较复杂。

3)F-NPLL技术的发展

如前所述,F-NPLL能在提高合成信号源频率分辨率的同时有较快的转换速度,信号源的频谱纯度也得到改善。图2-21中的模拟相位内插器就是用于改善在小数分频时VCO的工作情况,降低输出信号噪声,提高频谱纯度。

图2-21 F-NPLL(50~82)MHz频率合成器框图

这种模拟内插称为模拟补偿法,其缺点是模拟信号由于温度影响及器件老化等原因,在某种程度上又引入了新的寄生分量。因此,人们又提出采用数字信号处理中的“噪声形成”(Noise-Shaping)方法来改善F-NPLL的相位噪声性能。“噪声形成”是将寄生信号的全部能量转换为频率的高端频谱,进而被F-NPLL环路滤除,借以提高频谱纯度。现今的仪器设备几乎都倾向于采用这种先进的F-NPLL技术。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。