1.定时器计数原理

图5-19是计数器的功能框图,从图5-19中能分析其工作原理。需要明确的是,计数器并不是被输入的时钟脉冲驱动进行计数操作的,实际上,计数器是按CPU的时钟速度运行的,输入定时器的时钟信号只是作为内部的计数使能信号的一个触发源。由一个边沿检测电路(图5-19中的边沿检测)对该时钟脉冲进行检测,一旦检测到有效的边沿,就会产生宽度为一个CPU时钟周期的计数使能脉冲。在计数使能由低变高时,才允许计数器进行计数操作。这样,对于用户而言,计数器就像是由输入时钟产生的使能信号驱动进行计数。

当定时器计数达到定时器计数周期寄存器中设定的值后,会在下一个CPU时钟脉冲处立即复位为0。因此,计数器计数范围是0~N。如果设置计数周期为2,CPU时钟源(CLK- SRC=1)选择为1/8DSP时钟周期,那么启动后,定时器的计数状态是:

0,0,0,0,0,0,0,0(8个DSP时钟脉冲后,计数值加1,下一个计数值为1)

1,1,1,1,1,1,1,1(8个DSP时钟脉冲后,计数值再加1,下一个计数值为2)

2,0,0,0,0,0,0,0(计数器达到2,马上恢复到0,定时器完成一次定时)

1,1,1,1,1,1,1,1(定时器重复上述步骤)

2,0,0,0,0,0,0,0

…

虽然整个计数过程中计数器的计数值到达了2,但是周期是16个CPU时钟周期(2×8),而不是12个CPU时钟周期(3×4)。所以,用户在向下计数周期寄存器中设置的值应该是TIMER PERIOD(定时周期数),而不是TIMER PERIOD+1。

2.定时器的复位和使能

表5-16描述了如何使用定时器控制(CTL)寄存器的GO位和HLD位使能定时器的基本操作。配置一个定时器可采用如下4个步骤:

1)如果定时器当前不在保持状态,将定时器置于保持状态(HLD=0)。注意,在器件复位后,定时器就处于保持状态。

2)向定时器周期(PRD)寄存器写入期望的值。

3)向定时器控制(CTL)寄存器写入期望的值,不要改变CTL寄存器中的GO位和HLD位。

4)设置CTL寄存器中的GO位和HLD位为1,启动定时器。

表5-16 使用GO位和HLD位的定时器操作

3.定时器时钟源选择

定时器输入时钟脉冲从低电平到高电平的变换(如果INVINP=1,则为从高到低)启动定时器计数器开始计数。驱动定时器输入时钟的两个源为:

1)CLKSRC=0选择TINP引脚上的输入值。该信号被同步以便防止任何因为异步的外部输入产生的不稳定性。TINP引脚的值反映在DATIN上。

2)CLKSRC=1选择内部时钟源。TMS320C62x/C67x DSP使用CPU时钟/4作为内部时钟源,而TMS320 C64x DSP使用CPU时钟/8作为内部时钟源。(https://www.xing528.com)

4.定时器脉冲产生

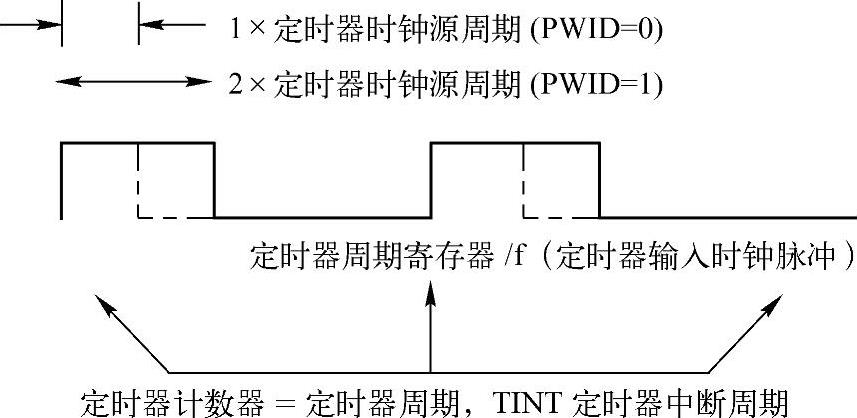

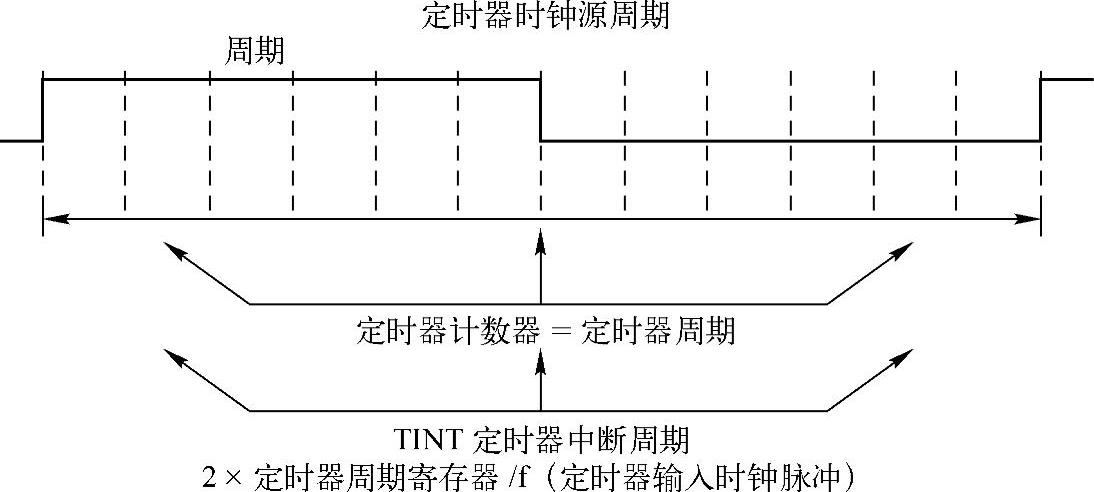

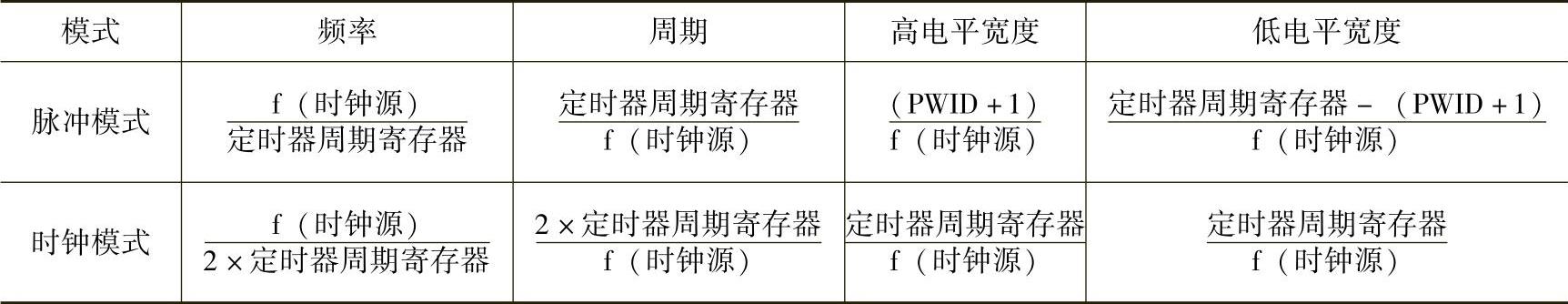

两个基本脉冲产生模式是指脉冲模式(如图5-23所示)和时钟模式(如图5-24所示)。用户可以使用定时器控制(CTL)寄存器的CP位来选择模式。注意,在脉冲模式下,CTL的PWID可以设置脉冲宽度为1或2个输入时钟周期。该特征的目的就是为了在TSTAT驱动TOUT输出时,能提供最小的脉冲宽度。当TOUT被用做一个定时器引脚(FUNC=1)时,TSTAT驱动这个引脚。表5-17分别给出了在脉冲模式和时钟模式下各种TSTAT时序参数的公式。

图5-23 脉冲模式下的定时器操作

图5-24 时钟模式下的定时器操作

表5-17 脉冲模式和时钟模式下各种TSTAT时序参数的公式

5.定时器工作的边界条件

以下几种边界条件会对定时器的工作产生影响。

1)定时器周期(PRD)寄存器和定时器计数(CNT)寄存器的值都是0。在器件复位后和定时器启动前,TSTAT保持默认值0。如果在定时器周期寄存器和定时器计数寄存器中的值都是0的情况下,设置HLD=1和GO=1启动定时器后,定时器的操作依赖于CP模式的选择。如果设置为脉冲工作模式,那么不论定时器是否被保持,TSTAT始终等于1。在时钟模式下,当定时器被保持(HLD=0),则TSTAT保持以前的值不变,并且当HLD=1时,TSTAT值会按CPU时钟/2的频率变化。

2)计数器溢出。如果定时器计数寄存器中初始化的值超过了定时器周期寄存器中的值,在计数时定时器会首先计数到最大值(FFFFFFFFh),然后恢复为0,再继续计数。

3)对工作中的定时器进行寄存器写入。写入的值更新定时器计数寄存器,新状态更新定时器控制寄存器。

4)脉冲模式下小的定时器周期值。如果脉冲模式下设置的周期值≤PWID+1,则TSTAT保持为高电平。

6.定时器中断与仿真

TSTAT信号直接产生CPU中断和EDMA同步事件,中断的频率和TSTAT的频率相同。在使用仿真器调试时,CPU可以被暂停。对于TMS320 C620x/C670x DSP,在一次仿真暂停期间,当选择CPU时钟/4为时钟源时,定时器也会暂停。此时,计数器只在CPU没有暂停的周期内进行计数。对于TMS320 C64x DSP,在仿真暂停期间,不管时钟源如何,定时器都会继续计数。

7.定时器引脚用做通用I/O

当器件复位时,定时器引脚TINP和TOUT为通用目的输入/输出引脚。通过配置定时器控制寄存器,即使当定时器运行时,TINP和TOUT引脚也可以用做通用目的输入/输出引脚。

如果定时器不运行,则TINP引脚一直是通用目的输入引脚。如果定时器正在运行,并且如果CTL的CLKSRC=1,则TINP引脚是通用目的输入引脚,此时意味着使用一个内部时钟源替代TINP引脚。当TINP是通用目的输入引脚时,输入值可以从CTL的DATIN位读取。

如果FUNC=0,则TOUT引脚是通用目的输出引脚,而不管定时器操作如何。FUNC位选择DATOUT或TSTAT的值作为TOUT引脚的输出。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。