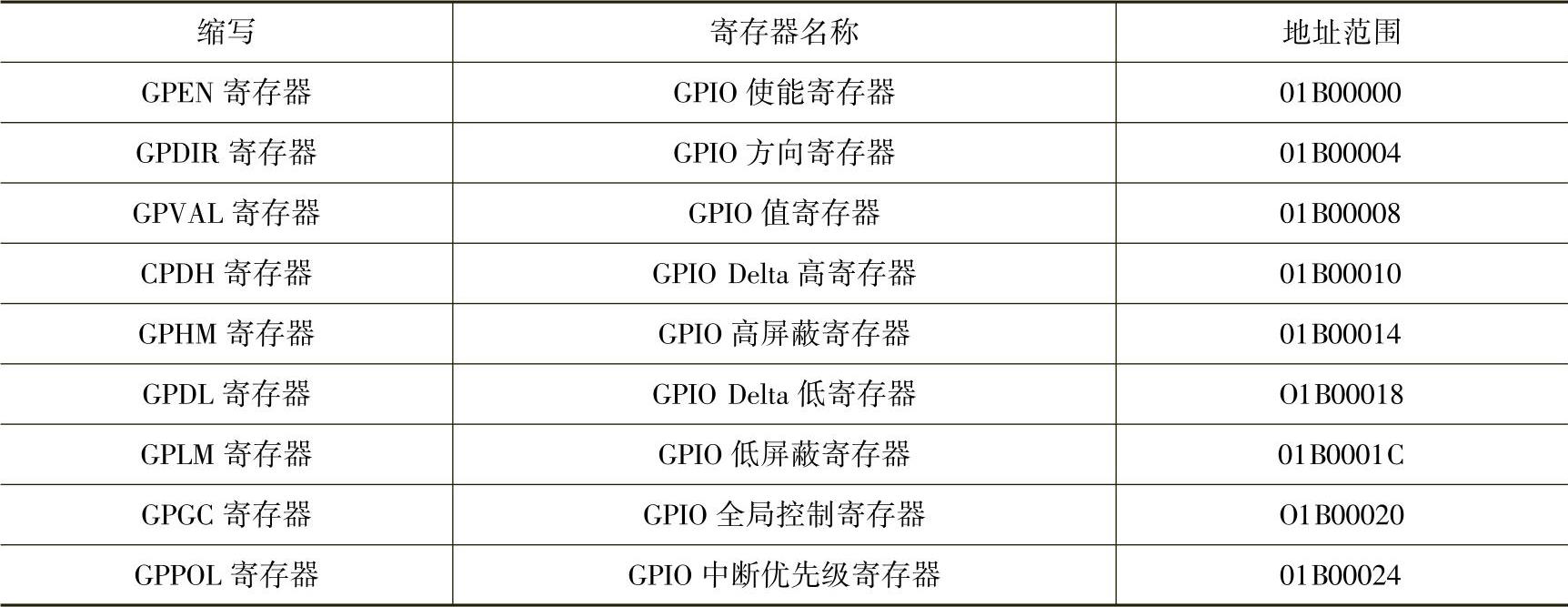

表5-3列出了用于配置GPIO外设的寄存器。

表5-3 用于配置GPIO外设的寄存器

1.GPIO使能(GPEN)寄存器

GPIO使能寄存器使能GPIO引脚为通用目的输入/输出功能。为了在通用目的输入/输出模式下使用任一条GPIO引脚,相关的GPXEN位必须设置为1。GPEN寄存器如图5-8所示,各位段的描述见表5-4。

图5-8 GPEN寄存器

有些GPIO信号是和其他器件信号复用的。对于那些复用的信号,信号的功能由以下方式控制。

1)器件配置输入。复位时,器件配置输入选择用于GPIO引脚或其他模式的复用信号。

表5-4 GPEN寄存器各位段的描述

2)GPEN位段。一个GPXEN位n设置为1,表示GPn引脚用做一个GPIO信号,并且被其他GPIO寄存器所控制。一个GPXEN位n被清除为0,表示GPn引脚不能用做GPIO引脚,它将用于其他目的。

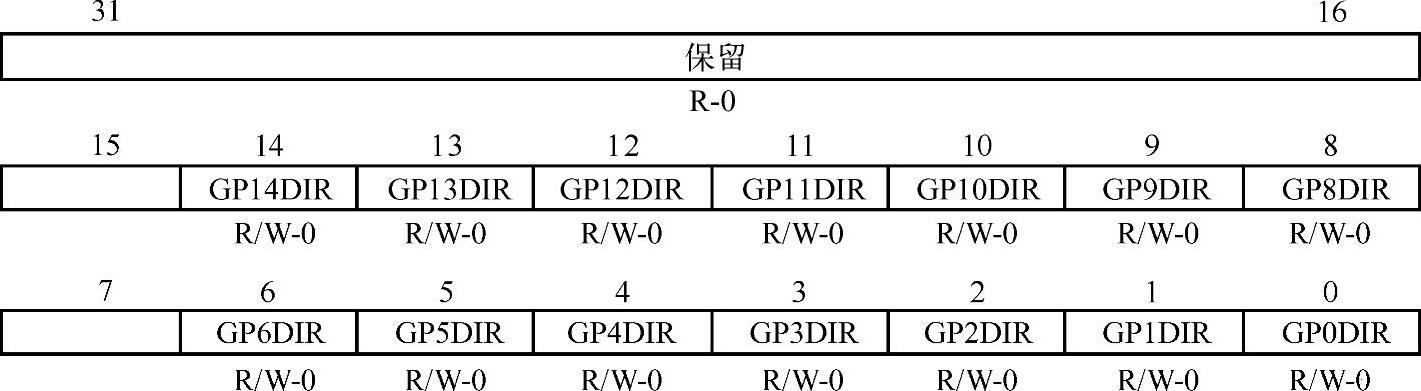

2.GPIO方向(GPDIR)寄存器

GPIO方向寄存器决定了一给定的GPIO引脚是输入还是输出。只有GPEN的GPXEN位使能了相应的GPIO信号,GPDIR才起作用。GPDIR寄存器如图5-9所示。在默认情况下,所有GPIO引脚配置为输入。

图5-9 GPDIR寄存器

当GPIO引脚配置为输出引脚时,这些引脚不会有高阻态特性。复位时,GPIO输出引脚默认为GPIO值寄存器(GPVAL)的值。如果必须驱动GPIO输出为高阻态,GPIO引脚可以配置为输入引脚,然后可以改变为输出引脚。

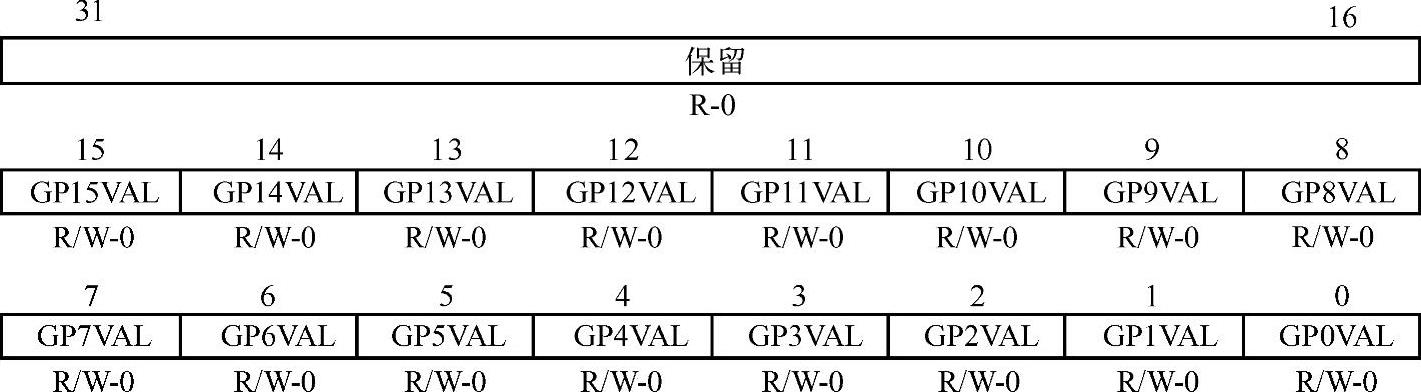

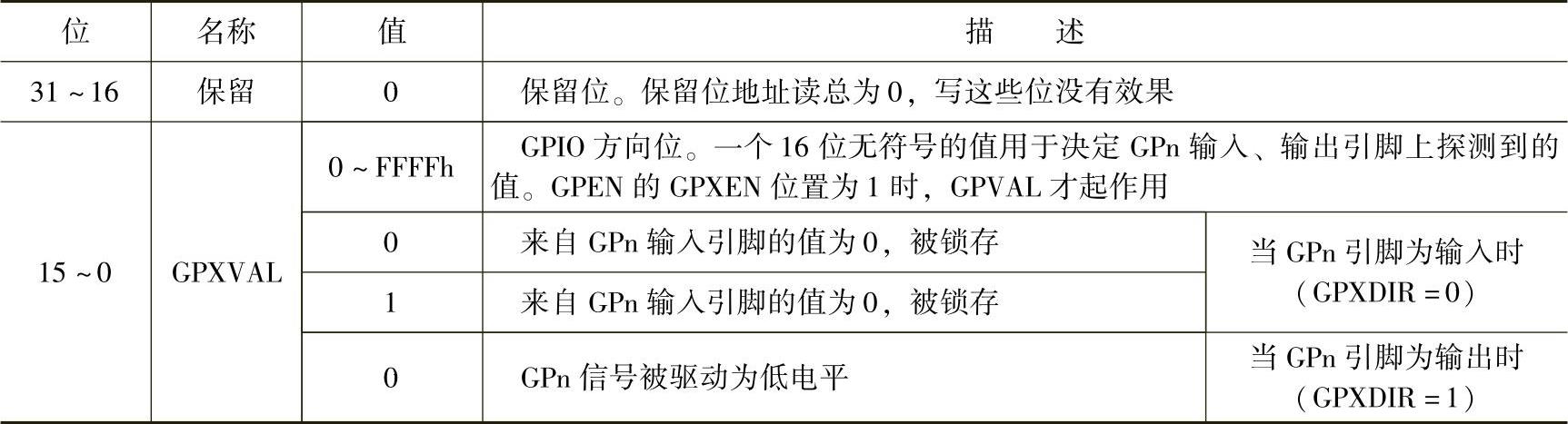

3.GPIO值(GPVAL)寄存器

GPIO值寄存器表示一指定GPIO输出引脚所驱动的值,或一指定GPIO输入引脚上探测到的值。GPVAL寄存器如图5-10所示,其各位段见表5-5。

图5-10 GPVAL寄存器

表5-5 GPVAL寄存器各位段的描述

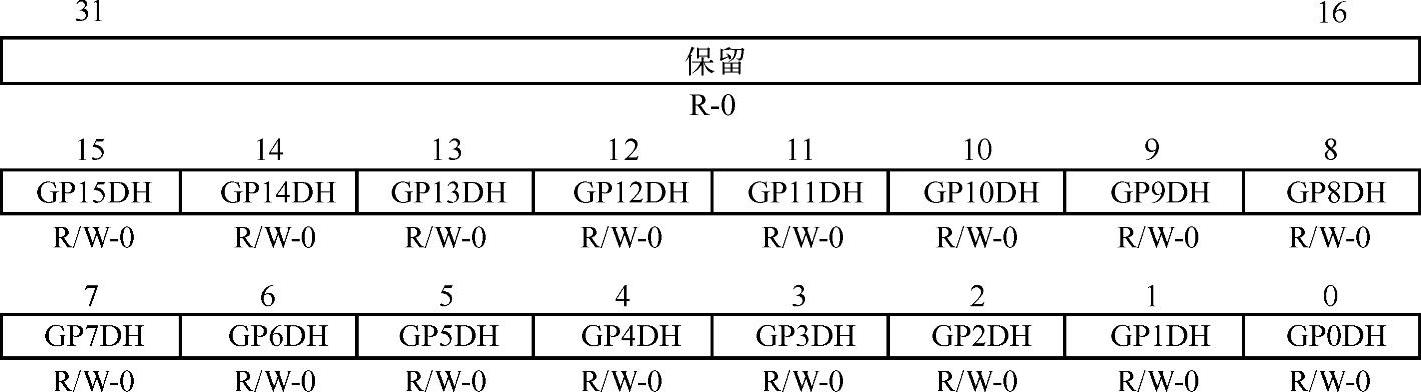

4.GPIO Delta高(GPDH)寄存器

GPIO Delta高寄存器表示已给定的GPIO输入是否已经经历一次从低电平到高电平的转变。如果给定的GPIO引脚配置为输出,则GPDH寄存器中相应的位保持原来的值。向相应的位写1清除该位,写0无效果。GPDH寄存器如图5-11所示,其各位段的描述见表5-6。

图5-11 GPDH寄存器

表5-6 GPDH寄存器各位段的描述

5.GPIO Delta低(GPDL)寄存器

GPIO Delta低寄存器表示给定的GPIO输入是否已经经历一次从高电平到低电平的转变。如果给定的GPIO引脚配置为输出,则GPDL寄存器中相应的位保持原来的值。向相应的位写1清除该位,写0无效果。GPDL寄存器如图5-12所示,其各位段的描述见表5-7。(https://www.xing528.com)

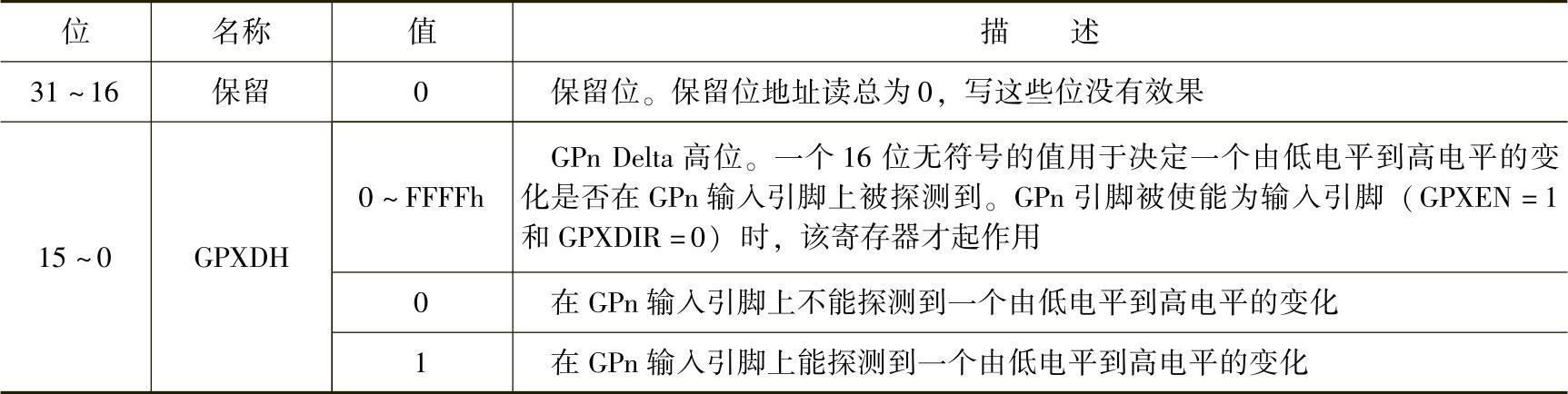

6.GPIO高屏蔽(GPHM)寄存器

GPIO高屏蔽寄存器用来使能指定的GPIO输入产生CPU中断或EDMA事件。如果GPHM位(GPnHM)被禁止,则在相应GPn引脚上的值或变化不会产生一个中断或事件。如果屏蔽位被使能,则根据GPGC寄存器选择的中断模式,在相应GPn输入可以产生一个中断或事件。GPHM寄存器如图5-13所示,其各位段的描述见表5-8。

图5-12 GPDL寄存器

表5-7 GPDL寄存器各位段的描述

图5-13 GPHM寄存器

表5-8 GPHM寄存器各位段的描述

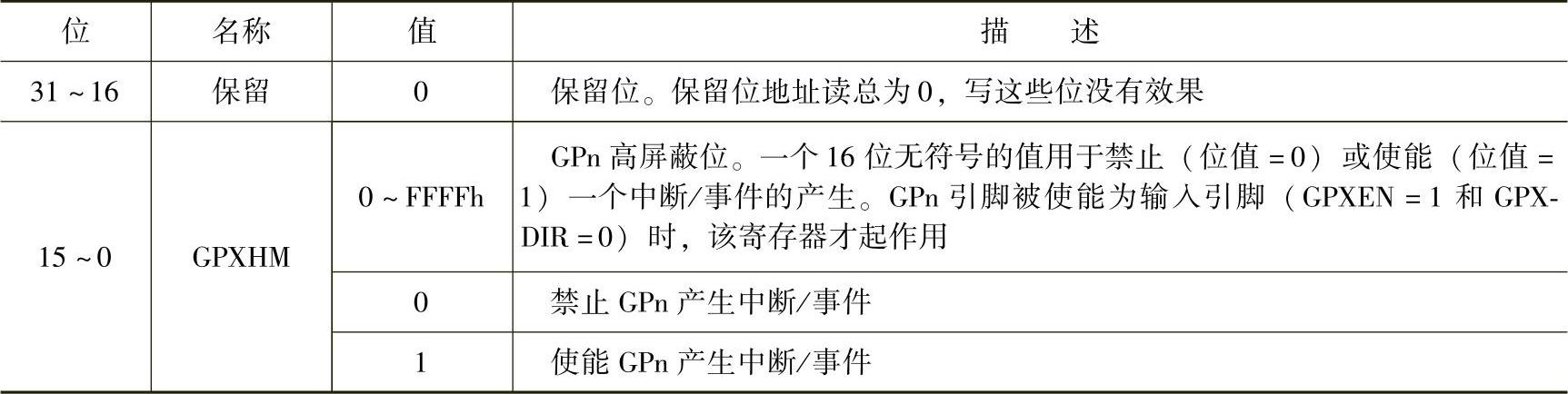

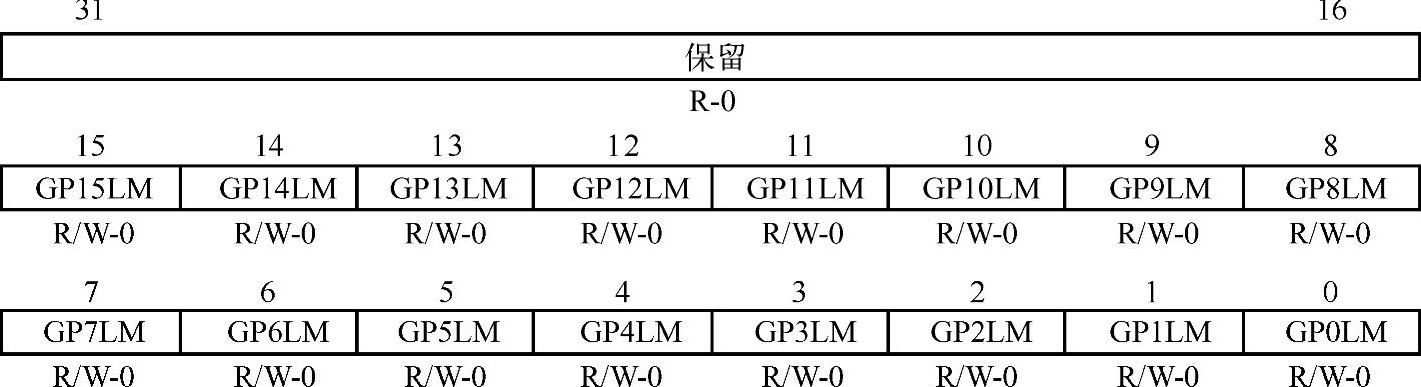

7.GPIO低屏蔽(GPLM)寄存器

GPIO低屏蔽寄存器用来使能指定的GPIO输入产生CPU中断或EDMA事件。如果GPLM位(GPnLM)被禁止,则在相应GPn引脚上的值或变化不会产生一个中断或事件。如果屏蔽位被使能,则根据GPGC寄存器选择的中断模式,在相应GPn输入可以产生一个中断或事件。GPLM寄存器如图5-14所示,其各位段与GPHM寄存器类似(参见表5-9)。

图5-14 GPLM寄存器

表5-9 GPLM寄存器各位段的描述

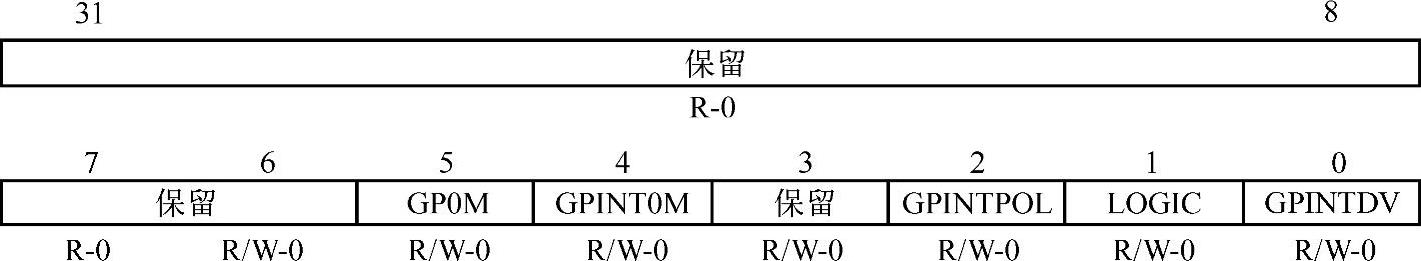

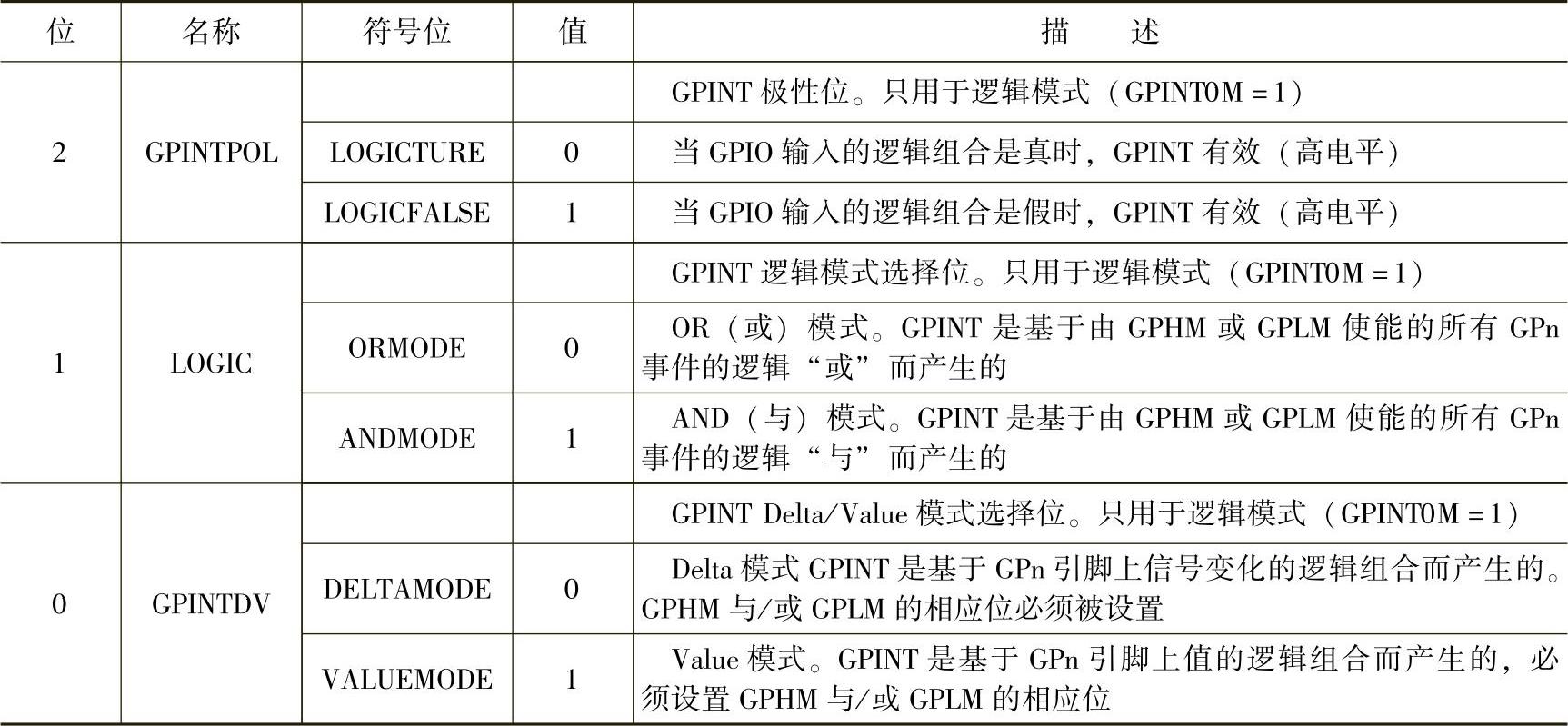

8.GPIO全局控制(GPGC)寄存器

GPIO全局控制寄存器配置GPIO外设的中断/事件产生。GPGC寄存器如图5-15所示,其各位段见表5-10。

图5-15 GPGC寄存器

表5-10 GPGC寄存器各位段的描述

(续)

9.GPIO中断极性(GPPOL)寄存器

GPIO中断极性寄存器用来选择直接传递模式下GPINTn中断/事件信号的极性。为了使用直接传递模式下的GPINT0,GPGC寄存器的GPINT0M必须清除为0。GPPOL寄存器如图5-16所示,其各位段的描述见表5-11。

图5-16 GPPOL寄存器

表5-11 GPPOL寄存器各位段的描述

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。