SPI(Series Protocol Interface)是一个利用4根信号线的串行接口协议,包括主、从两种模式。4个接口信号是:串行数据输入(MISO,Master In Slave Out,主设备输入、从设备输出)、串行数据输出(MOSI,Master Out Slave In,主设备输出、从设备输入)、移位时钟(SCK)和低电平有效的从设备使能信号(SS)。SPI的最大特点是由主设备时钟信号的出现与否来确定主/从设备间的通信。一旦检测到主设备时钟信号,数据开始传输,时钟信号无效后,传输结束。在这期间,要求从设备必须被使能(SS信号保持有效)。

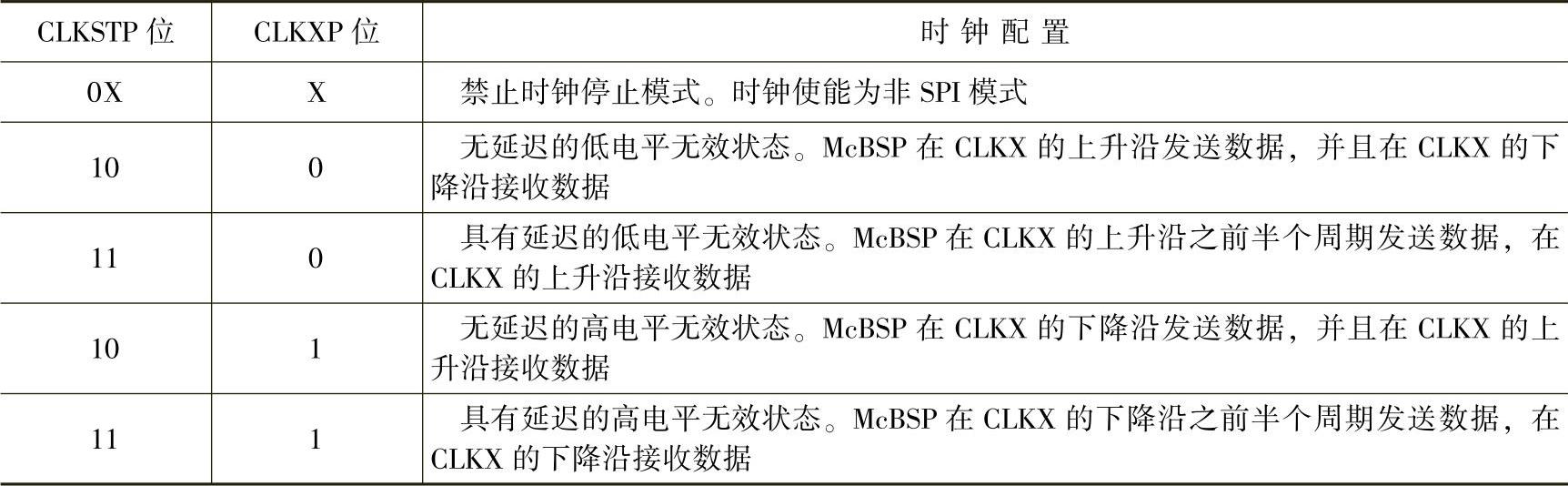

McBSP支持多种不同的SPI传输方式,在SPCR的GLKSTP位及CLKXP位中设置使用何种传输方式。

如果使用McBSP的SPI协议,则其初始化过程如下:

1)设置XRST和RRST为0,禁止McBSP的接收和发送。

2)设置CLKSTP'为0x,禁止时钟停止模式。

3)设置其他相关寄存器。

4)设置GRST为1,使采样时钟发生器开始工作。

5)等待两个以上时钟周期,确保McBSP的初始化完成。

6)设置CLKSTP位,选择采用何种SPI协议传输数据。

7)如果采用DSP直接访问McBSP,则设置XRST和RRST为使能McBSP的接收和发送,其他寄存器不变;如果采用DMA方式访问McBSP,则必须对DMA进行设置启动DMA,然后再设置XRST和RRST为1。

8)McBSP开始以SPI协议工作。

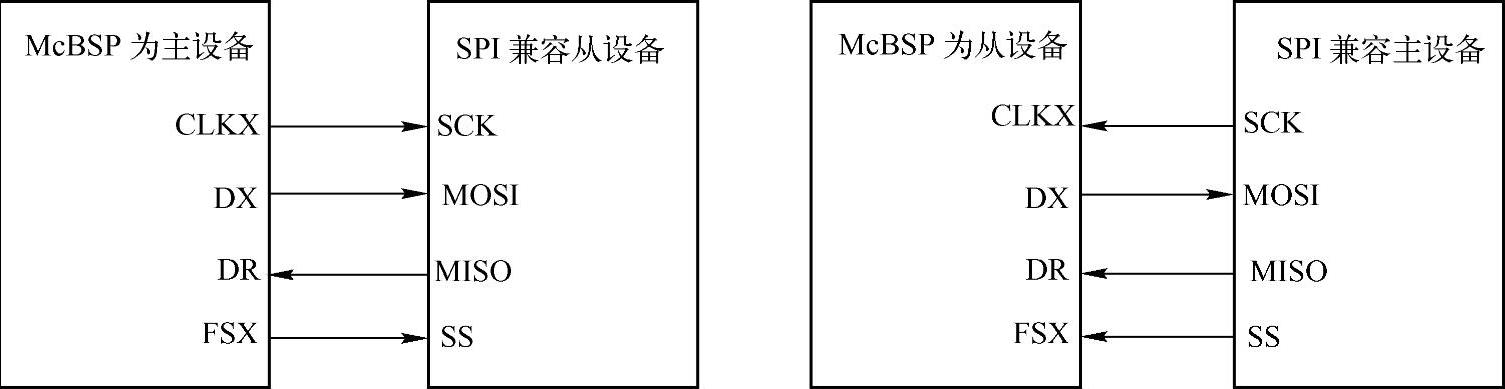

1.McBSP作为SPI设备的硬件连接

McBSP作为主设备和从设备的实例框图如图4-28所示。

McBSP中的传输时钟具有停止模式(CLKSTP)控制选项,这保证了与SPI协议的兼容性。McBSP支持两种SPI传输格式,在SPCR的时钟停止模式位(CLKSTP)中设置。表4-35列出了CLKSTP与CLKXP相配合,对串口时钟工作模式的配置。

图4-28 McBSP作为SPI主设备和从设备的实例框图(https://www.xing528.com)

表4-35 SPI时钟停止模式配置

2.McBSP作为SPI主设备

作为SPI主设备时,由McBSP内部的采样率发生器产生时钟CLKX和从设备使能信号FSX。因此,CLKX应该配置为输出(CLKXM=1),而FSX配置为一个输出并且可以连接到从设备上(FSXM=1)的从设备使能(SS)输入。每个单元的DXR到XSR传输产生从设备使能FSX(SRGR的FSGM=1)。因此为了在SPI主设备模式下接收一个单元,McBSP必须同时发送一个单元(即写DXR),以便产生必需的从设备使能FSX。在McBSP开始将数据移位输出到DX引脚之前,FSX要声明为低电平,以便使能从设备。

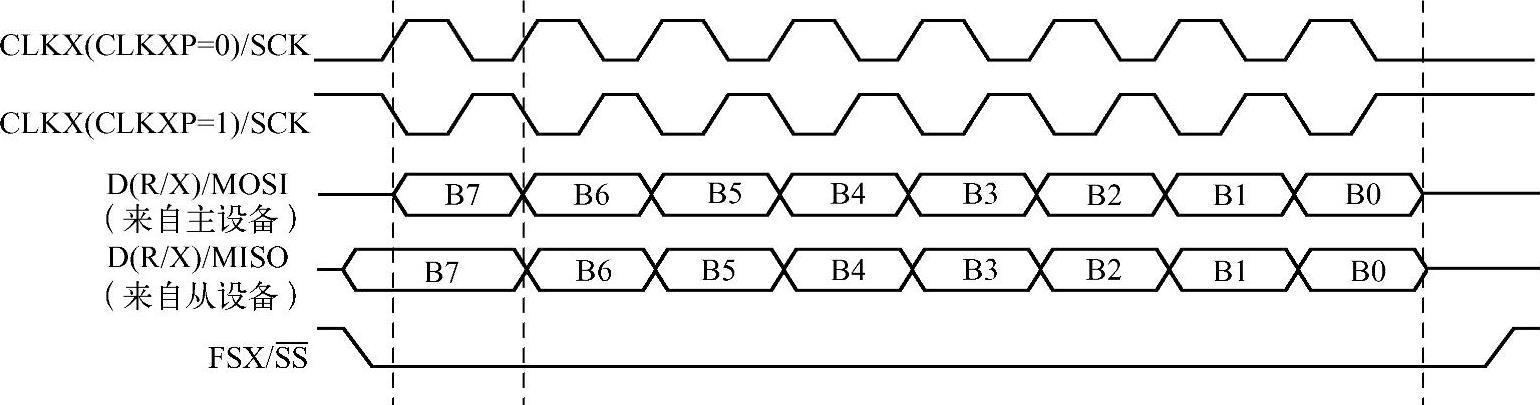

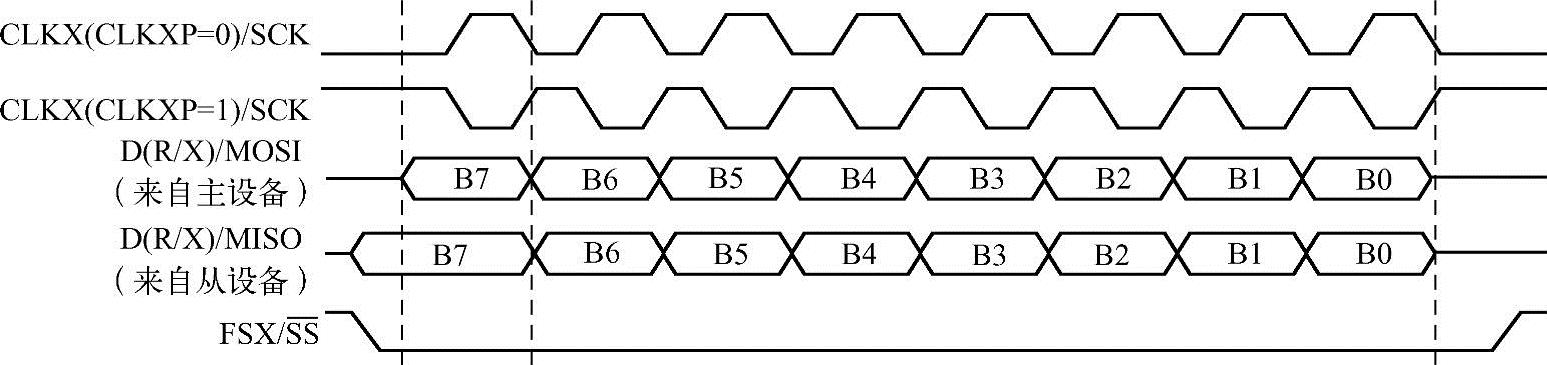

图4-29和图4-30为MOSI和FSX波形。因此,XDATDLY和RDATDLY位必须编程为1。当McBSP为SPI主设备时,XDATDLY的值为0或2会产生不确定的操作,并且RDATD-LY的值为0会使接收的数据移位不正确。

图4-29 CLKSTP=10b时的SPI传输时序图

作为SPI主设备,McBSP通过内部采样率发生器产生CLKX和FSX。用户需要设置SR-GR中的CLKSM位来选择CPU时钟或外部时钟输入(CLKS)作为采样率发生器的时钟源。选择时钟停止模式时,SRGR中的帧发生器位段(FPER和FWID)没有意义。

图4-30 CLKSTP=11b时的SPI传输时序图

对SRGR的CLKGDV(时钟倍率)编程来产生CLKX,按照需要的SPI数据传输速率来编程。在McBSP内部会产生一个连续的CLKX时钟,然后在经过门限制后输出到外部接口,从而实现传输接口所需要的时钟停止模式。因此在McBSP一端,对于发送和接收的内部操作而言,时钟信号实际上是连续的。

3.McBSP作为SPI从设备

当McBSP作为SPI从设备时,由外部的主设备产生所需的主控时钟信号和从设备使能信号。McBSP的CLKX引脚和FSX引脚配置为输入引脚(CLKXM=FSXM=0)。串口按照主控时钟进行数据同步传输,输入的CLKX和FSX信号同时也分别作为McBSP内部接收端的CLKR信号和FSR信号。在进行数据传输之前,外部主设备必须先将FSX信号设置为有效的低电平。

尽管CLKX信号是由外部主设备产生,McBSP内部的采样率发生器仍必须被使能,并被设置为相应的SPI模式。因为McBSP需要利用内部的采样率发生器产生时钟信号,对输入的CLKX和FSX信号进行同步化处理。采样率发生器应当设置为采用CPU时钟作为采样率发生器的时钟源(SRGRCLKSM=1),以及必须保证内部的CLKG信号频率(由SRGR的CLKGDV位控制)至少是SPI数据传输率的8倍,例如,可以令CLKGDV=1,将采样率发生器设置为最大速率。

作为SPI从设备时,McBSP的RCR/XCR中的(R/X)DATDLY位必须设置为0,以保证发送的第一个数据能够出现在DX引脚上,如图4-29和图4-30所示的时序中的MISO波形。(R/X)DATDLY=0,一旦检测到串行时钟CLKX有效,就可以立刻接收数据。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。