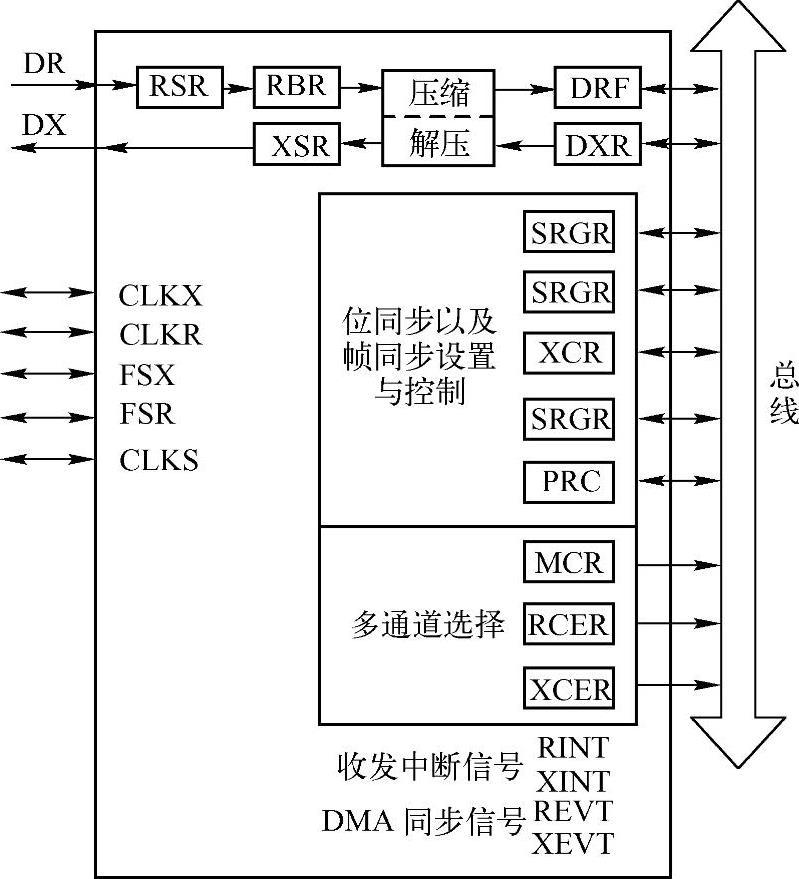

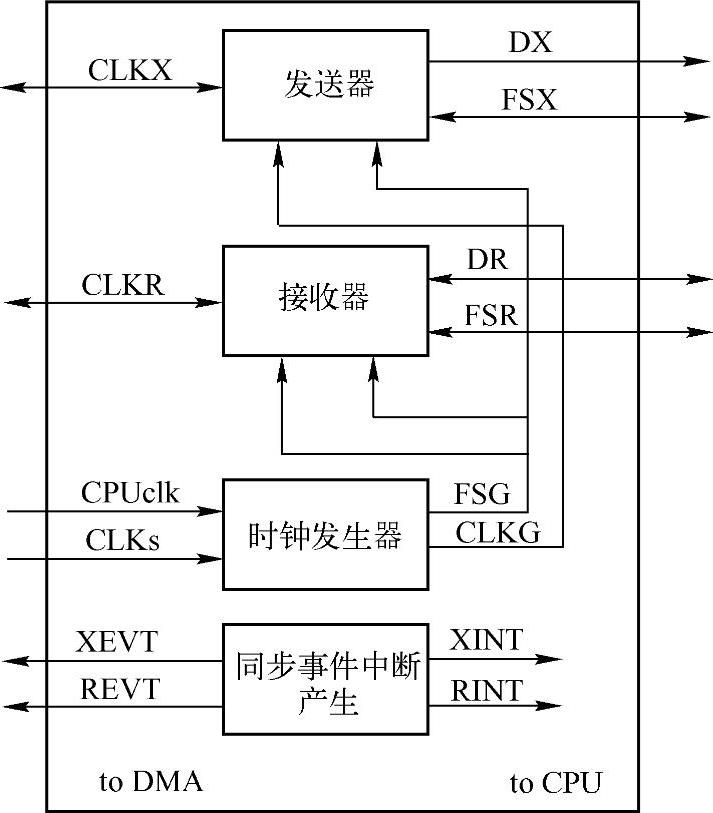

如图4-13所示为McBSP的结构,内部结构如图4-14所示。DSP向数据发送寄存器(DXR)写入发送数据,写入DXR的数据通过发送移位寄存器(XSR)移位输出到DX引脚,外设从DX引脚读取数据。反之,DSP从DR引脚读取数据,移位后写入接收移位寄存器(RSR),然后将数据写入到数据接收缓冲寄存器(RBR)中,RBR再将数据移动到数据接收寄存器(DRR)中,最后等到DSP读取数据。这样的多级缓冲结构使得DSP的片内数据读/写和片外的数据通信可以同时进行。

McBSP还包括一些控制引脚,这些引脚提供数据读/写的位同步和帧同步时钟信号,以及产生DMA控制器需要的同步事件和中断信号。控制引脚的状态一般由McBSP的控制寄存器读取或者设置。

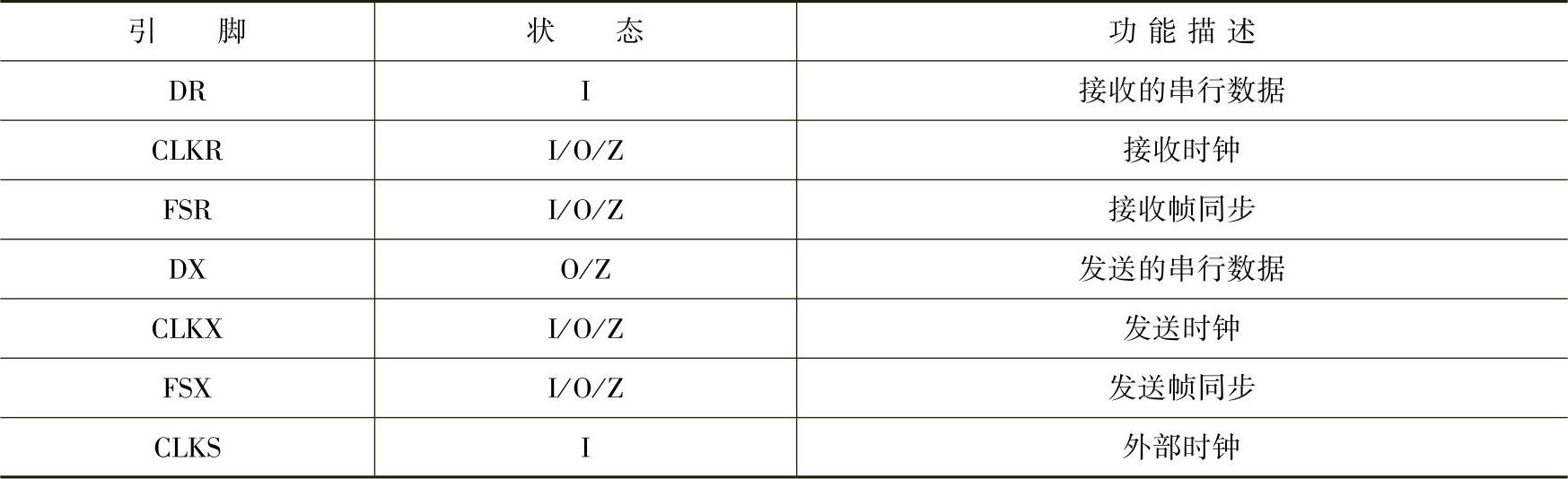

McBSP由和外部器件相连接的一个数据通道和一个控制通道组成,表4-22给出了有关引脚的信号定义。

图4-13 McBSP的结构

(https://www.xing528.com)

(https://www.xing528.com)

图4-14 McBSP的内部结构

表4-22 McBSP引脚的信号定义

数据发送(DX)引脚负责数据的发送,数据接收(DR)引脚负责数据的接收,另外5个引脚(CLKS、CLKX、CLKR、FSX和FSR)提供了控制信号(时钟和帧同步)接口。TMS320C6000CPU通过片内的外设总线访问串口的32位控制寄存器,从而实现与McBSP间的通信与控制。非32位的写访问控制寄存器会破坏寄存器的值,但是非32位的读访问能返回正确的值。

CPU或DMA控制器向数据发送寄存器(DXR)中写入待发送的数据,从数据接收寄存器(DRR)读取接收到的数据。写入DXR的数据通过发送移位寄存器(XSR)移位输出到DX引脚。同样,DR引脚上接收到的数据先移位进入接收转移寄存器(RSR)中,然后被复制到接收缓冲寄存器(RBR)中。最后RBR被复制到DRR中,CPU或DMA控制器可以将数据读取。这种多级缓冲方式使得片内的数据移动和外部数据的通信可以同时进行。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。