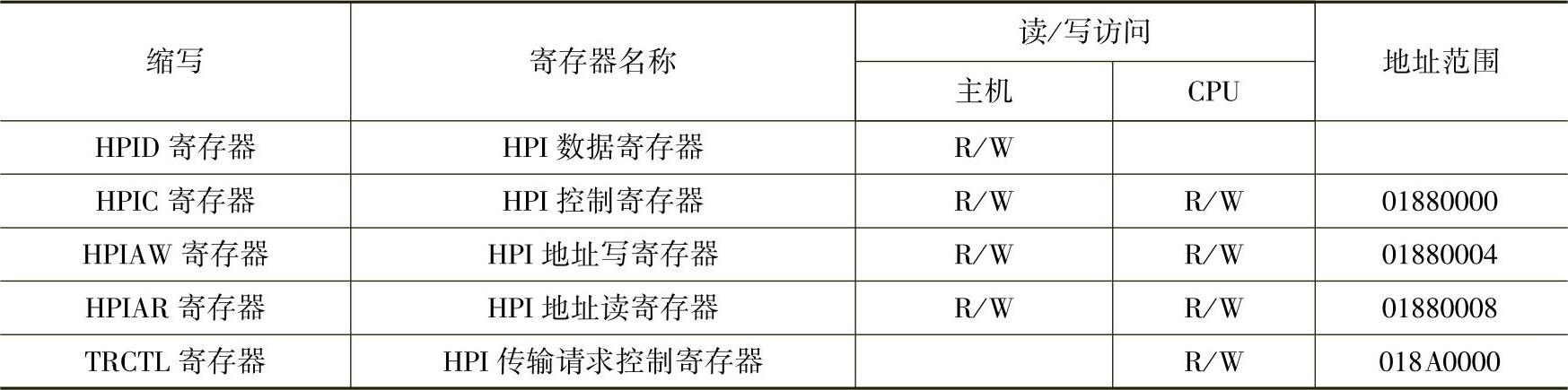

表4-19分别列出了TMS320C64x DSP的HPI寄存器。通过这些寄存器,可以实现主机器件和CPU之间的通信。

表4-19 TMS320C64x DSP的HPI寄存器

1.HPI数据(HPID)寄存器

当前访问是读操作时,HPID寄存器包含有HPI从存储器读取的数据;当前访问是写操作时,HPID包含的是将要写入存储器的数据。

2.HPI控制(HPIC)寄存器

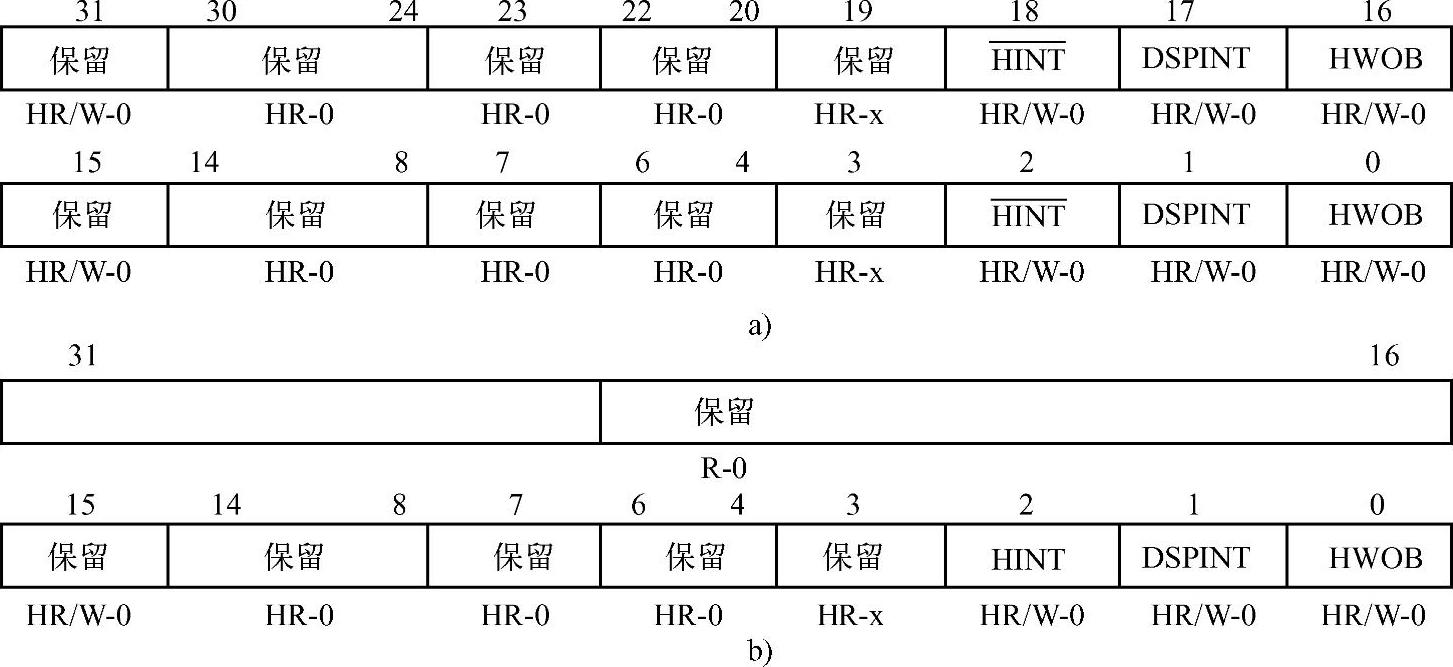

为了设置配置位并初始化接口,HPIC寄存器通常是第一个访问的寄存器。TMS320C6000DSP的HPIC寄存器分别如图4-8所示,其各位段的描述见表4-20。

图4-8 HPIC寄存器

表4-20 HPIC寄存器各位段的描述

注:①仅对C620X/C670X有效。

图4-8a是从主机端看,HPIC是一个32位的寄存器,其高16位和低16位是一样的,分别表示高位半字和低位半字内容。当一次主机写时,除了HPI16模式下写DSPINT位以外,两个半字必须是一样的。在HPI16模式下,当设置DSPINT=1时,主机必须向低16位半字或高16位半字写(但不能同时写)1。在TMS320C64x DSP的HPI16模式下,第一个半字写时DSPINT的值被锁存;第二个半字写时DSPINT位必须清除为0。在HPI32模式下,高半字和低半字必须一致。图4-8b是从DSP端看,HPIC是一个32位寄存器,但是只有16位有用,所以仅当CPU向低位半字写操作影响HPIC的值和HPI操作。

对于TMS320C64xDSP,由于CPU可以写HWOB位,因此,在对HPIC进行写操作时,必须注意不可向HWOB写入不期望的值。

对于TMS320C64xDSP,由于CPU可以写HWOB位,因此,在对HPIC进行写操作时,必须注意不可向HWOB写入不期望的值。

3.HPI地址(HPIA)寄存器

HPIA寄存器包含了HPI所访问的存储器地址。该地址是一个32位的字,所有32位是可读/写的。无论从HPIA的位置读取的值是多少,最低两位总是为0。

TMS320C64x HPIA寄存器既可以被主机所访问,也可以被CPU访问。TMS320C64x HPIA寄存器在内部分为两个寄存器———HPI地址写(HPIAW)寄存器和HPI地址读(HPIAR)寄存器,CPU可以独立地更新读和写存储器地址,以允许主机对不同地址范围执行读和写。

当从CPU读HPIA寄存器时,返回的值和当前HPI和DMA在DSP内部传输数据所使用的地址相关。对于一次HPI写,HPIAR寄存器中为传输的起始地址,而HPIAW寄存器包含了当前被使用的地址并且在传输的每次数据突发后更新。对于一次HPI读,HPIAW寄存器包含了传输的起始地址,而HPIAR寄存器包含了当前被使用的地址并且在传输的每次数据突发后更新。HPIA寄存器并不包含外部引脚上的当前传输的地址,所以读HPIA寄存器不能表示一个传输的状态。

HCNTL[1∶0]控制位设置为01b,表示一个对HPIA寄存器的访问。一次主机写HPIA寄存器在内部更新HPIAW寄存器和HPIAR寄存器。一次主机读HPIA返回最近使用的HPI-Ax寄存器中的值。例如,最近HPID寄存器访问是一次读,则外部主机的一次HPIA寄存器写返回HPIAR寄存器中的值;如果最近HPID寄存器访问是一次写,则外部主机的一次HPIA寄存器写返回HPIAW寄存器中的值。(https://www.xing528.com)

通过CPU内部更新,HPIAR/HPIAW寄存器的系统不允许通过外部总线更新HPIA寄存器,同样,通过外部主机更新HPIAR/HPIAW寄存器的系统不允许CPU更新HPIA。HPI-AR/HPIAW寄存器可以独立地被CPU和外部主机所读取。当DSP正在更新HPIAR/HPIAW寄存器时,系统不允许外部主机访问HPID寄存器。这可以通过任何方便的方式进行控制,包括使用通用目标输入/输出(GPIO)引脚来执行主机和DSP之间的传输。

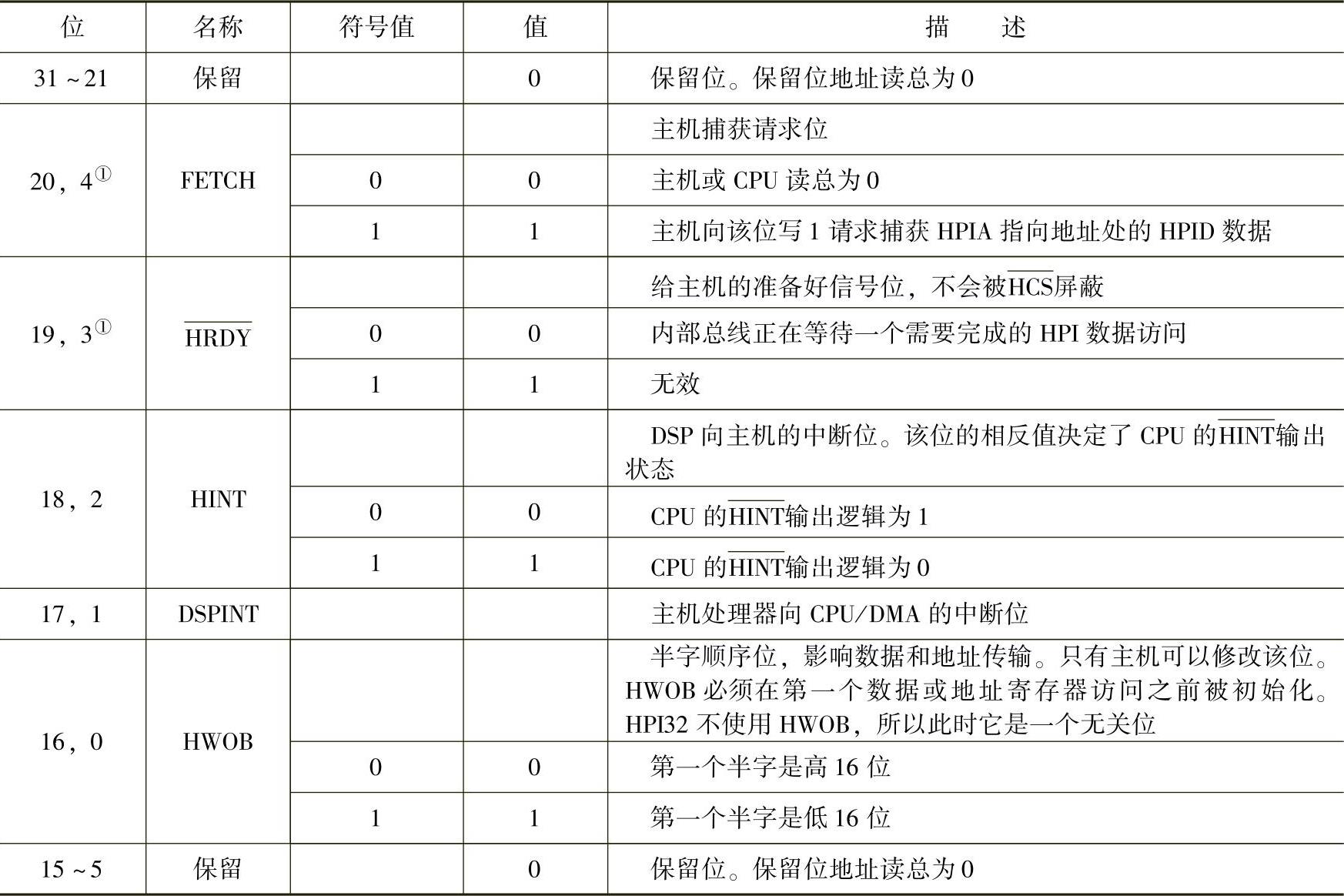

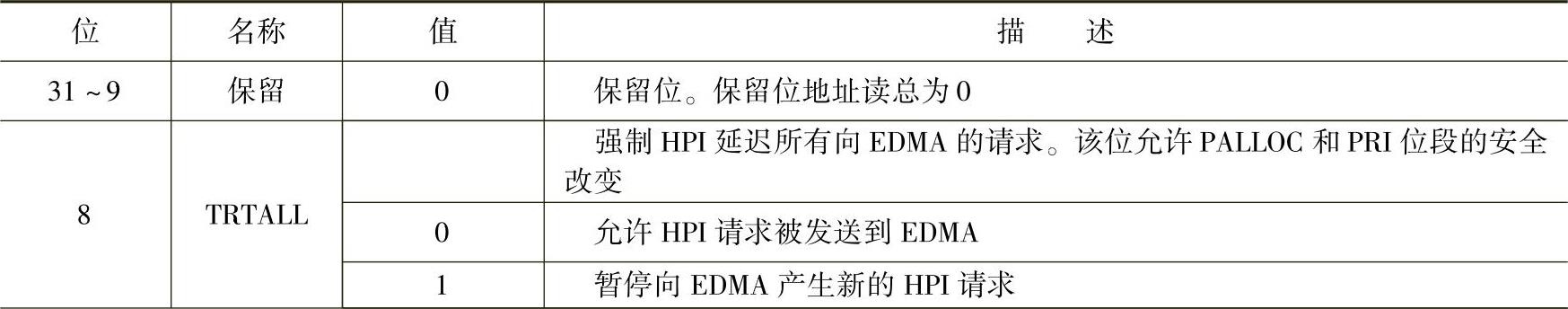

4.HPI传输请求控制(TRCTL)寄存器

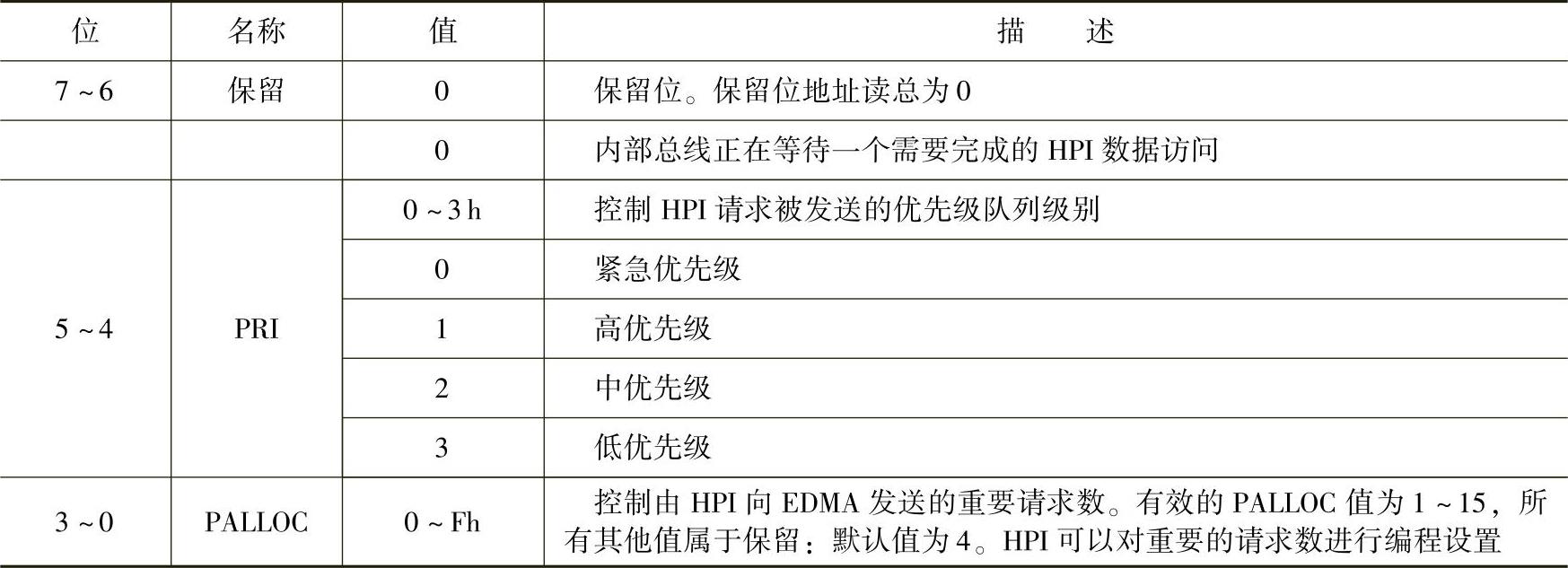

TMS320C64x DSP的HPI传输请求控制寄存器控制HPI如何发送它的请求到EDMA子系统。TRCTL寄存器如图4-9所示,其位段的描述见表4-21。

图4-9 TRCTL寄存器

表4-21 TRCTL寄存器的位段描述

(续)

为了安全地改变TRCTL寄存器的PALLOC或PRI位,需要使用TRSTALL位以确保正确变换。修改PALLOC或PRI位应该遵循下面的操作程序。

1)设置TRSTALL位为1,防止HPI以当前的PRI优先级发送TR请求。此时,可以指定期望的新PALLOC或PRI位。

2)清除所有与原来的和新的PRI优先级相关的EDMA事件使能(EER),防止EDMA发送新旧PRI级的TR请求。

3)不要对新旧PRI优先级发送新的QDMA请求。

4)停止新旧PRI优先级的L2缓存缺失(Cache Miss)。这可以通过强制程序执行或内部存储器的数据访问来实现。另一种方法是使CPU执行一个不会产生额外的缓存缺失的紧凑循环(Fight Loop)。

5)在EDMA的优先级队列状态寄存器(PQSR)查询PQ位,直到两个队列均为空。

6)清除TRSTALL位为0,允许HPI继续执行普通的操作。

当旧的HPI PRI优先级的请求方被终止时,才能够保留存储器排序。在这种情况下,在HPI从延迟状态释放之前,所有与旧的PRI优先级相关的挂起的请求必须完成。

当新的PRI优先级的请求方被终止时,才能确保任何时候所有请求方分配的总量不会超过队列长度。通过停止一个指定优先级的所有请求方,用户可以自由修改每个请求方的队列配置计数器。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。