1.请求链

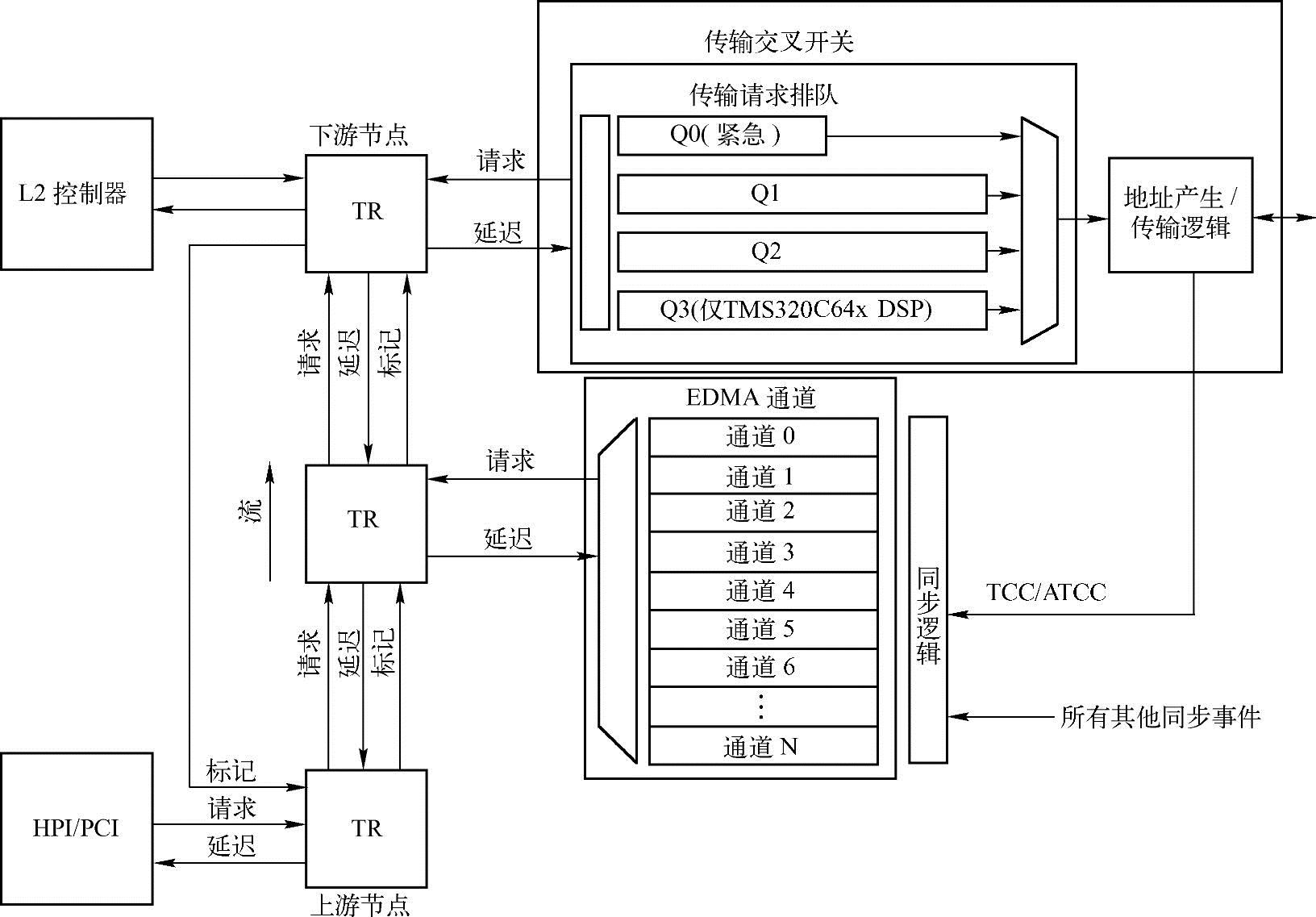

所有EDMA的传输请求方都连接到传输请求链,如图3-19所示。一个传输请求一旦被发送,它会通过请求链移到传输交叉开关(TC),然后在TC处确定优先级并处理。传输请求可以是单个数据单元或多个数据单元。

请求链为请求方提供了一个内在的优先计划。假设每个请求方在相同周期内产生一个请求,则离TC最近的请求方(下游请求方)首先到达,最远的(上游请求方)最后到达。若请求已在请求链中,则其优先级就比新的请求高,因此不用担心的它的服务响应。

为防止上游请求方的连续发送请求拖延下游请求方的发送,系统提供了一个链逻辑循环方案。在每个EDMA时钟周期,一个发送请求标记被传送到下游方向的链附近(标记是一个环)。具有标记的传输请求节点会使它的两个请求方的优先级倒置,不是把优先权给了位于上游节点链中存在的请求,而是给了具有发送新请求标记的本地请求方。尽管这是一个内置于EDMA中的保障机制,但与发送请求速度相关的EDMA高带宽仍表明这是不合理的。EDMA请求方包括L2控制器、EDMA通道和HPI/PCI。

(1)L2控制器传输请求

L2控制器为高速缓冲存储器TMS320(Cache)服务发送所有传输请求,用于访问非高速缓冲存储器和QDMA传输。对于TMS320C64x DSP,能以高速缓冲存储器配置寄存器(CCFG)中P位指定的任意优先级执行高速缓存服务请求。对于读操作请求,Cache控制器总是以两个64KB的突发请求一个L2缓存块。对于写操作请求,作为一个回写(Write-back)/回写无效的操作结果,Cache控制器以两个64KB的突发传输一个完整的L2缓存块。

图3-19 EDMA的传输请求框图

(2)HPI/PCI传输请求

HPI/PCI自动产生传输请求以服务主机的活动。对于TMS320C621x/C671x DSP,这些传输请求发送只使用高优先级实现,并且对用户来说是不可视的。对于TMS320C64x DSP,默认情况下HPI/PCI传输请求使用中优先级发送,但是请求优先级可以编程从而获得4种优先级的任一种,使用传输请求控制(TRCTL)寄存器的PRI位段来设置优先级。HPI/PCI为一个单元读或写发送一个传输请求,用于固定模式的主机访问;HPI/PCI也为一个短的数据突发发送一个传输请求,用于自动增量传输。突发大小总是8个或更少的单元。

(3)EDMA通道传输请求

可以使用紧急优先级(仅TMS320C64x DSP)、高优先级、中优先级(仅TMS320C64x DSP)或低优先级发送EDMA通道传输。高优先级为短突发和单个单元数据传输,而低优先级用于更长(后台)的块移动。当实际应用时,建议将传输分成不同的优先级,这样有助于最大化器件的性能。(https://www.xing528.com)

2.传输交叉开关

一旦一个传输请求到达请求链的末端,它就会被送到传输交叉开关(TC)。在TC内,传输请求会移到一个传输队列中等待处理。传输请求被送到的哪个队列由它的相应优先级决定。TMS320C621x/C671x DSP具有3个固定长度的队列(Q0~Q2),而TMS320C64x DSP具有4个优先级队列(Q0~Q3),这些队列长度是可编程序的。

一旦传输请求到达了队列的头部,它就会被送去处理地址产生/传输逻辑,地址产生/传输逻辑仅仅服务来自队列中的传输请求。为了最大化系统的数据传输带宽,应该利用所有队列。

3.地址产生/传输逻辑

如图3-19所示,地址产生/传输逻辑块通过EDMA控制数据的传输。每个优先级队列具有一个寄存器集,可以监测传输的过程。在一个特定队列的寄存器集中,当前源地址、目的地址和计数只用于一个传输。这些寄存器不是存储器映射的,并且CPU不能访问它们。

队列寄存器本质上是一个传统的DMA,它们在数据传输过程中保留传输参数(源地址、目的地址和计数等)。这些队列寄存器为数据传输发送请求。这些请求是用于小于或等于请求传输的总数据量的小突发,实际大小依赖于执行数据读或写的端口,并且由硬件确定以最优化性能,这样就允许不同队列初始化的传输可以同时发生。由于寄存器为数据传输发送请求,所以只要端口准备好了就可以实现实际数据移动。如果不同队列请求不同端口的传输,则传输会同时发生。对于同一端口的传输请求,按优先级执行。

每个队列寄存器集发送它的传输请求到适当的源/目的管道(Pipeline)以初始化一个数据传输。队列寄存器产生3个命令:预写、读和写。在每个EDMA周期,任何一个队列寄存器可以将命令发送到源/目的管道。TC会对每个EDMA周期进行仲裁(每个管道独立进行)以允许源/目的管道中挂起的最高优先级的命令先发送。预写命令会通知目的管道将要接收数据。所有端口具有一个小的缓冲区用来按内部时钟频率接收一个突发数据。一旦目的管道具有空间以容纳接收的数据,它就会送出一个应答到EDMA,表明已经准备好。

在接收到来自目的应答后,就向数据源执行一个读命令。数据以最大的源频率读取并送到EDMA通道单元(Routing Unit),以便将来送到目的管道。一旦通道单元接收到数据,通道单元就会执行一条写命令将数据送到它的目的地址。

由于EDMA能够等待目的准备接收数据,源资源可以被其他传输访问直到目的准备好。这就提供了一个非常好的资源利用率,并且可以称为写驱动整个处理过程。EDMA在一条总线上传送所有命令和写数据到所有源。信息以EDMA的时钟速度传递,并且当多个传输同时发生时,来自多个传输的数据是交错的。只要多个传输(来自不同队列)具有不同的源,则传输可以同时发生。

来自每个源的数据到达专门的“读”总线,这样可以防止竞争并且确保数据以最大的速率读取。一旦数据到达通道单元,最高优先级的数据就从它的“读”总线移动到“写”总线并送到目的地址。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。