EDMA控制器负责向CPU产生传输完成中断。与TMS320C620x/C670x DMA控制器不同(每个DMA通道均具有独立的中断),EDMA只向CPU产生一个中断(EDMA_INT),代表所有16个通道(TMS320C621x/C671x DSP)或64个通道(TMS320C64x DSP)。各种控制寄存器和位段易于EDMA中断的产生。

当为一个EDMA通道设置OPT时,寄存器的TCINT位为1,并且一个特定的传输完成代码(TCC)被提供,则EDMA控制器会设置通道中断挂起寄存器(CIPR)的某一位。对于TMS320C64x:其EDMA具有两个通道中断挂起寄存器,即通道中断挂起低位寄存器(CIPRL)和通道中断挂起高位寄存器(CIPRH)。

编程设置的TCC值指定被置位的CIPR位数,最后向CPU产生EDMA_INT信号。为了实现这些操作,通道中断使能寄存器(CIER)的相应中断使能位应该被置位。对于TMS320C64x,EDMA具有两个通道中断使能寄存器,即通道中断使能低位寄存器(CIERL)和通道中断使能高位寄存器(CIERH)。

为配置任意通道的EDMA(或QDMA请求)中断,进行如下设置:

1)设置CIER的CIEn位为1。

2)设置OPT寄存器的TCINT位为1。

3)设置OPT寄存器的TCC位为n。

CIPR与一个其源为TCC值的中断挂起寄存器是等价的,并且CIER与一个中断使能寄存器类似。注意,如果CIER位被禁止,则当TCINT=1时,通道完成事件仍然保存在CIPR中。一旦CIER位被使能,相应的通道中断将发送到CPU。如果CPU中断(默认为CPU INT8)使能,则执行中断服务程序。

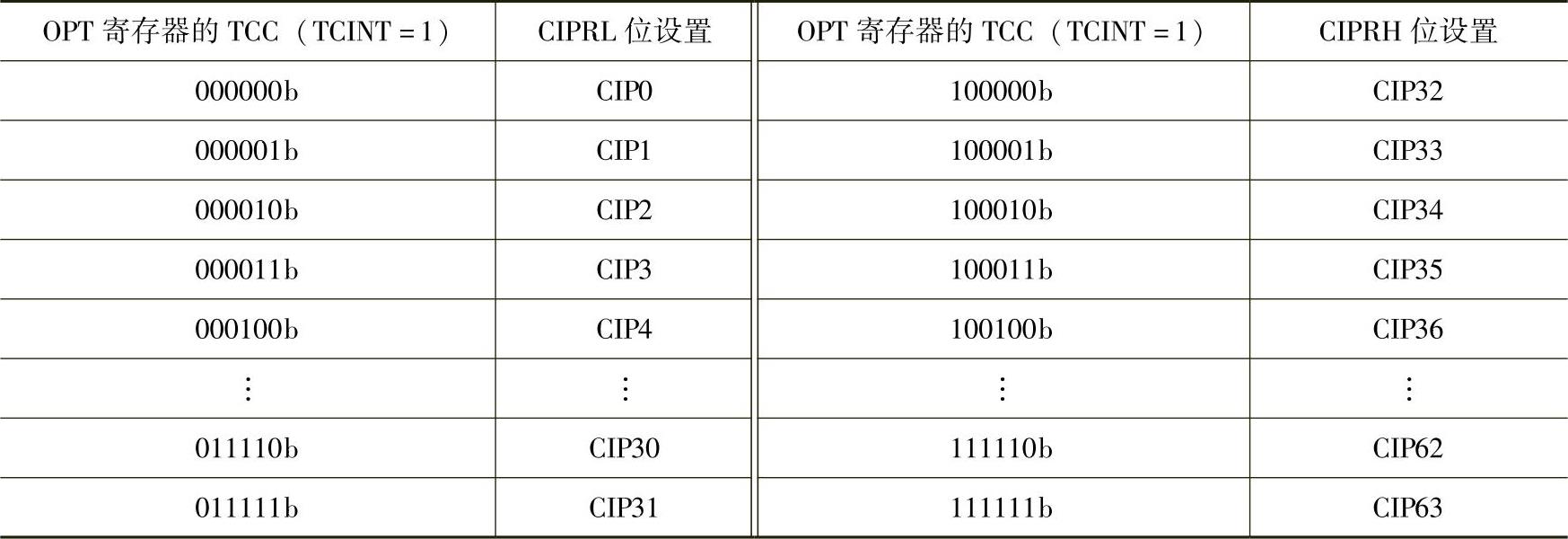

对于TMS320C64x,具有64个通道的EDMA,其传输完成代码扩展为64个通道的6位的值。TMS320C64xEDMA的6位传输完成代码由TCC位和TCCM位组成(传输完成代码的最高位)。传输完成代码直接映射到CIPR位,表3-37为TMS320C64x DSP的传输完成代码(TCC)的EDMA中断映射。例如,如果在传输完成后,TCC=1100b、TCCM=0,CIPRL[12](TMS320C64x DSP)置1,则仅在CIER[12]=1时才会产生一个CPU中断。用户可以编程设置传输完成代码为表3-21中所示的任意值。换句话说,通道号和传输完成代码值之间没有任何直接关系。这就允许多个通道具有相同的传输完成代码,从而使CPI执行相同的中断服务程序(ISR)。也就是说,相同通道可以根据执行的传输设定多个传输代码。

表3-21 TMS320C64x DSP的传输完成代码(TCC)的EDMA中断映射

(1)CPU的EDMA中断服务(https://www.xing528.com)

EDMA控制器会跟踪EDMA通道传输的完成,它按照指定的传输完成代码设置CIPR的合适位。CPUISR将会读取CIPR,并判断任意事件/通道是否已经完成,并执行那些必要的操作。在服务过程中,ISR会清除CIPR中的位,从而使能进一步中断的识别。写1到CIPR的相关位可以清除CIPR,写0无效果。

在一个中断被服务时,许多其他中断可能已经发生,并且CIPR中的相应位已经被置位,CIPR中的这些位可能需要不同类型的服务。ISR会检查所有挂起的中断并且继续直到所有挂起的中断被服务。

在向CIPR写操作后,如果CIPR和CIER的位逻辑“与”(AND)为非0,则CPU的中断标志寄存器(IFR)的中断标志被设置。这个执行会防止丢失当ISR退出时发生的中断,但是会引起多次进入ISR。因为ISR被写入连续处理和清除每个CIPR位时,而清除CIPR位的写操作设置了额外的IFR,会发生对ISR的额外调用。第二次调用ISR时,CIPR位可以清除为0。如前所述,ISR会读取CIPR,并且确定任何事件/通道是否完成并且执行那些必要操作。为了避免额外的中断,可以在ISR结束时立刻清除所有被处理的CIPR位。

(2)交替传输完成中断(仅TMS320C64x DSP)

除了传输完成中断外,TMS320C64xEDMA允许在一个块中的中间传输完成通道中断,称为交替的传输完成中断。例如,在一个1D数据单元同步传输,可以在每个单元的传输完成时产生交替的传输完成中断。

通道选项参数(OPT)寄存器具有两个新位段,交替传输完成中断(ATCINT)和交替传输完成代码(ATCC)。交替传输中断的功能与传输完成中断的功能类似。与TCC类似,ATCC可以设置范围为0~63的任意值。

为了使能交替传输完成中断,需要对EDMA通道选项参数进行如下配置。

1)设置CIER的CIEn位为1。

2)设置OPT寄存器的ATCINT位为1。

3)设置OPT寄存器的ATCC位为n。

当交替传输完成中断被ATCINT使能时,则在当前通道的每个中间传输完成时会产生一个中断(如CIER被置位,则会送往CPU)。当整个通道传输完成时,只要传输完成中断被ATCINT使能,则产生传输完成中断。交替传输完成中断不会应用于2D帧同步传输,因为在这种模式下没有任何中间传输。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。