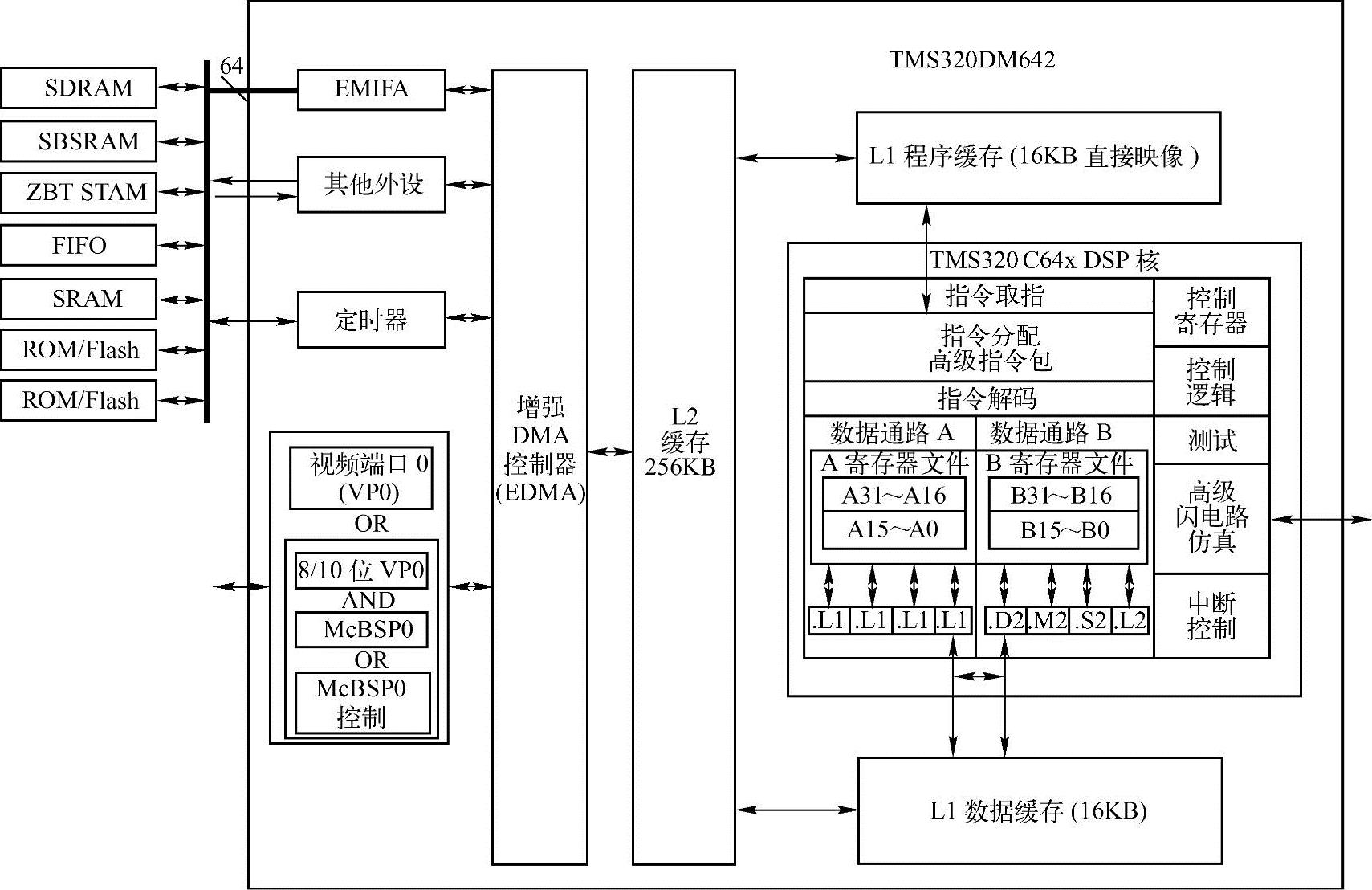

增强的直接存储器访问(EDMA)控制器处理片内L2高速缓冲存储器(Cache)控制器和TMS320C621x/C671x/C64xDSP外设之间的所有数据传输。这些数据传输包括Cache服务、非高速缓冲存储器访问、用户编程的数据传输和主机访问。图3-16为具有EDMA的TMS320DM642的方块图。

图3-16 具有EDMA的TMS320DM642的方块图

EDMA控制器在L2内存空间和片内外设传输数据。EDMA控制器主要由两个部分———传输控制器(EDMATC)和通道控制器(EDMACC)组成。所有的数据传输,包括内存和EMIF的数据传输、非L2内存之间及主机和内存之间,均由传输控制器完成。传输控制对于用户是不可编程序的,而通道控制器具有高度可编程序性,用户可以设置各种传输方式,包括一维或者二维数据传输,以及事件、链或者CPU同步事件触发传输,支持地址重载,支持乒乓寻址、循环寻址、帧提取及排序等。

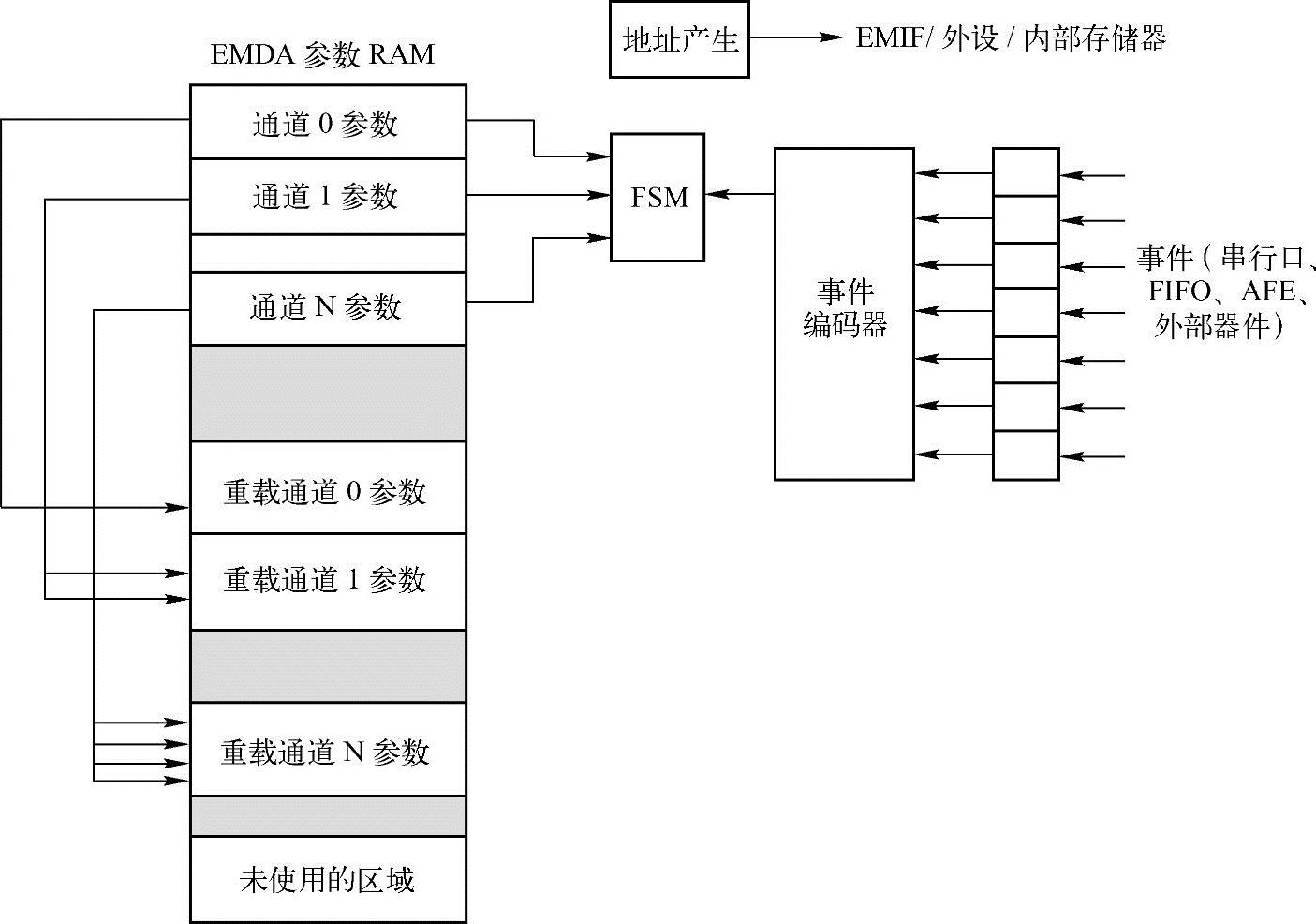

如图3-17所示为EDMA控制器的结构框图。

图3-17 EDMA控制器的结构框图

EDMA控制器由以下几部分组成:

1)事件和中断处理寄存器。

2)事件编码器。

3)参数RAM。

4)地址产生硬件。

5)事件结束检测器。

事件寄存器完成对EDMA事件的捕获。一个事件相当于一个同步信号,由它触发一个EDMA通道以便开始数据传输。如果有多个事件同时发生,由事件编码器对它们进行识别。在EDMA的参数RAM中存放有与事件相关的传输参数,这些参数被送入地址产生硬件,从而产生对EMIF/外设读写操作所需要的地址。

为方便后面的讲解,先介绍一下EDMA。为了便于对EDMA的说明,首先介绍一些ED- MA传输中的相关术语及其含义。(https://www.xing528.com)

(1)数据单元(Element)的传输

单个数据单元从源地址向目的地址传输,并且每一个数据单元还可以由同步事件触发传输。数据单元传输一般在一维传输中使用。

(2)帧(Frame)

一组数据单元组成一帧,一帧中的数据单元可以是相邻连续存放的,也可以是间隔存放的。帧传输可以受同步事件控制,也可以不受同步事件控制。“帧”一般在一维传输中使用。

(3)阵列(Array)

一组连续的数据单元组成一个阵列。一个阵列中的数据单元不允许间隔存放。“阵列”一般在多维传输中使用。

(4)块(Block)

多帧数据或多个阵列的数据组成一个数据块。块传输的启动可以受同步事件控制,也可以不受同步事件控制。对于一维(1D)传输,一组帧组成一个块;对于二维(2D)传输,一组阵列组成一个块。

(5)一维(1D)传输

多个数据帧组成一个一维的传输块。块中帧的个数(FRMCNT)范围可以是1~65536,每帧中单元数(ELECNT)范围为1~65535,可以同时传输每个单元或整个帧。

(6)二维(2D)传输

多个数据阵列组成一个二维的传输块。第1维是阵列中的数据单元,第2维是阵列的个数。块中阵列的个数范围可以是1~65536,可以同时传输每个阵列或整个块。

快速DMA(QDMA)是TMS320C621x/C671x/C64x中增加的另一个新的功能,QDMA与EDMA的功能非常类似,但是它提供了一种更快速更有效的数据转移手段,尤其适合于需要快速数据传输的应用场合,如紧耦合的循环算法中的数据存取。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。