TMS320DM642芯片内部只集成了256KB的SRAM,一般情况下都不能满足用户需求,需要在外部存储器接口(EMIF)上扩展存储空间。DSP采用大容量的SDRAM作为外部存储器,外部SDRAM结合片内RAM来使用,大大提高系统的性能。SDRAM既可以作为程序存储器,又可以作为数据存储器。当系统上电后,DSP程序通过主机下载到SDRAM中执行,同时暂存数据也可以放在SDRAM中,常用数据可以放在片内RAM中以提高执行效率。

1.硬件电路设计

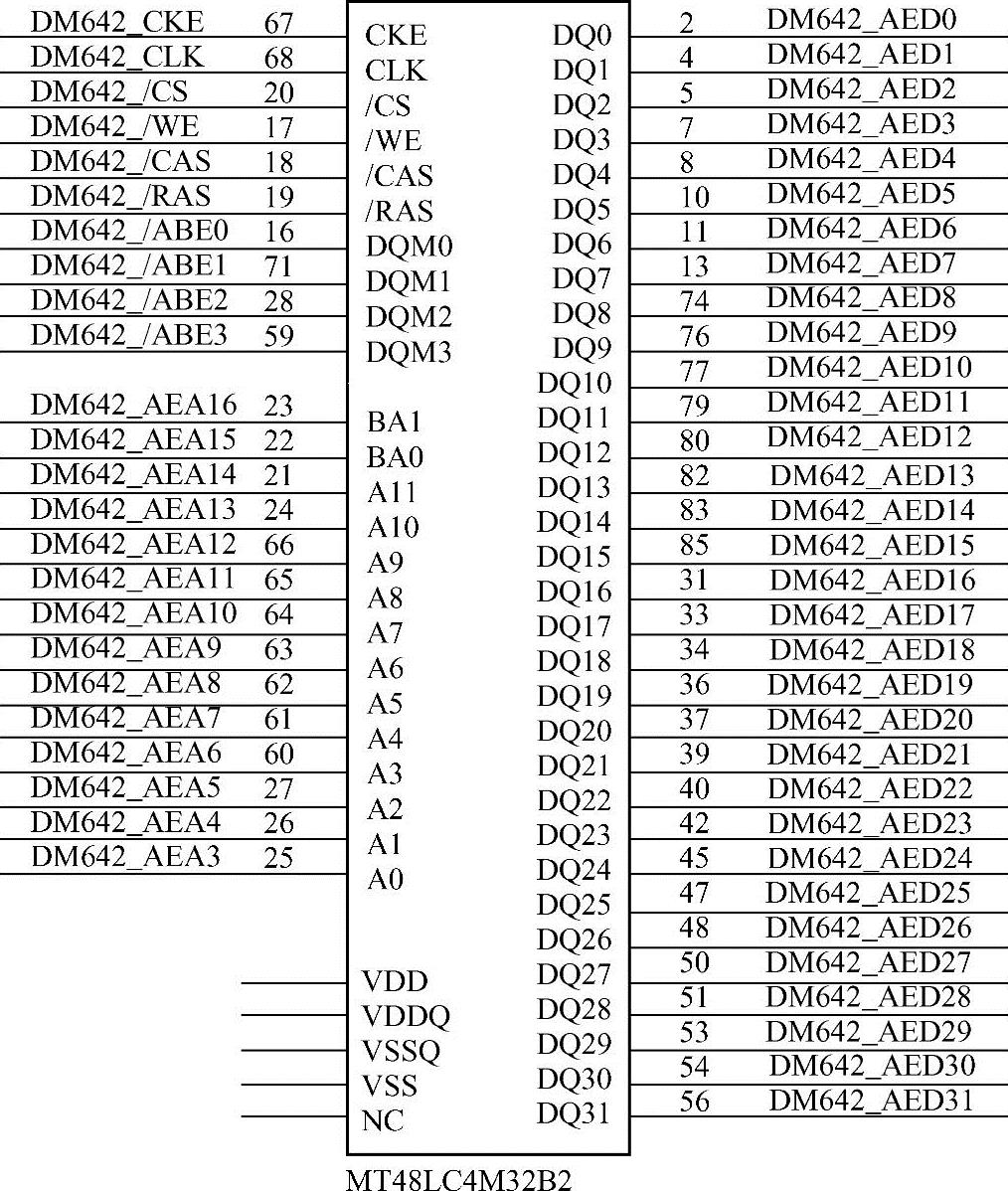

TMS320DM642的EMIF在CE0空间提供了容量为1GB、宽度为64bit的SDRAM接口总线,为了符合64bit的接口,需要采用两片32bit的SDRAM。本系统选用了型号为MT48LC4M32B2的两片32bit的SDRAM芯片在片外扩展了64MB的动态存储空间。其中1片SDRAM与TMS320DM642连接的电路原理图如图3-14所示,地址输入引脚A[0~11]与TMS320DM642的引脚AEA[3~14]相连接。SDRAM的主要控制信号有:BA[1∶0](BANK存储体选择)、CLK(时钟信号)、CKE(时钟使能信号)、/CS(片选使能信号)、/RAS(行地址选通信号)、/CAS(列地址选通信号)、/WE(写使能信号),所有的控制信号都与外部的133MHz时钟同步。BANK地址输入信号引脚BA[0~1]与TMS320DM642的引脚AEA[15~16]相连接。两片SDRAM的数据输入/输出接口DQ[0~31]分别与TMS320DM642的引脚AED[0~31]、AED[32~63]顺序连接。两片SDRAM的字节使能引脚DQM[0~3]分别与TMS320DM642的引脚/ABE[0~3]、/ABE[4~7]顺序连接,其中的DQM0控制DQ[0~7]字节使能,DQM1控制DQ[8~15]字节使能,DQM2控制DQ[16~23]字节使能,DQM3控制DQ[24~31]字节使能。SDRAM的CLK、CKE、/CS、/RAS、/CAS、/WE分别与TMS320DM642的对应引脚相连接。

图3-14 TMS320DM642扩展SDRAM的电路原理图

SDRAM正常工作一般包含以下几个步骤:

1)初始化。SDRAM芯片内部有一个逻辑控制单元,并且有一个模式寄存器为其提供控制参数,分别规定了SDRAM的操作模式、CAS潜伏期、突发传输方式和突发长度。

2)行有效。初始化完成后,要对一个BANK中的阵列进行寻址,首先要进行行激活操作,然后再确定列,虽然之前要进行片选和BANK定址,但它们可以和行有效同时进行。

3)列寻址。行地址确定之后,就要确定列地址,行地址和列地址的地址线是复用的,可以通过/CAS来确定和区分行地址和列地址,另外还需根据/WE确定读/写命令,高为读,低为写,列寻址信号和读/写命令是同时发出的。

4)数据输出。在选定列地址后,就已经确定了具体的存储单元,接下来就是数据通过DQ数据线传输的执行了。数据输出一般会滞后/CAS命令2~3个时钟周期,这段时间被叫做CAS潜伏期。

5)数据写入。数据写入也是在列寻址后进行的,TMS320DM642在列寻址的同时可以同时对SDRAM进行写操作,此时/WE为低。(https://www.xing528.com)

6)刷新操作。动态存储器都存在刷新问题,否则会造成存储的数据丢失,当TMS320DM642的ASDCKE为低电平时,SDRAM进行自刷新。

制作PCB时,两片SDRAM的布线拓扑最好采用T形分支结构,且走线的分支点应靠近TMS320DM642,这样可以降低传输线上的信号反射。

制作PCB时,两片SDRAM的布线拓扑最好采用T形分支结构,且走线的分支点应靠近TMS320DM642,这样可以降低传输线上的信号反射。

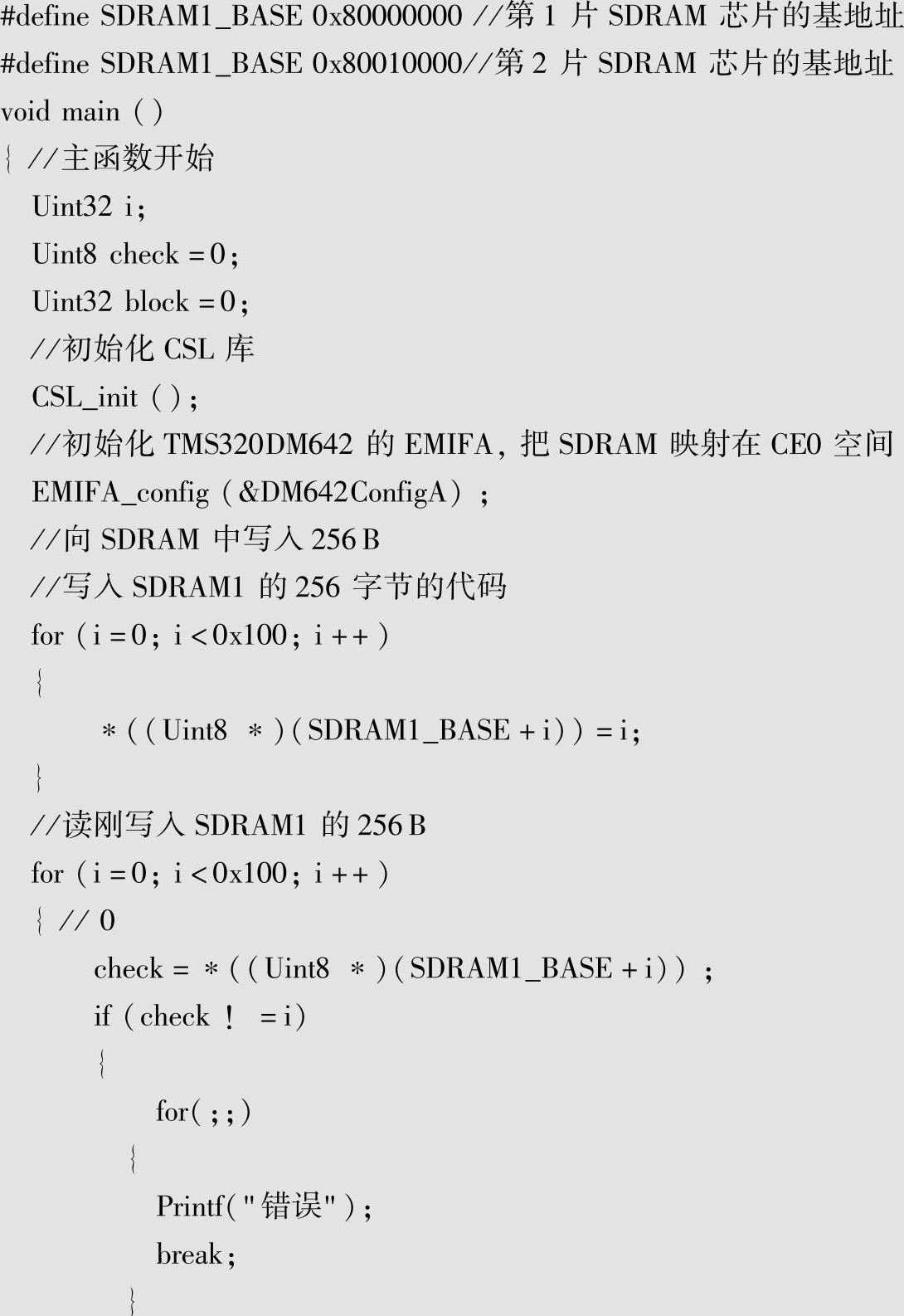

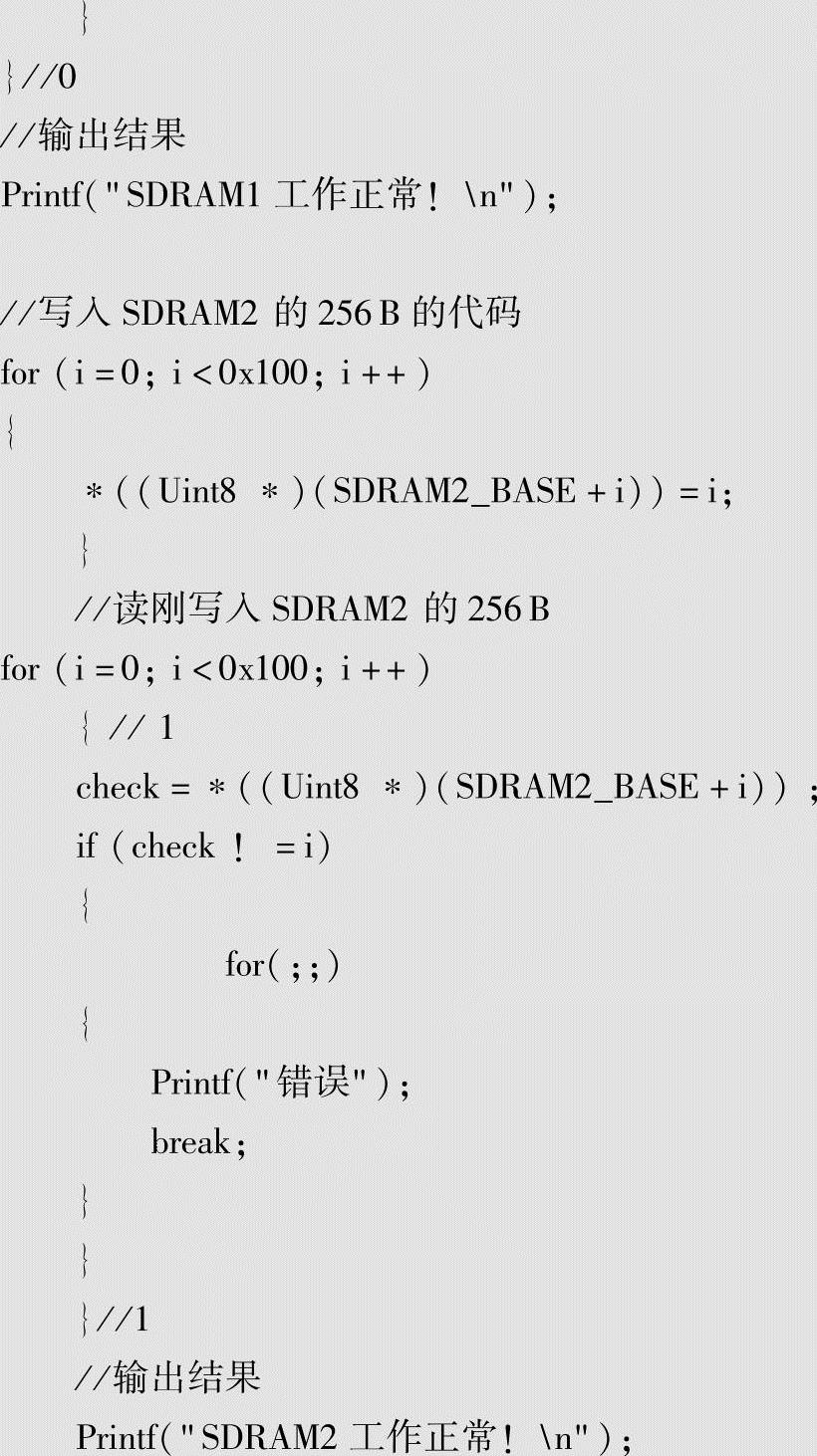

2.SDRAM读/写程序

【例3-1】 第1片SDRAM芯片的基地址为0x80000000,第2片SDRAM芯片的基地址为0x80010000,编写程序对两片SDRAM芯片进行检测。

设计分析

在main.c文件中定义SDRAM的基地址和编写主要程序代码,利用CSL库函数和EMI-FA_Config结构配置TMS320DM642的EMIFA,然后分别向两片SDRAM芯片中写入一些测试数据,然后读出这些测试数据,将读出数据与写入数据进行对比,如果一致则说明SDRAM存储器工作正常。

程序代码

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。