SBSRAM是一种同步突发式静态存储器,由于是静态RAM,不需要刷新,其最大的优点在于读写速度快。EMIF提供了标准的SBSRAM的支持,可以方便地与32位宽度的SB-SRAM连接。对于TMS320C64x系列的DSP,SBSRAM接口速度既可为ECLKOUT1时钟频率,又可为ECLKOUT2时钟频率。

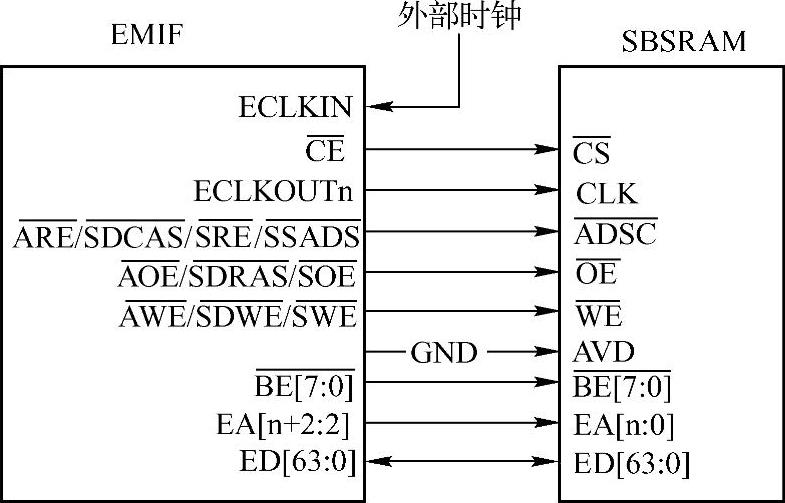

TMS32064x系列DSP的EMIF与64位SBSRAM的连接如图3-11所示。

图3-11 EMIF与64位SBSRAM连接

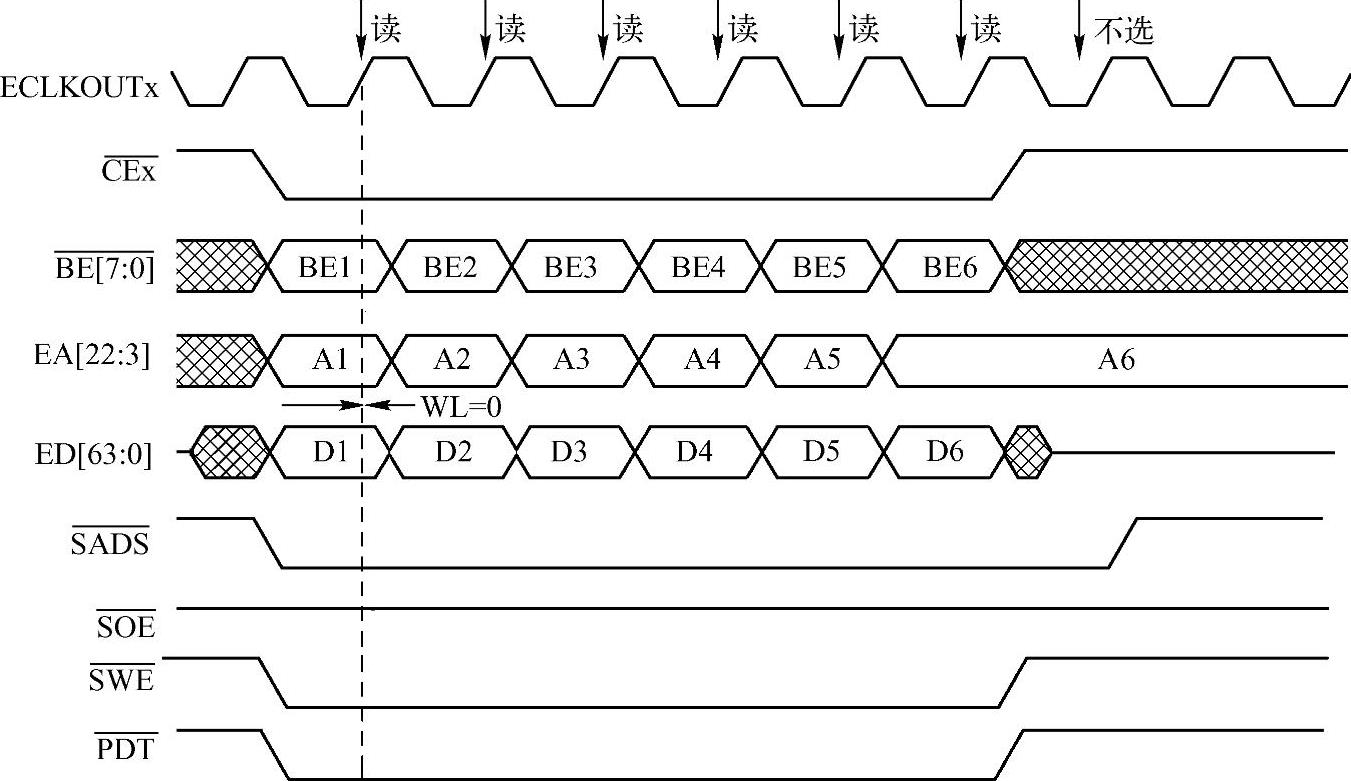

EMIF与64位SBSRAM的连接引脚功能说明见表3-13。

表3-13 EMIF与64位SBSRAM的连接引脚功能说明

在TMS320C64xEMIF中,不支持SBSRAM的突发脉冲特性。一个地址在每个周期被选通到SBSRAM,执行一次读或写命令后,如果CE空间没有存取访问正处于挂起,则TMS320C64xEMIF会对SBSRAM声明一个取消选择命令。EMIF也支持可编程序的读和写等待,以便允许对不同类型的同步存储器的接口。

对于SBSRAM,为了判断当前是何种操作,当片选信号有效时,SBSRAM在时钟的上升沿将锁存其他4个控制信号。为了加快存取过程,SBSRAM器件自身的信号允许器件内部产生突发地址,从而协助不能快速提供存取地址的控制器产生地址。

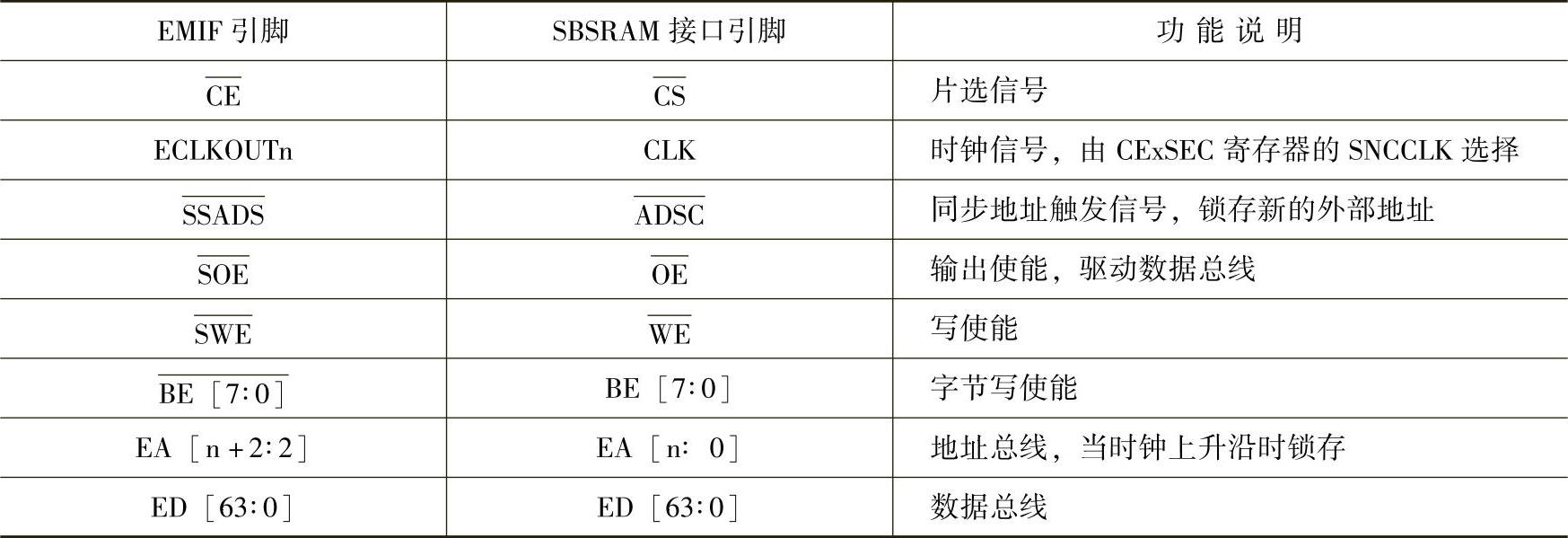

1.SBSRAM读操作

如图3-12所示为TMS320C64xEMIF的一个SBSRAM的6单元(对于EMIFA为双字,EMIFB为半字)读操作。对于TMS320C64xEMIF,该读操作具有两个周期的读等待时间。每次存取访问选通一个新地址到SBSRAM,由 选通为低电平表示。在脉冲传输结束时,EMIF声明一个取消选择周期。

选通为低电平表示。在脉冲传输结束时,EMIF声明一个取消选择周期。

对于标准的SBSRAM接口,CESEC寄存器中的下面段位必须置于它们的默认状态:(https://www.xing528.com)

1)SYNCRL=10b,表示2周期的读等待时间。

图3-12 TMS320C64x EMIF的一个SBSRAM的6单元读操作时序

2)SYNCWL=00b,表示0周期的写等待时间。

3)CEEXT=0,表示在最后一个命令被发布后,CE进入无效状态。

4)RENEN=0, 用做

用做 信号。

信号。

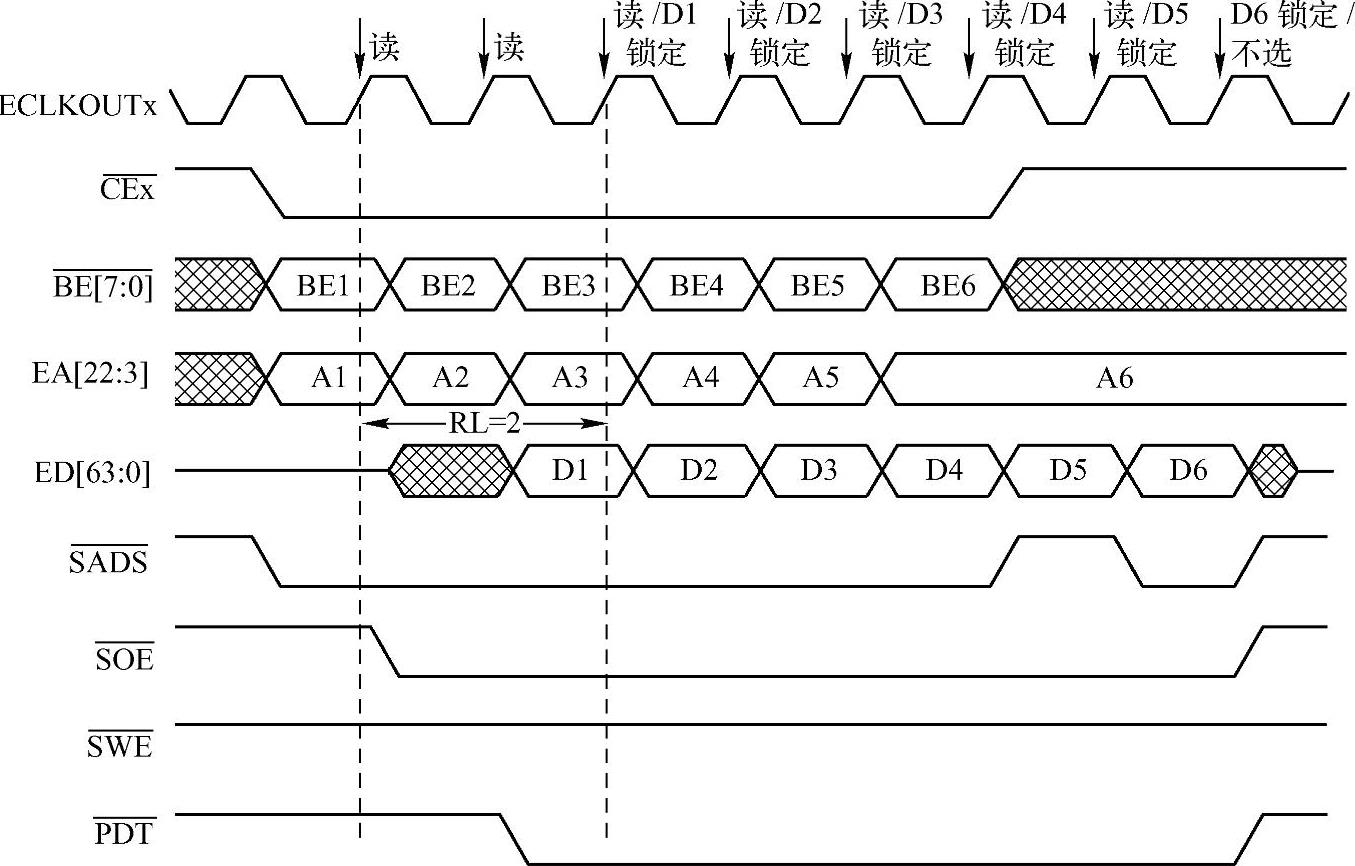

2.SBSRAM写操作

如图3-13所示为TMS320C64x EMIF的一个SBSRAM的6单元(对于EMIFA为双字,EMIFB为半字)写操作。每次存取访问选通一个新地址到SBSRAM。在脉冲传输结束时,EMIF声明一个取消选择周期。对于标准的SBSRAM接口,CESEC寄存器中的下面段位必须置于它们的默认状态:SYNCRL=10b、SYNCWL=00b、CEEXT=0和RENEN=0。

图3-13 TMS320C64x EMIF的一个SBSRAM的6单元写操作时序

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。