通过设置EMIF寄存器,可完成对EMIF的控制,包括配置各个空间的存储器类型、设置相应的接口时序等。TMS320DM642的EMIF寄存器缩写及地址见表3-2。

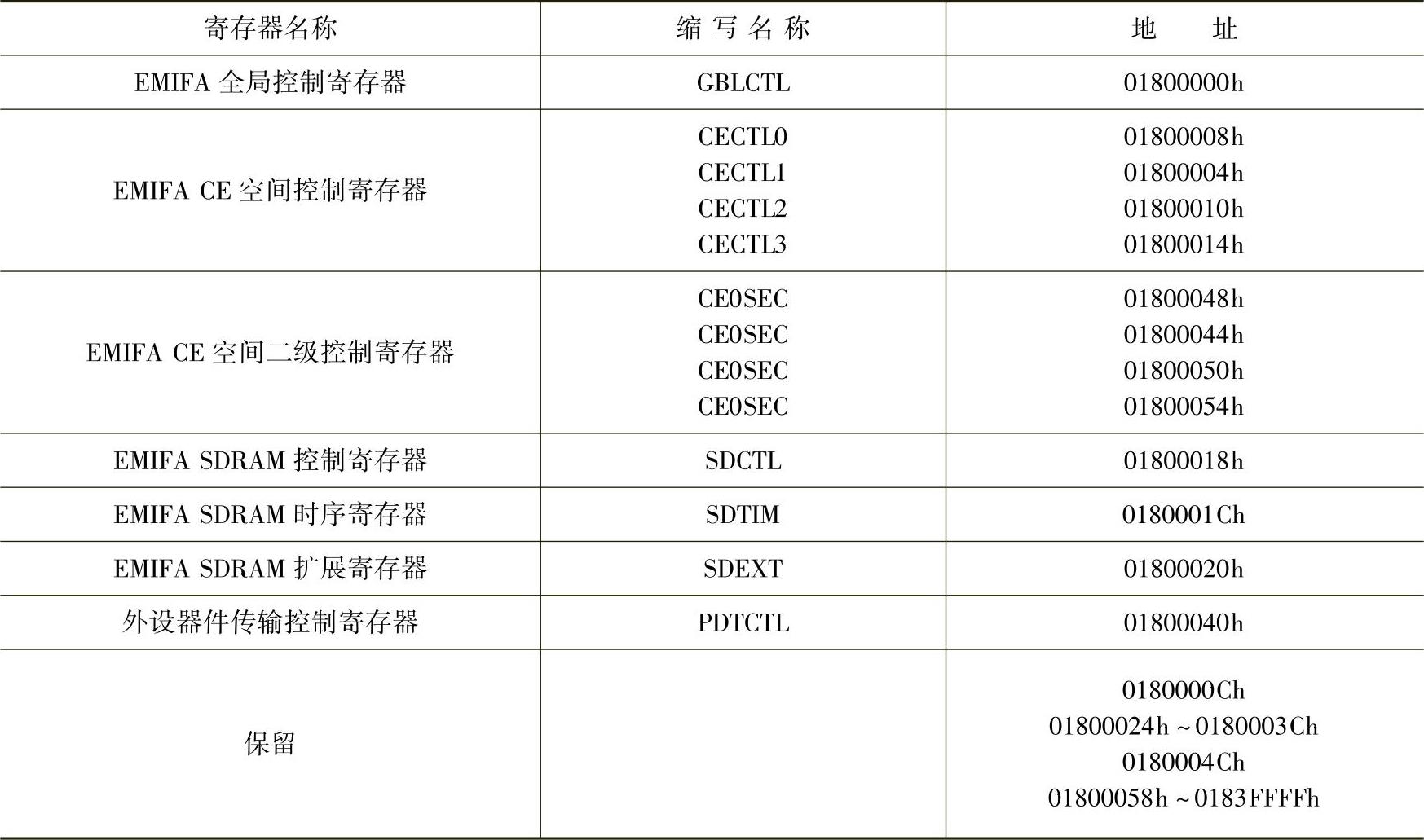

表3-2 TMS320DM642的EMIF寄存器缩写及地址

1.EMIFA全局控制寄存器

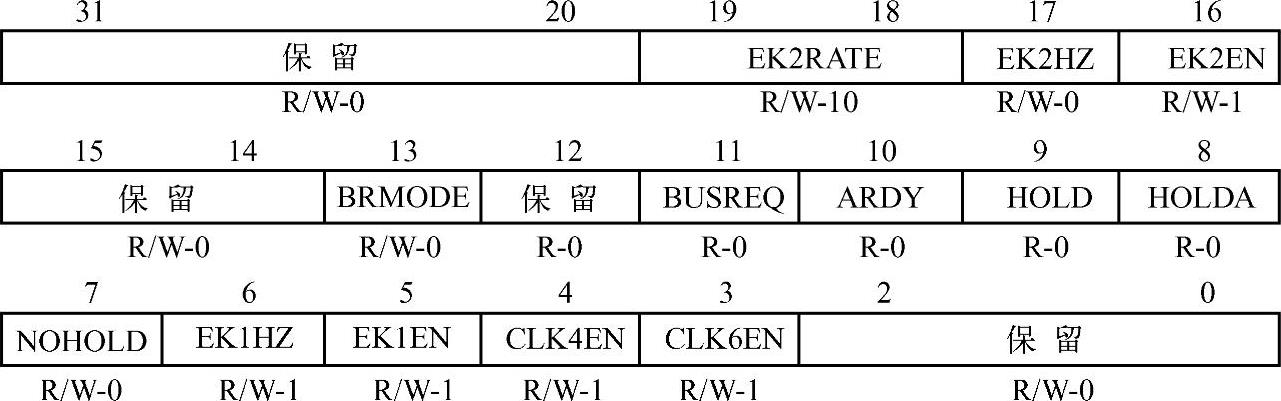

EMIFA全局控制寄存器(EMIFA Global Control Register)简称GBLCTL,可通过该寄存器配置空间的所有参数。GBLCTL寄存器的结构如图3-2所示。

图3-2 EMIFA全局控制寄存器(GBLCTL)

说明:R/W=读/写; R=只读; -n=复位后确定的值; -x=复位后不确定的值

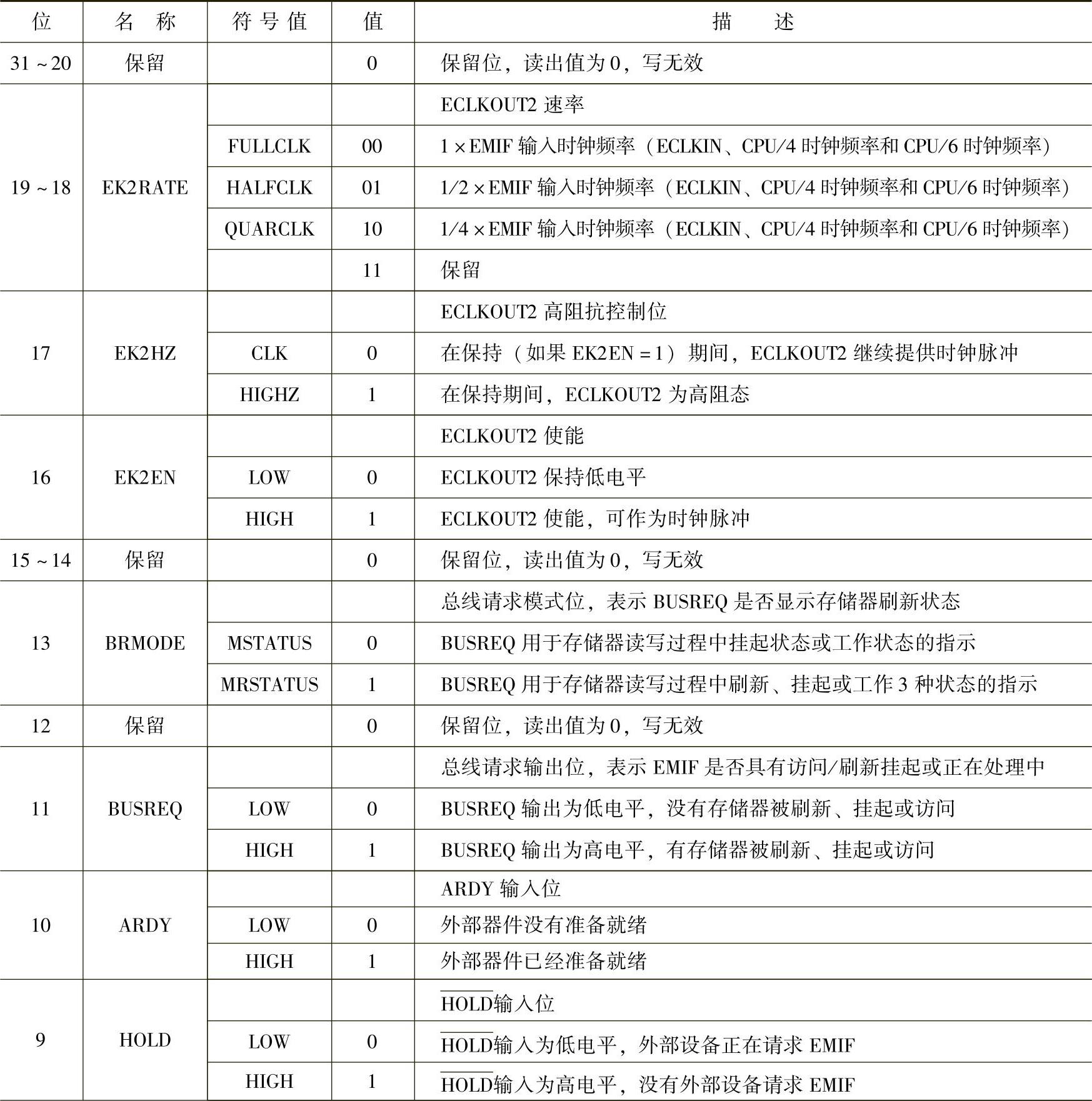

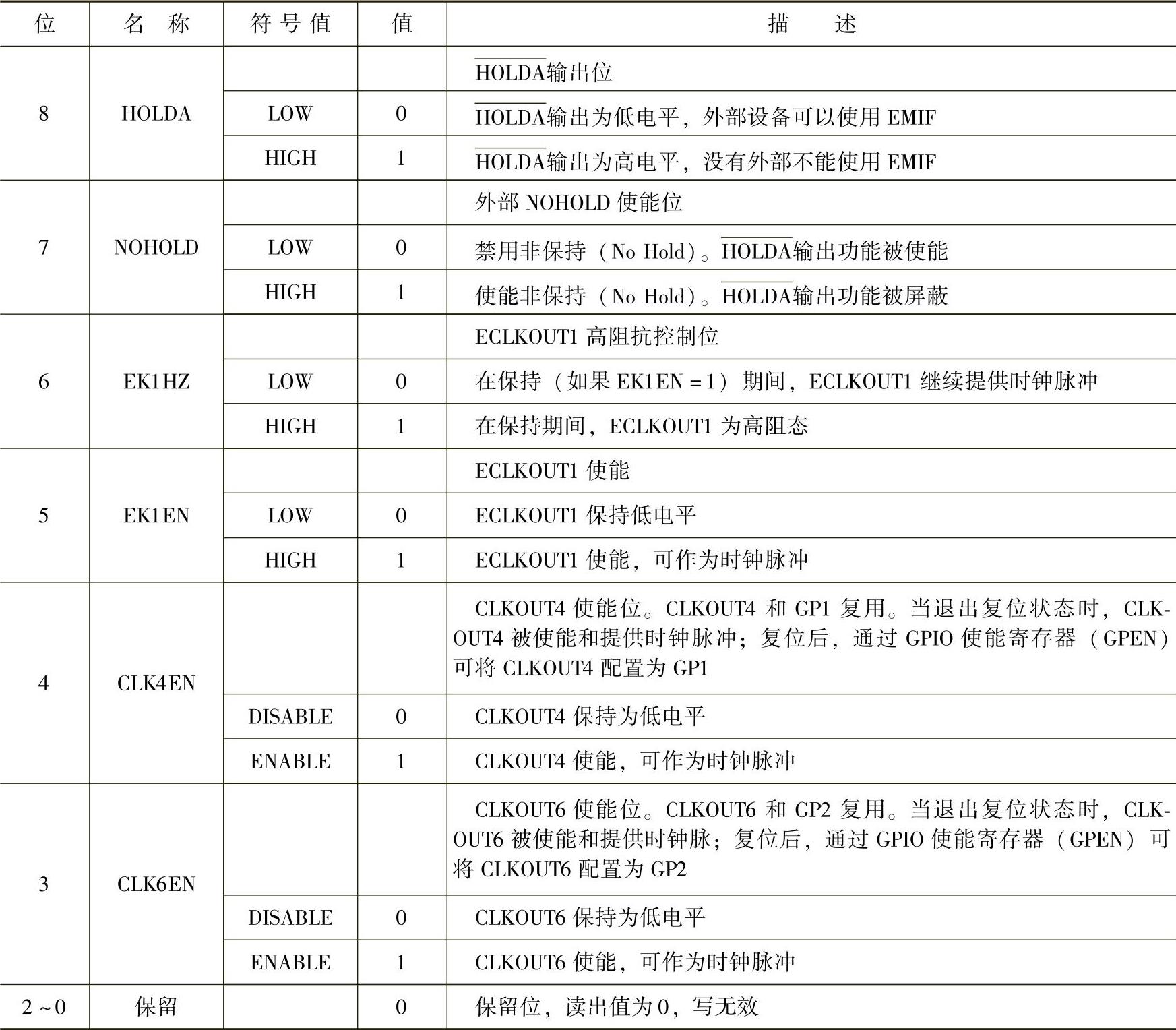

GBLCTL寄存器各段位的详细描述说明见表3-3。

表3-3 GBLCTL寄存器各段位的详细描述说明

(续)

2.EMIFACE空间控制寄存器

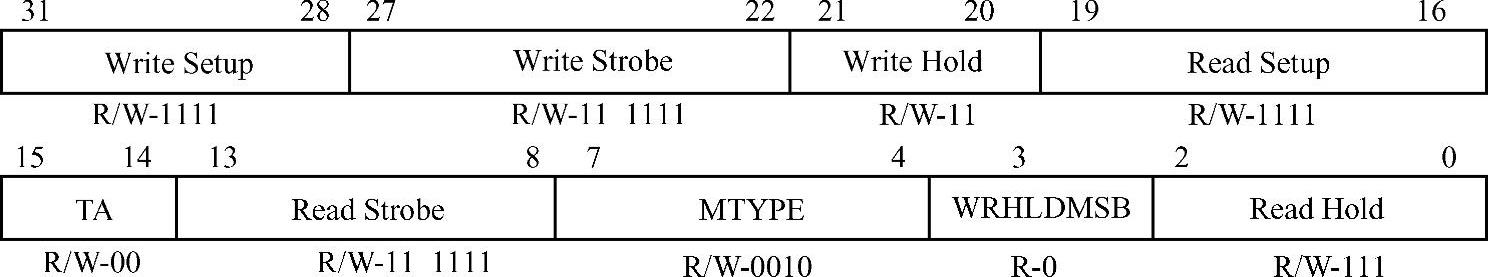

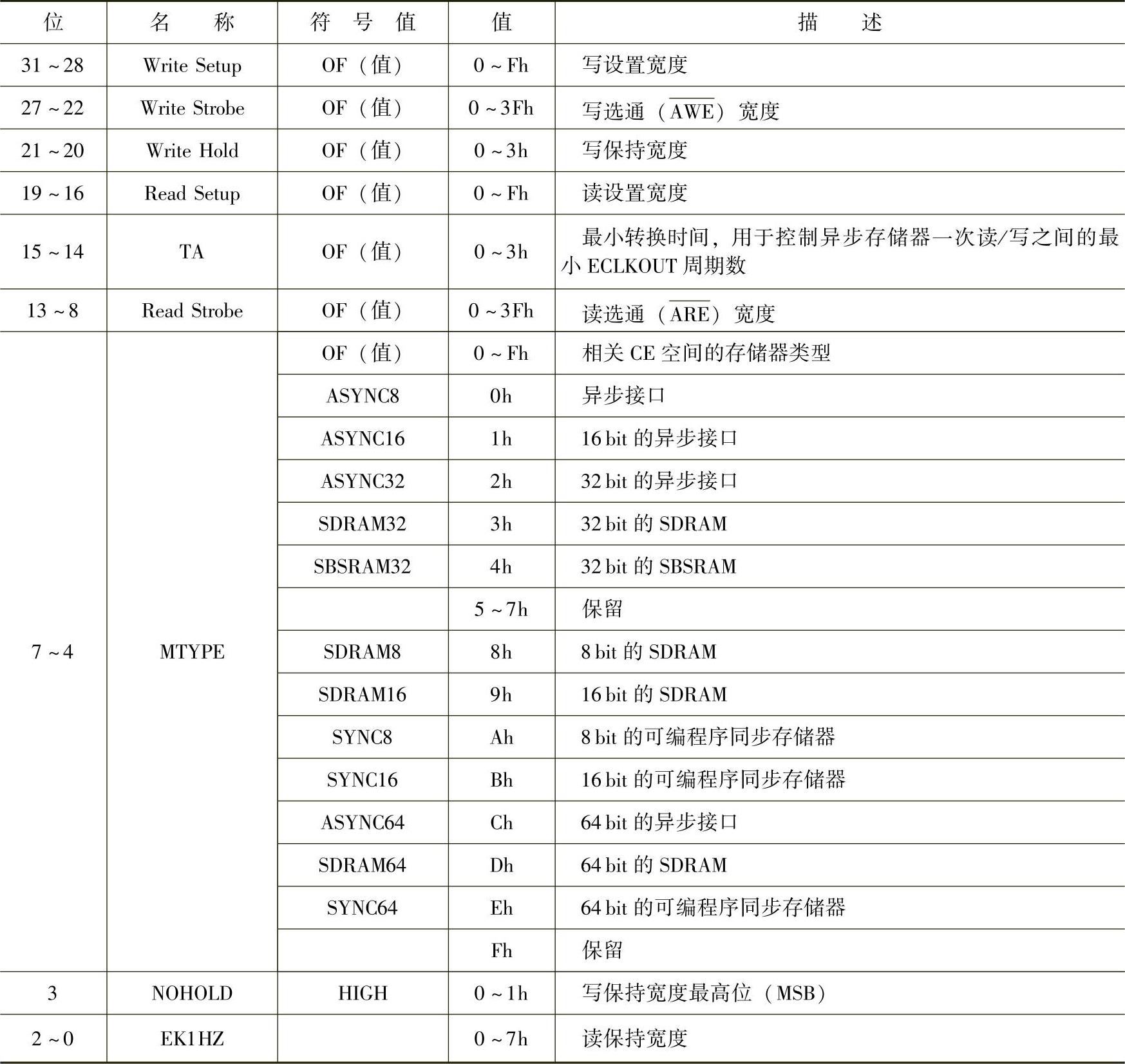

TMS320DM642具有与4个外部CE信号相关的4个CE空间控制(CECTL0~CECTL3)寄存器。CECTL0~CECTL3寄存器是EMIFA的CE空间控制器(EMIFA CE Space Control Registers),该寄存器控制CE空间对外设的读写建立、选通和保持时间参数以及外设类型的选择等。CECTL0~CECTL3寄存器的结构如图3-3所示。

MTYPE段位为相应的CE空间识别存储器类型。如果MTYPE段位选择了一个异步存储器类型,则其余的寄存器段位为访问该存储器空间指定地址和控制信号的信息。如果MTYPE段位选择了一个同步存储器类型,则其余的寄存器段位无效。

在系统初始化期间,MTYPE段位只能设置一次(当CE1用于ROM自举模式时除外)。在自举模式下,CE空间可以配置为另一个异步存储器类型。

由于同步存储器支持SDRAM后台刷新,并且它们共享同步存储器控制信号,在SDRAM刷新期间,DSP不能很好地提供刷新时钟给不同的外设存储器类型,故而一个系统只支持一个同步存储器类型。

由于同步存储器支持SDRAM后台刷新,并且它们共享同步存储器控制信号,在SDRAM刷新期间,DSP不能很好地提供刷新时钟给不同的外设存储器类型,故而一个系统只支持一个同步存储器类型。

在进行软件程序编写时,必须确保当一个CE空间位被设置为一个同步存储器类型时,没有其他CE空间设置为一个不同的同步存储器类型。例如,如果一个CE空间设置为SDRAM,则其他CE空间不应该设置为SBSRAM。同样,如果CE空间设置为SBSRAM,则其他CE空间不能设置为SDRAM。

图3-3 EMIFACE空间控制(CECTL0~CECTL3)寄存器

CECTL0~CECTL3寄存器各段位的详细描述说明见表3-4。

表3-4 CECTL0~CECTL3寄存器各段位的详细描述说明

3.EMIFACE空间二级控制寄存器

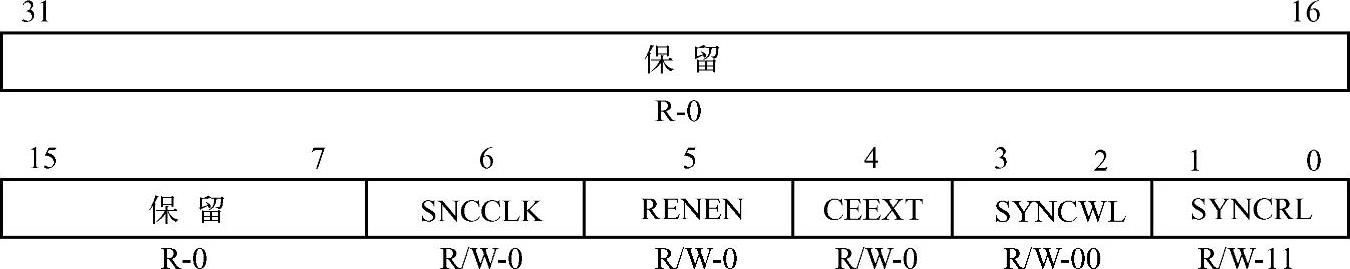

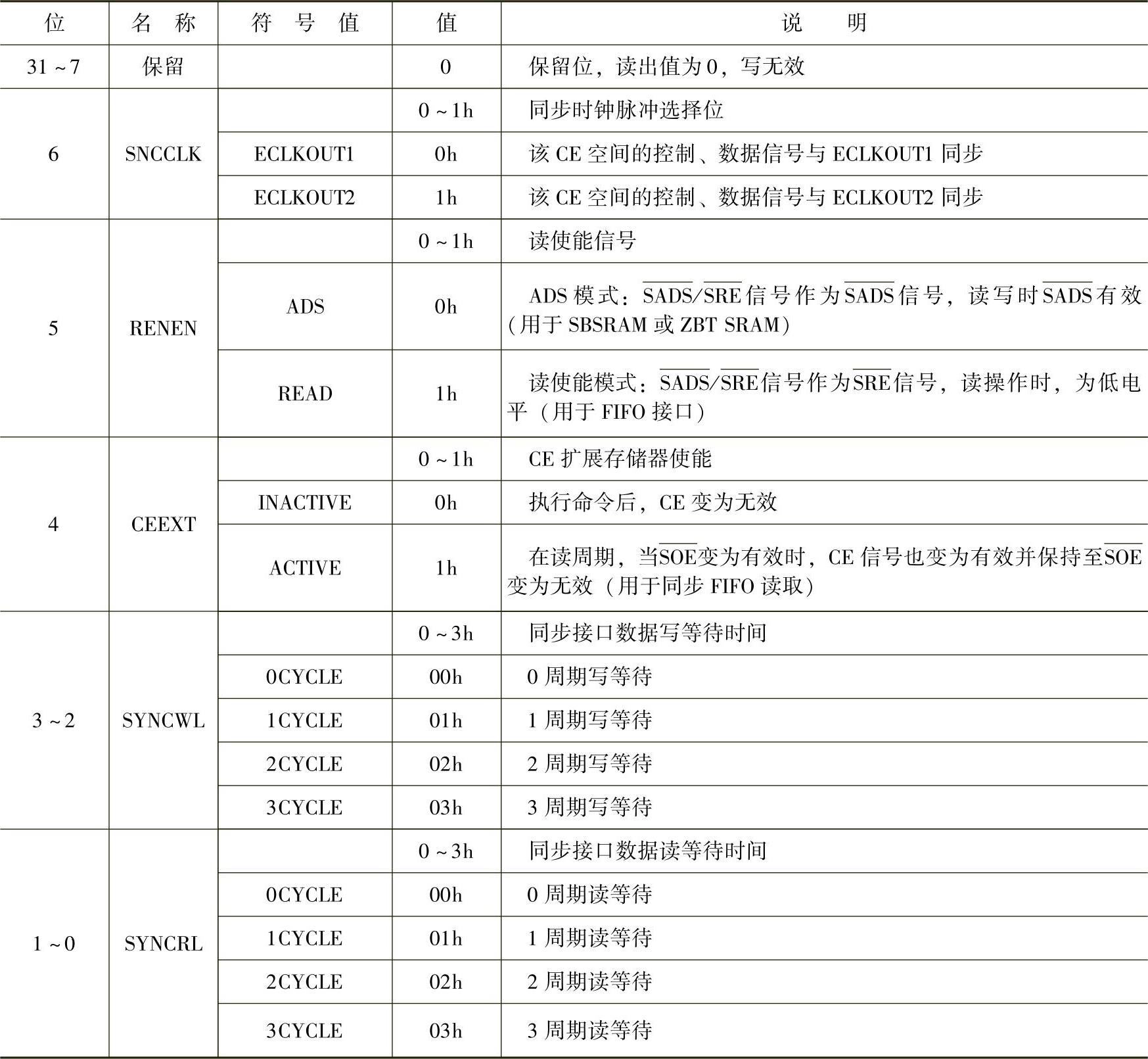

EMIFACE空间二级控制(CExSEC)寄存器是TMS320C64x DSP特有的寄存器,该寄存器是为了实现可编程序的同步接口而增加的,并控制可编程序同步存储器访问的时序和时钟脉冲,用于指定的CE空间的同步。CExSEC寄存器的结构如图3-4所示。

图3-4 EMIFACE空间二级控制(CExSEC)寄存器

CExSEC寄存器各段位的详细描述说明见表3-5。

表3-5 CExSEC寄存器各段位的详细描述说明

4.EMIFASDRAM扩展寄存器

SDRAM扩展(SDEXT)寄存器允许对SDRAM的许多参数进行编程。只有TMS320C621x/C671x/C64x DSP具有该寄存器。SDRAM的可编程序属性具有如下两个优点:

1)允许对各种SDRAM的接口操作,并且对一些配置和速度特性没有限制。

2)允许EMIFA实现来自外部SDRAM无缝数据传输。(https://www.xing528.com)

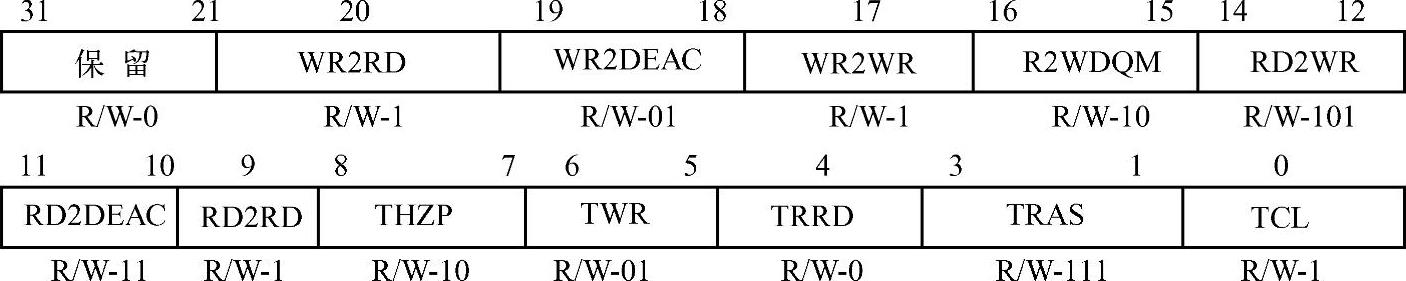

SDEXT寄存器的结构如图3-5所示。

图3-5 EMIFASDRAM扩展(SDEXT)寄存器

SDEXT寄存器各段位的详细描述说明见表3-6。

表3-6 SDEXT寄存器各段位的详细描述说明

在配置SDRAM扩展寄存器之后,必须设置SDRAM控制寄存器。

在配置SDRAM扩展寄存器之后,必须设置SDRAM控制寄存器。

5.EMIFASDRAM控制寄存器

SDRAM控制(SDCTL)寄存器控制用于所有CE空间的SDRAM参数,CE空间通过CECTL寄存器的MTYPE段位指定一个SDRAM存储器类型。因为SDCTL寄存器控制所有SDRAM空间,每个空间必须包含具有相同的刷新、时序和页面属性。当访问SDRAM时,SDCTL寄存器不能被修改。SDCTL寄存器的结构如图3-6所示。

图3-6 EMIFASDRAM控制寄存器(SDCTL)

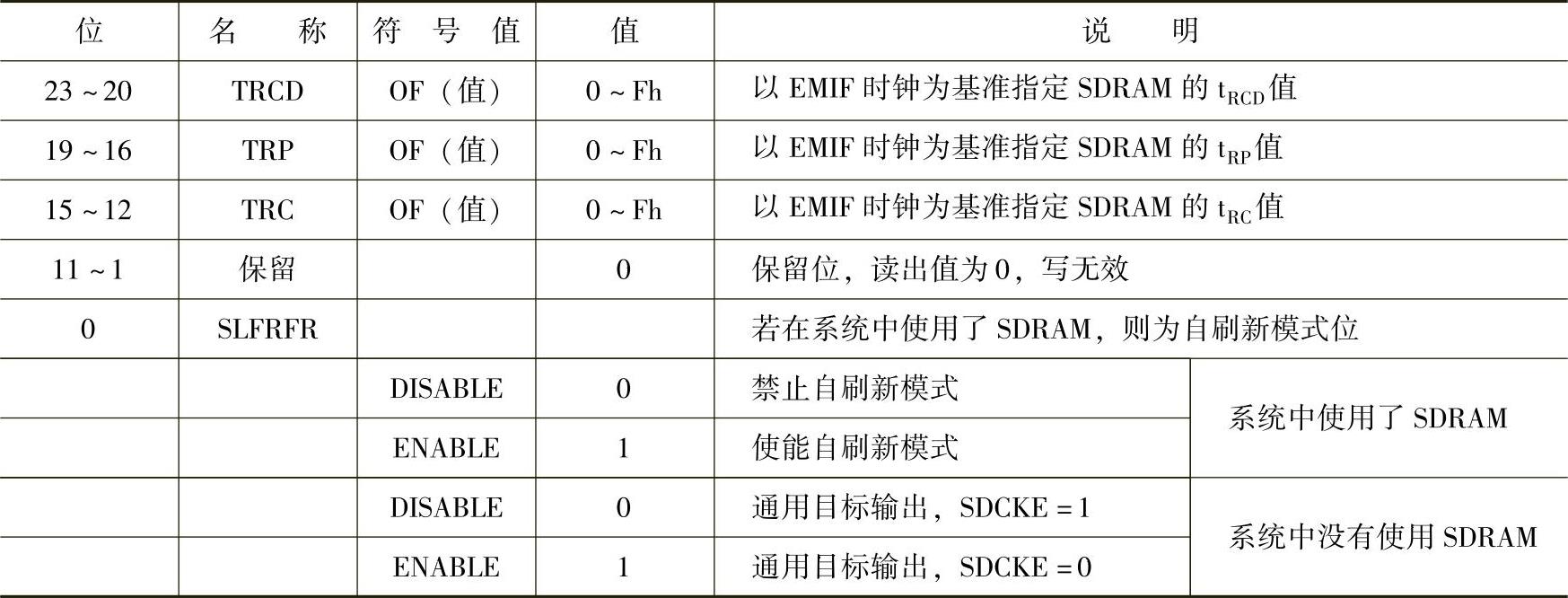

SDCTL寄存器各段位的详细描述说明见表3-7。

表3-7 SDCTL寄存器各段位的详细描述说明

(续)

6.EMIFASDRAM时序寄存器

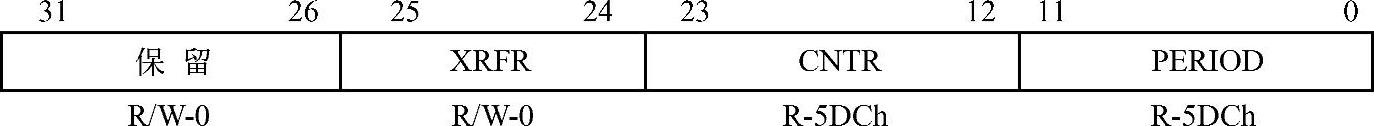

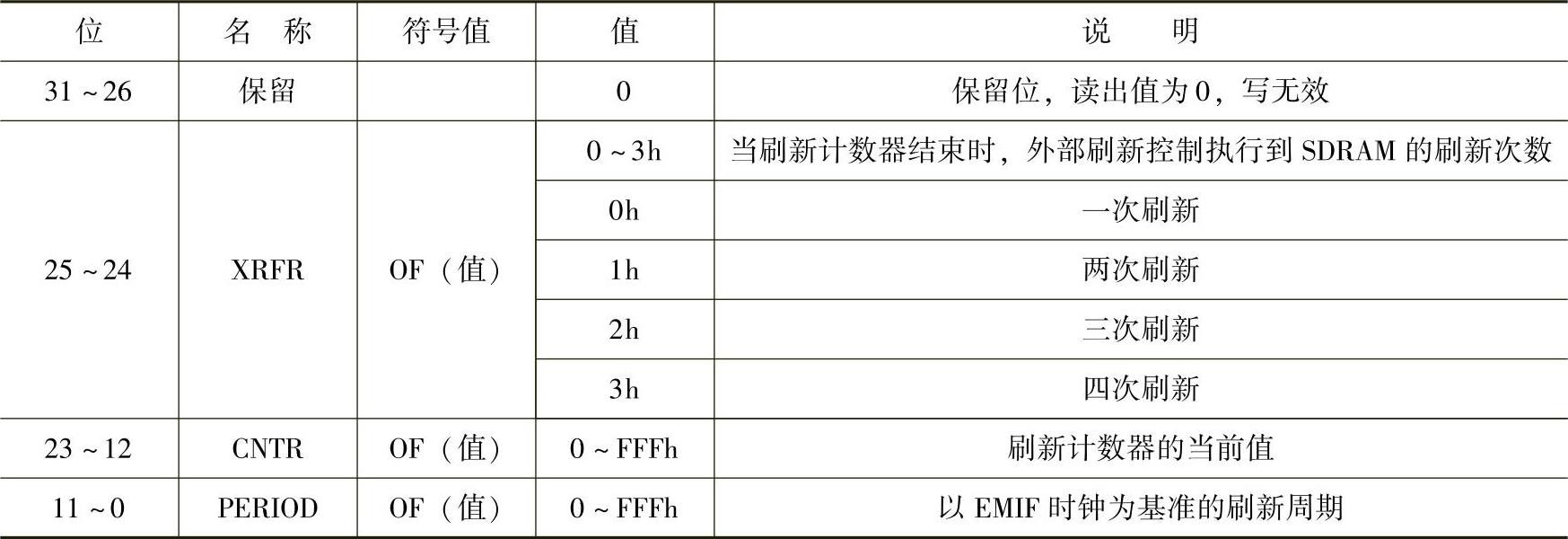

SDRAM时序(SDTIM)寄存器以EMIF时钟周期控制刷新周期。SDTIM寄存器的结构如图3-7所示。

图3-7 EMIFASDRAM时序(SDTIM)寄存器

SDTIM寄存器各段位的详细描述说明见表3-8。

表3-8 SDTIM寄存器各段位的详细描述说明

PERIOD段位可以选择性地送一个中断到CPU。因此,如果系统中没有使用SDRAM,则这个计数器可以用做一个通用目标定时器。CPU可以读取计数器段位(CNTR)。当计数器计数到0时,它将自动重载周期值,并且声明SDMT(到EDMA的同步事件和到CPU的中断源)。

对于TMS320DM642,还具有XRFR段位。XRFR段位控制当刷新计数器到达零时所执行的刷新数。当刷新计数器结束时,可以执行多达4次刷新。例如,由于为了执行一次刷新,必须使所有的存储区无效,希望执行两次刷新。系统通常考虑所有刷新请求为最高优先级。当刷新时,刷新会立刻执行。在执行发布一条刷新命令前,所有的存储器组都无效。当一条刷新命令完成后,存储器组不会恢复到刷新前的状态。

CNTR段位和PERIOD段位的初始值为5DCh(1500个时钟周期)。对于一个10ns的EMIF周期,在刷新操作之间的时间为15μs。SDRAM每次刷新通常需要15.625μs。

7.外设器件传输控制寄存器

外设器件传输控制(PDTCTL)寄存器是TMS320C64xDSP特有的寄存器。该寄存器配置与数据传送阶段相关的 信号的等待时间。

信号的等待时间。

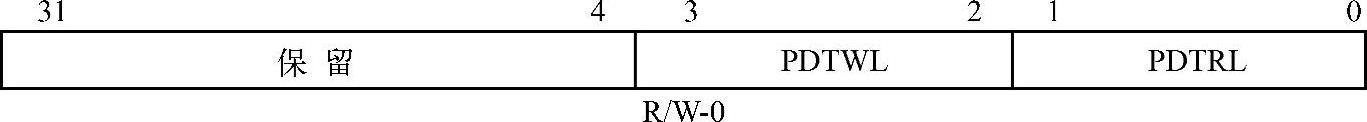

PDTCTL寄存器的结构如图3-8所示。

图3-8 外设器件传输控制(PDTCTL)寄存器

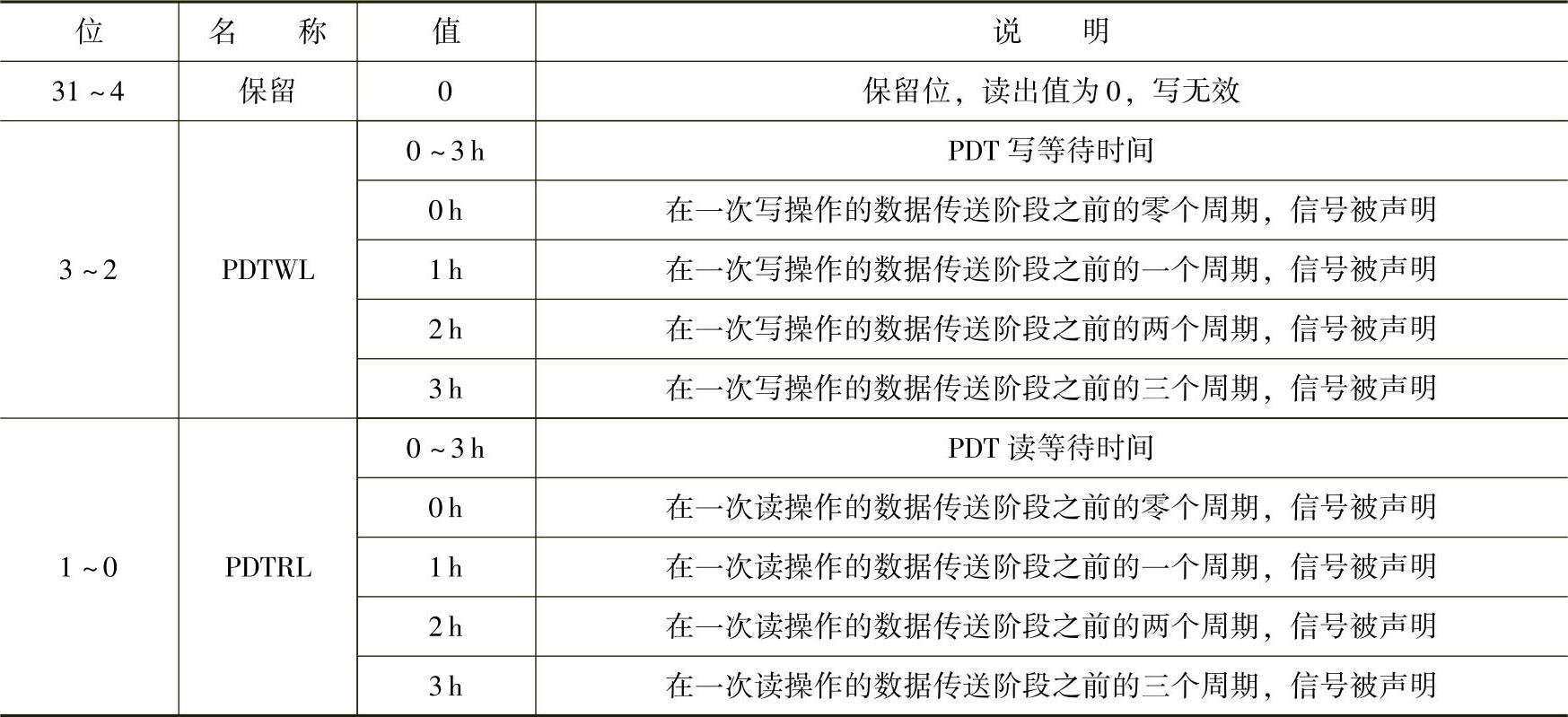

PDTCTL寄存器各段位的详细描述说明见表3-9。

表3-9 PDTCTL寄存器各段位的详细描述说明

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。