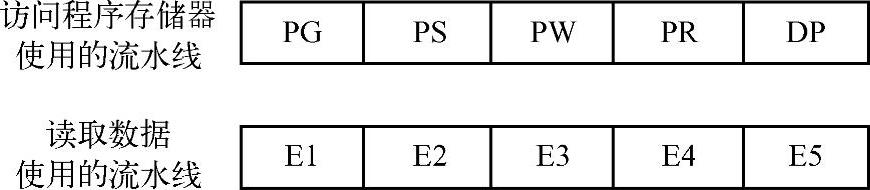

TMS320C6x系列DSP具有典型的存储器配置,即一个物理空间作为程序存储空间,另一个物理空间作为数据存储空间。数据读取和程序读取在流水线中的操作相同,仅区别于使用不同的节拍以完成操作。程序存储器访问和数据读取所使用的流水线节拍如图2-18所示。

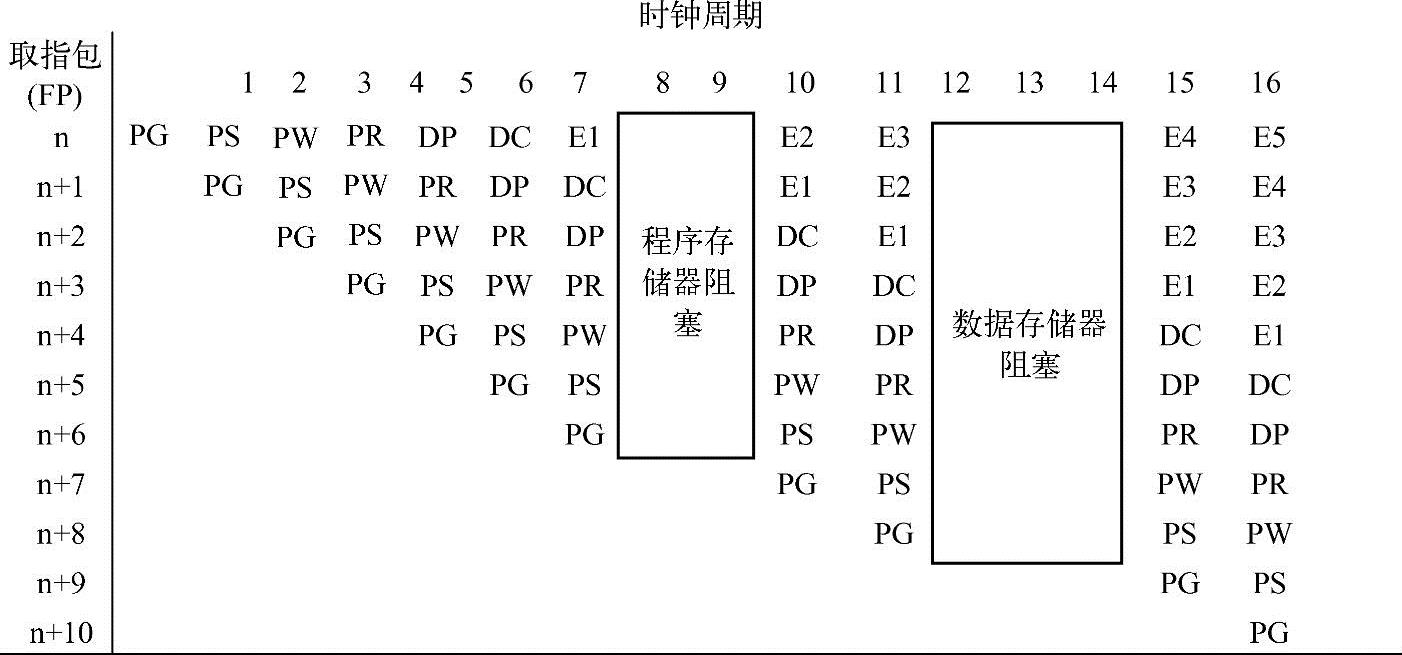

程序存储器访问和数据读取在内部存储器中以相同的速度运行,且执行同种类型的操作。表2-10列出指令读取和数据读取的流水线操作。

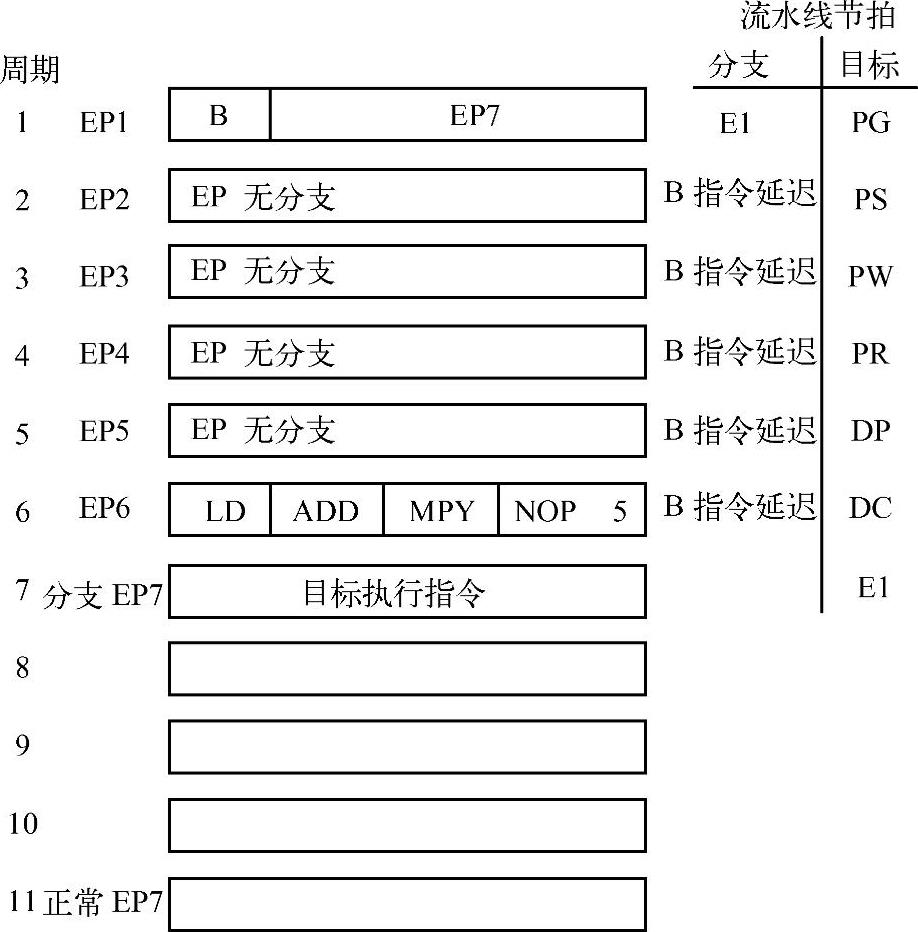

图2-17 跳转指令提前结束多周期NOP指令

图2-18 程序存储器访问和数据读取所使用的流水线节拍

表2-10 指令读取和数据读取的流水线操作

存储器对流水线性能的影响可分为两种情况:存储器阻塞(Memory Stall)和存储器冲突(Memory BankHit)。下边分别举例说明。

1.存储器阻塞

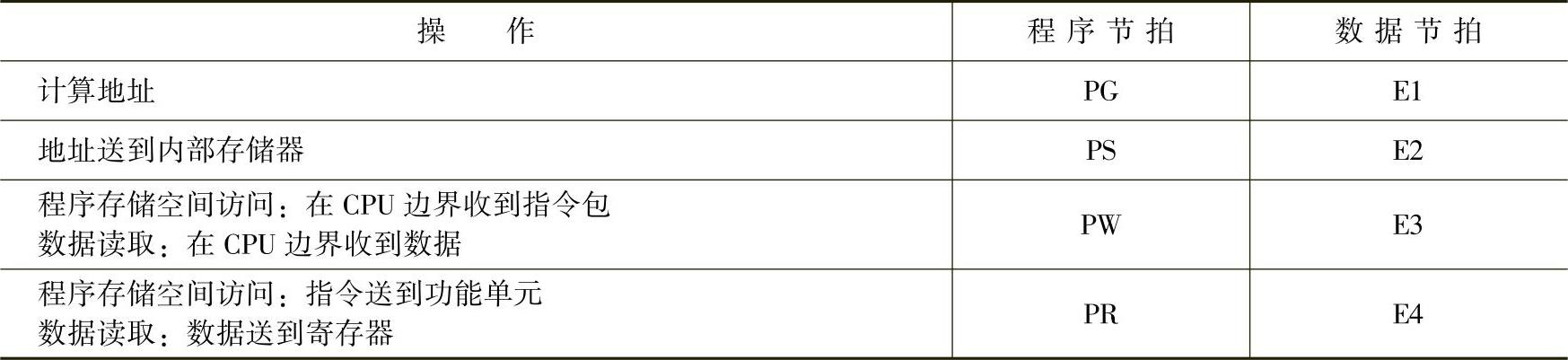

CPU访问存储器(包括程序存储器和数据存储器),如果存储器不能及时响应CPU的访问,就会产生CPU等待。等待期间,TMS320C6x的流水线暂停,称为流水线的存储器阻塞,导致程序延迟或停止一段时间。对于程序存储器,存储器阻塞发生在流水线取指阶段的PW节拍,对于数据存储器,存储器阻塞发生在流水线取指阶段的E3节拍。

存储器阻塞引起处于该流水线的所有节拍延长一个时钟周期以上,从而使执行增加额外的时钟周期,但不会改变程序运行结果。

发生存储器阻塞的流水线过程如图2-19所示。

(https://www.xing528.com)

(https://www.xing528.com)

图2-19 存储器阻塞的流水线过程

2.存储器冲突

存储器冲突是并行执行的多条指令对同一存储器同时进行访问引起的。

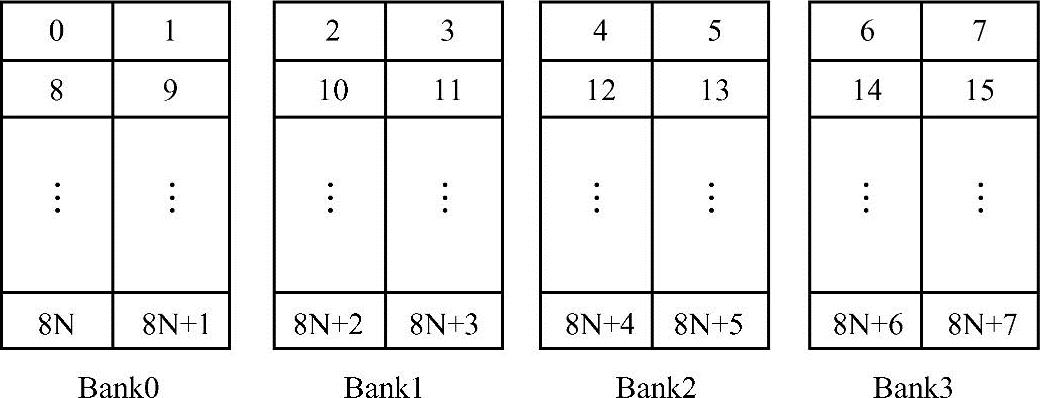

为了减少存储器冲突,大多数TMS320C6x DSP的存储器使用交叉存储方案(TMS320C6x1x除外)。TMS320C62x/C64x的存储器配置方案如图2-20所示,其中的数字代表存储器单元的地址,每个单元存储一个字节。对地址0的字节读取指令为LDB,读取Bank0区的字节0内的数据;对地址0的半字读取指令为LDH,读取Bank0区的字节0和字节1内的数据;对地址0的字读取指令为LDW,读取Bank 0和Bank 1区的字节0~3内的数据;对地址0的双字读取指令为LDDW,读取Bank0~Bank3区的字节0~7内的数据。

图2-20 TMS320C62x/C64x的存储器配置方案

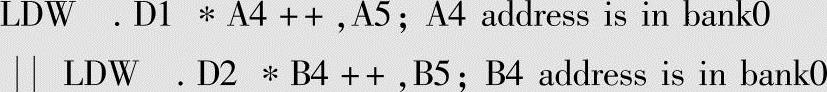

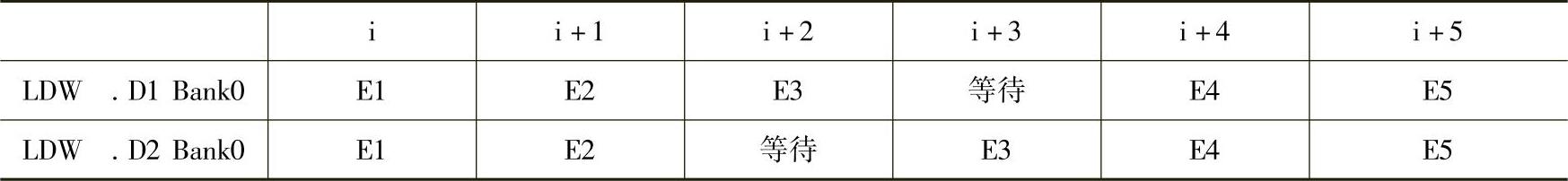

在一个周期内,同一个存储器Bank只允许访问一次,如果在同一周期内,对同一Bank多次访问,就会产生存储器冲突,存储器冲突会导致流水线的存储器阻塞。举例如下。

上述两条并行执行的指令代码,试图同时访问Bank0,其结果:第1个LDW指令访问Bank0(E3节拍)被安排在第i+2周期执行,同时,E4节拍延迟一个时钟周期,第2个LDW指令访问Bank0(E3节拍)被安排在第i+3周期执行,即E3节拍延迟1个时钟周期,两条指令在E4节拍重新对齐。

为了消除这类额外增加的节拍,可以考虑使用多个存储器空间配置方案。图2-11显示了配置两个存储器空间的配置方案。

表2-11 两个存储器空间的配置方案

对一个存储器空间Bank0的访问,不会影响另一个存储器空间Bank0的访问,从而进一步减少了存储器冲突的发生,消除了额外增加的节拍。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。