数据通路是TMS320C6xCPU的指令执行部分,是DSP内核的重要组成部分。TMS320C6000CPU的数据通路主要由2组通用寄存器和8个功能单元组成,包括:

·2组通用寄存器(A和B)。

·8个功能单元(.L1,.L2,.S1,.S2,.M1,.M2,.D1和.D2)。

·2个存储器读取通路(LD1和LD2)。

·2个存储器存储通路(ST1和ST2)。

·2个数据寻址通路(DA1和DA2)。

·2个寄存器交叉通路(1X和2X)。

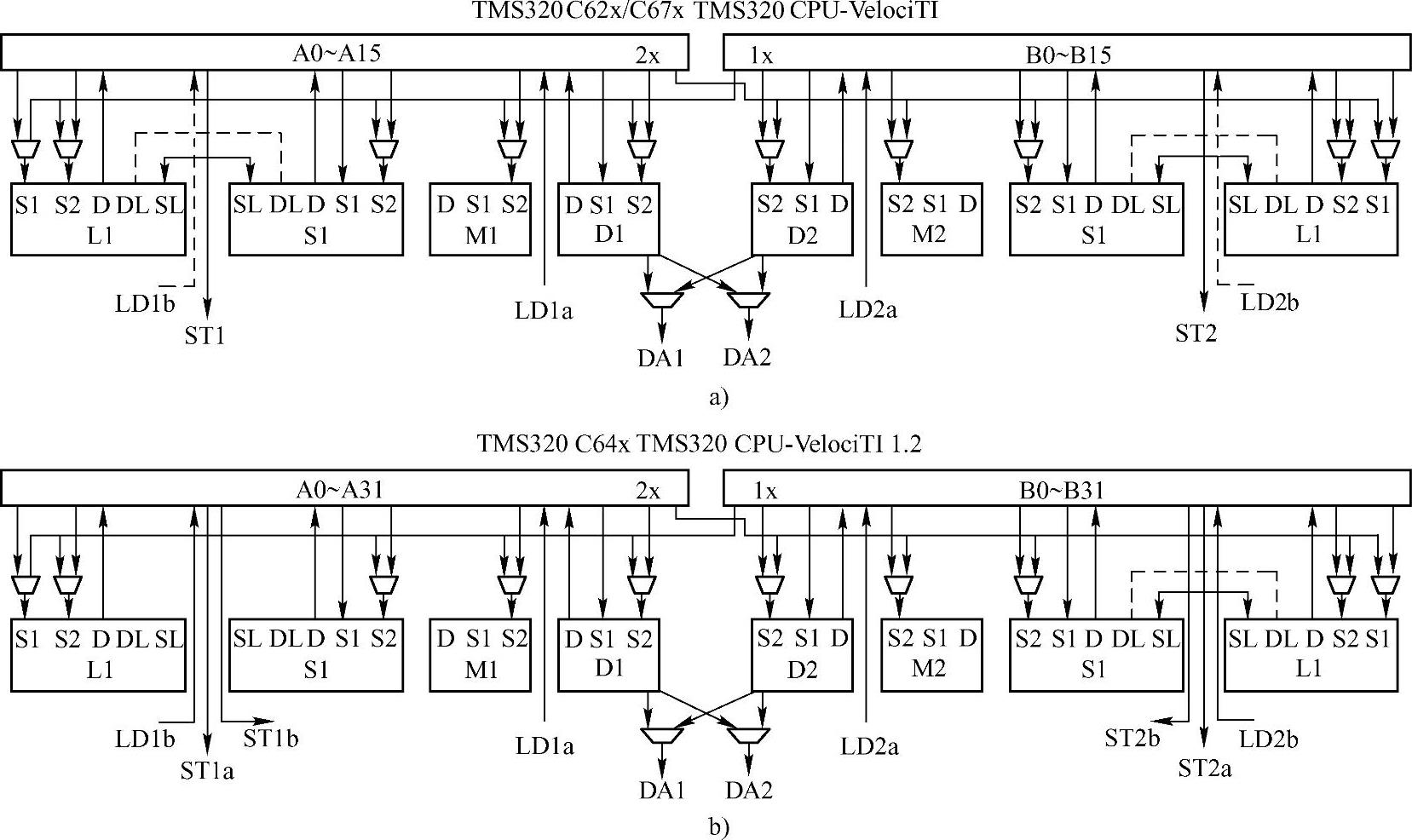

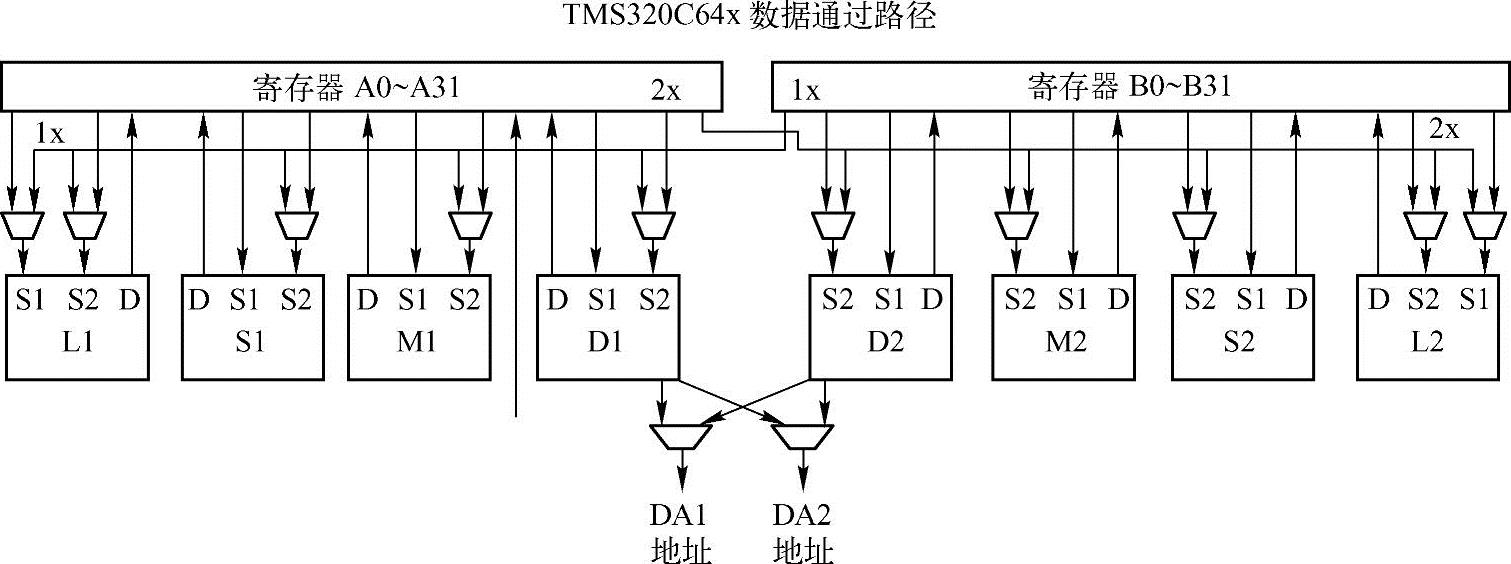

TMS320C62x/C67x的数据通路和TMS320C64x的数据通路分别如图2-3a、图2-3b所示。

1.通用寄存器组

通用寄存器可以用来存放数据、数据地址指针或作为条件寄存器使用。TMS320C6x的数据通路包含2个通用寄存器组(A和B)。对于TMS320C62x/C67x的DSP,每个寄存器组分别包括16个32位寄存器,分别为A0~A15和B0~B15。对于TMS320C64xDSP,每个寄存器组分别包括32个32位寄存器,分别为A0~A31和B0~B31。

TMS320C6x的通用寄存器可以存放32位整型、32位单精度浮点型、40位长整型、64位双精度浮点型和64位整型数据。此外,TMS320C6x的每个通用寄存器还可以存放2个16位整型(16位紧凑格式)或4个8位整型(8位紧凑格式)数据。

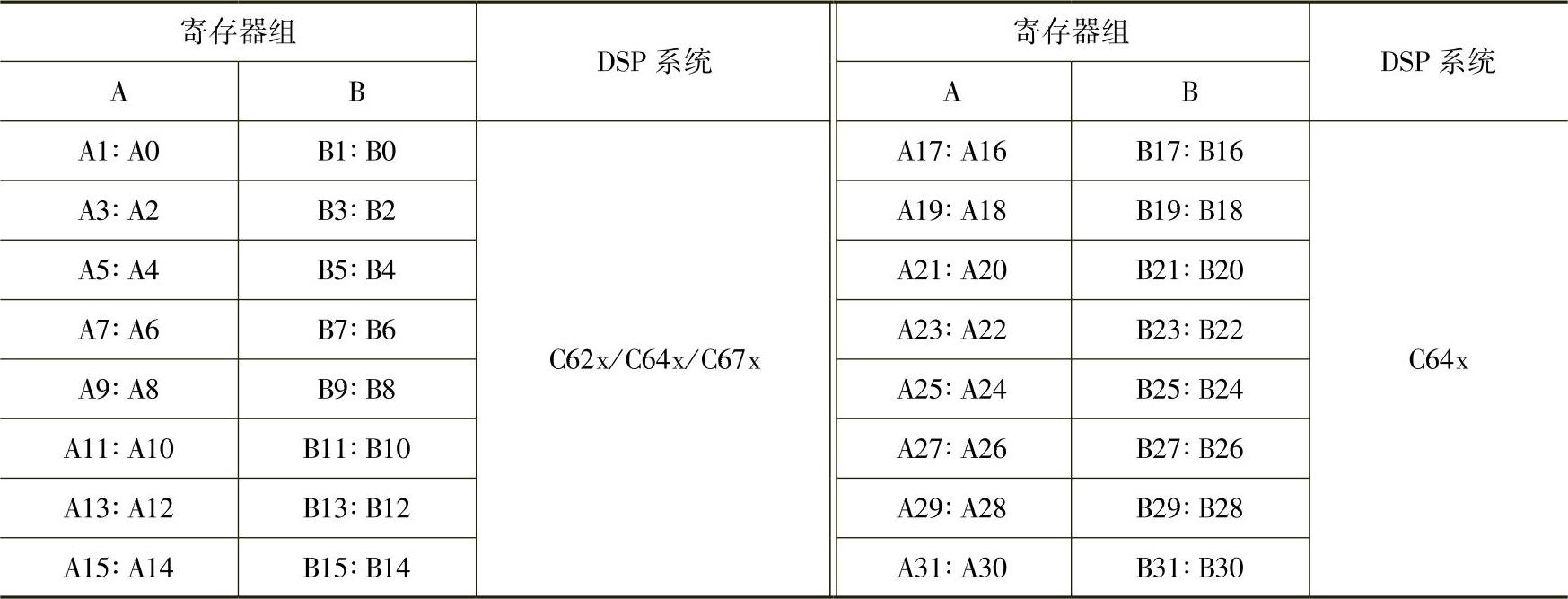

TMS320C6x采用寄存器对存放40位长整型、64位双精度浮点型和64位整型数据。寄存器对的编组方法见表2-1,其中,偶数编号的寄存器存放数据的低位有效部分,奇数编号的寄存器存放数据的高位有效部分。

图2-3 TMS320C6xCPU的数据通路

a)TMS320C62x/C67xCPU数据通路 b)TMS320C64xCPU数据通路

表2-1 TMS320C6x寄存器对的编组方法

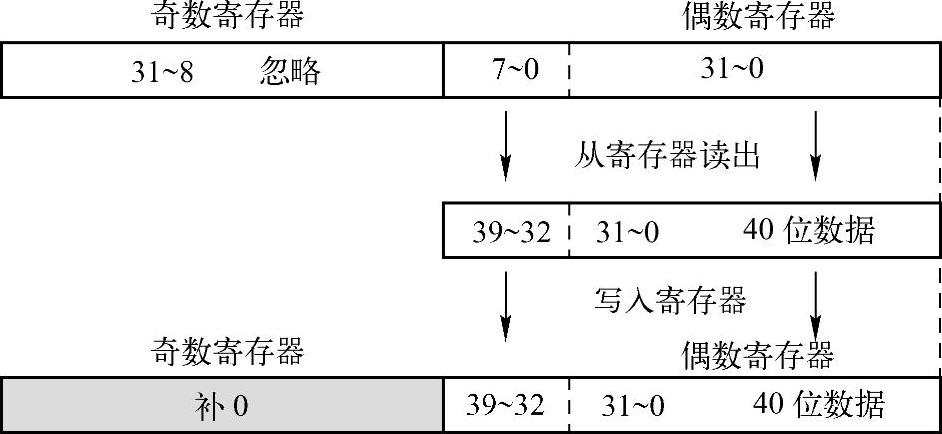

图2-4为40位长整型数在寄存器中的存放方法。

图2-4 40位长整型数在寄存器中的存放方法

序号为奇数的寄存器的高24位无效,对寄存器的长数据的存储操作将导致这24位为0,而序号为偶数的寄存器中的数据不变。

序号为奇数的寄存器的高24位无效,对寄存器的长数据的存储操作将导致这24位为0,而序号为偶数的寄存器中的数据不变。

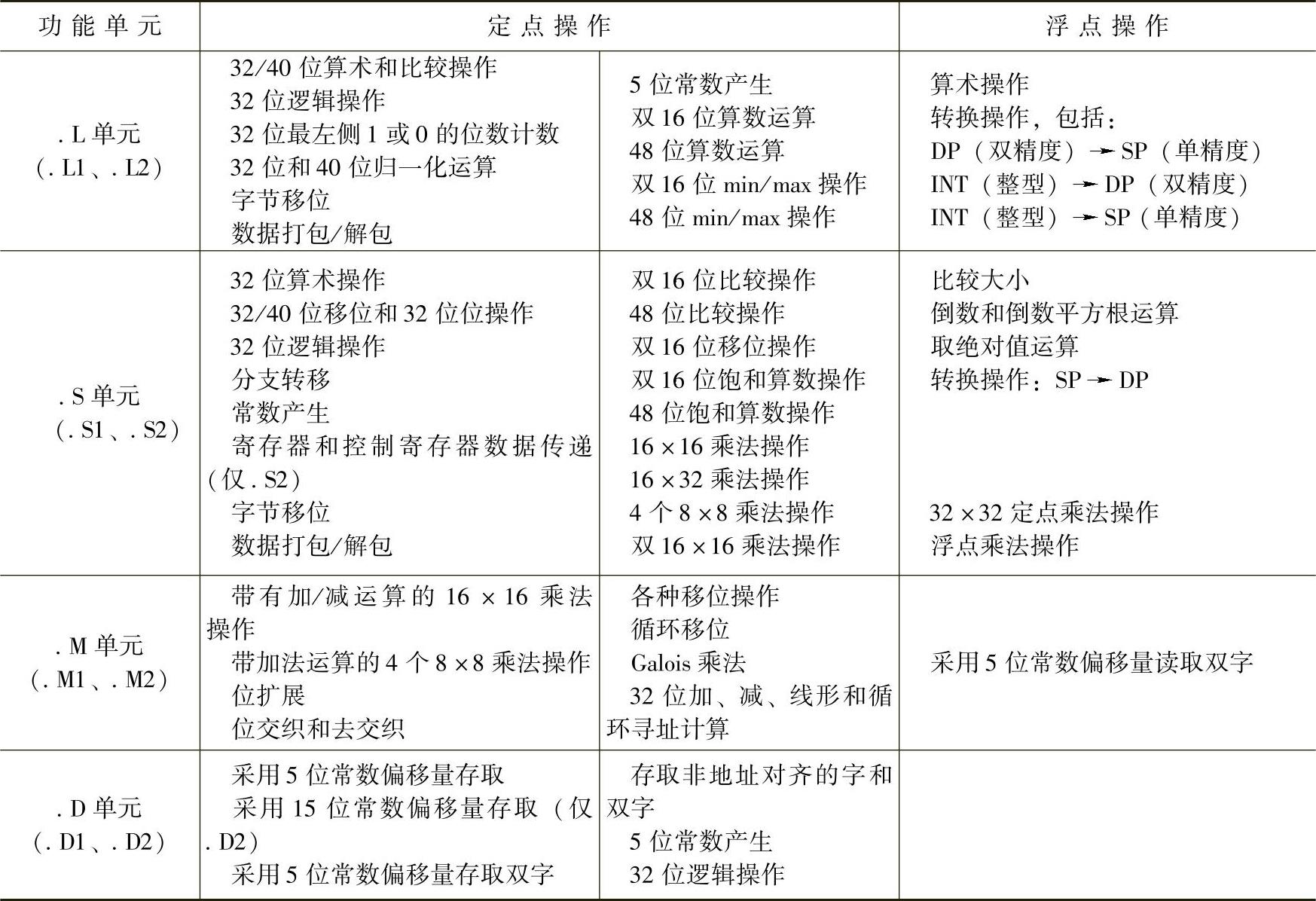

2.功能单元

TMS320C6x有两个数据通路,分别是A数据通路和B数据通路。每个数据通路中有4个功能单元,分别是.L、.S、.M和.D。每个数据通路中的功能单元和另一个数据通路中对应的功能单元功能基本相同。

TMS320C6x的指令是由各个功能单元完成的,但每个功能单元只能完成部分指令,其中,.L和.S单元主要完成算术和逻辑运算,.S单元完成程序跳转指令,.M单元主要完成乘法运算,.D单元主要完成数据存储器读取/写入。表2-2描述了各功能单元的主要功能。

表2-2 功能单元的介绍(https://www.xing528.com)

功能单元到寄存器组的数据读/写是通过数据端口完成的。每个功能单元到所属数据通路中的寄存器组,都有1个32位写数据端口和2个32位读数据端口。此外,.L1、.L2、.S1和.S2功能单元还另配有1个8位读/写端口,用于和32位端口共同完成40位数据的读/写操作;TMS320C64x的.M功能单元,可以返回64位的乘法结果,所以,TMS320C64x的.M功能单元还另配有1个32位写端口。

每个功能单元可以直接对各自所属数据通路中的寄存器组进行读/写操作,即.L1、.S1、.M1和.D1可以直接读/写寄存器组A;.L2、.S2、.M2和.D2可以直接读/写寄存器组B。由于每个单元都有各自独立的32位写端口,因此8个单元每个周期都可以用于并行操作。

3.交叉通路

每个功能单元使用自己的数据通道可以对寄存器进行直接读写。功能单元不可以对另一侧寄存器组进行写操作,但可以通过交叉通路,对另一侧的寄存器组进行读操作。如果这些单元要读写另一个寄存器,则需要通过交叉通道1X和2X将它们连接起来。

A寄存器组通过交叉通路2X和B寄存器组中的功能单元相连,B寄存器组通过交叉通路1X和A寄存器组中的功能单元相连。通过交叉通路,A(或B)寄存器组中的功能单元可以读取B(或A)寄存器组中的32位操作数。交叉通路1X允许寄存器组A中的功能单元从B寄存器组中读取源操作数,交叉通路2X允许B寄存器组中的功能单元从A寄存器组中读取源操作数。

对于TMS320C62x/C67xDSP,8个功能单元中的6个可以通过交叉通路读取另一侧的寄存器组,其中,.M1、.M2、.S1和.S2的SRC2输入可以在交叉通路和同一侧寄存器组之间选择,.L1和.L2单元的SRC1和SRC2输入都可以在交叉通路和同一侧寄存器组之间选择。

对于TMS320C64xDSP,8个功能单元都可以通过交叉通路读取另一侧的寄存器组,其中,.M1、.M2,.S1、.S2,.D1和.D2单元的SRC2输入可以在交叉通路和同一侧寄存器组之间选择,.L1和.L2单元的SRC1和SRC2输入都可以在交叉通路和同一侧寄存器组之间选择。

TMS320C6x只有两个交叉通路,这就使得在一个指令周期内只能从寄存器组读取一次源操作数,或者在一个指令周期内只能读取两个交叉通路的源操作数。对于TMS320C62x/C67xDSP,在一次操作中,每个数据通路只有一个功能单元可以从另一侧寄存器组中获取操作数;对于TMS320C64xDSP,一侧数据通路中的多个功能单元可以同时读取交叉通路的源操作数。如图2-5所示,在一次操作中,TMS320C64xDSP交叉通路操作数可以同时被两个功能单元使用。

对于TMS320C64xDSP,只要一条指令试图通过前一个周期被更新的交叉通路读取一个寄存器,就会产生一个时钟周期的延迟,这种延迟叫做交叉通路延迟。

交叉通路延迟是硬件自动插入的,不需要NOP指令。需要注意的是,如果被读取的寄存器是LDx指令放置数据的目的地址,则不会产生任何延迟。

交叉通路延迟是硬件自动插入的,不需要NOP指令。需要注意的是,如果被读取的寄存器是LDx指令放置数据的目的地址,则不会产生任何延迟。

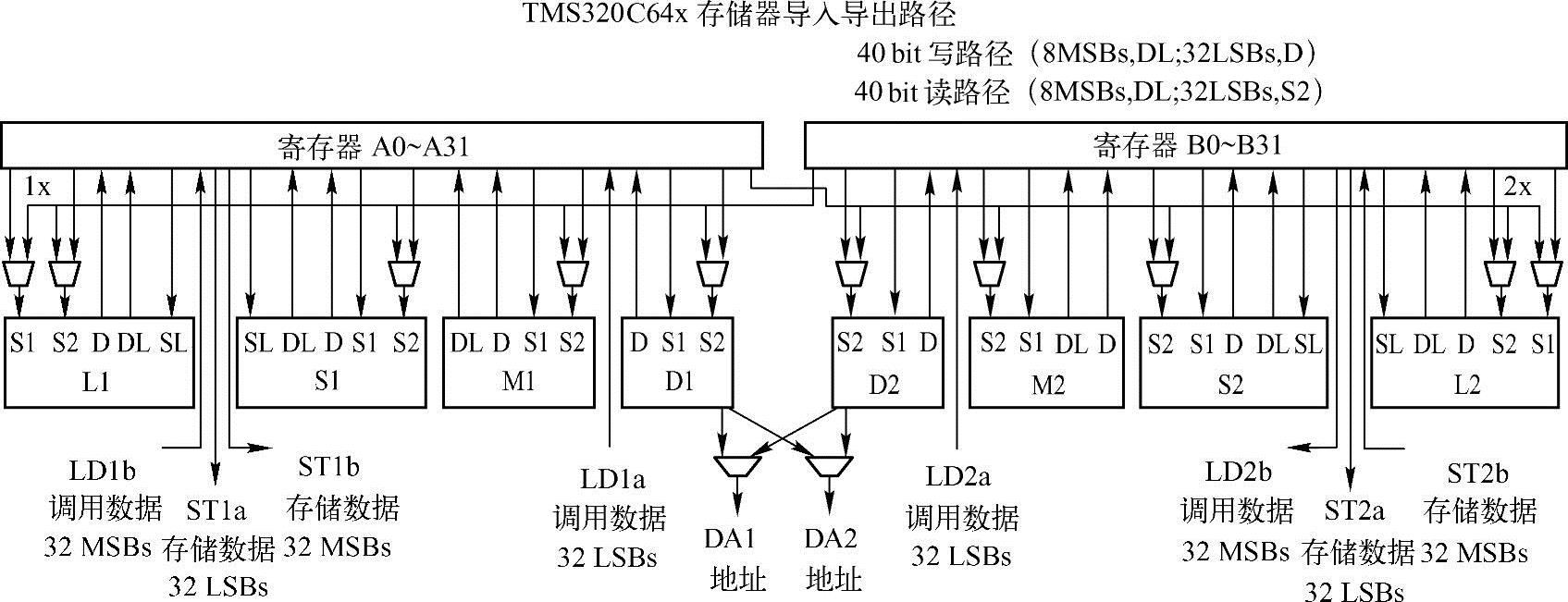

4.存储器存取通路

TMS320C64x支持双字存取。从存储器到寄存器文件导入数据时,有4个32位的通路可以使用。在A侧,LD1a是低32位装载通路,LD1b是高32位装载通路;在B侧,LD2a是低32位装载通路,LD2b是高32位装载通路。有4个32位通路,用来把寄存器的值写入存储器中。在A侧,ST1a是低32位写通路、ST1b是高32位写通路,在B侧,ST2a是低32位写通路、ST2b是高32位写通路。

5.数据地址通路

数据地址通路DA1、DA2和两个数据通路的.D单元交叉连接,任何一个数据通路产生的地址可以到任意一个寄存器组中存取数据。

TMS320C64xDSP的数据存取通路如图2-6所示。

图2-5 TMS320C64x数据交叉通路

图2-6 TMS320C64x数据存取通路

DA1和DA2以及它们各自相关的数据通路被分别指定为T1和T2。T1由DA1、LD1和ST1组成。对于TMS320C62x/C67x,LD1包括LD1a和LD1b,支持64位数据读取;对于TMS320C64x,ST1包括ST1a和ST1b,支持64位数据存储。同样,T2由DA2、LD2和ST2组成。对于TMS320C62x/C67x,LD2包括LD2a和LD2b,支持64位数据读取;对于TMS320C64x,ST2包括ST2a和ST2b,支持64位数据存储。

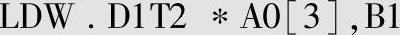

下面的数据读取指令,使用.D1单元产生的地址,通过LD2数据通路,读取数据到B寄存器组中的寄存器B1中。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。