1.同步二进制加法计数器

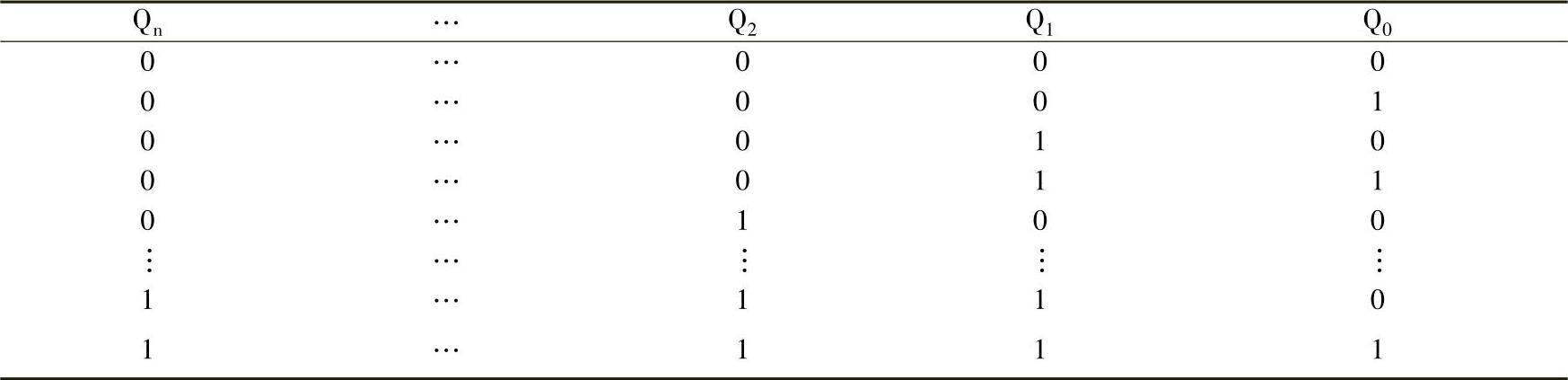

同步二进制加法计数器的状态见表11-12。从表11-12中可以知道,Q0只要有时钟脉冲就翻转,而Q1要在Q0为1时翻转,Q2要在Q1和Q0都是1时翻转,由此类推,若要Qn翻转,必须Qn-1…Q2、Q1和Q0都为1。若用JK触发器组成同步二进制加法计数器,则每一个触发器的翻转的条件:

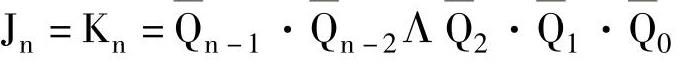

Jn=Kn=Qn-1·Qn-2ΛQ2·Q1·Q0

表11-12 同步二进制加法计数器状态表

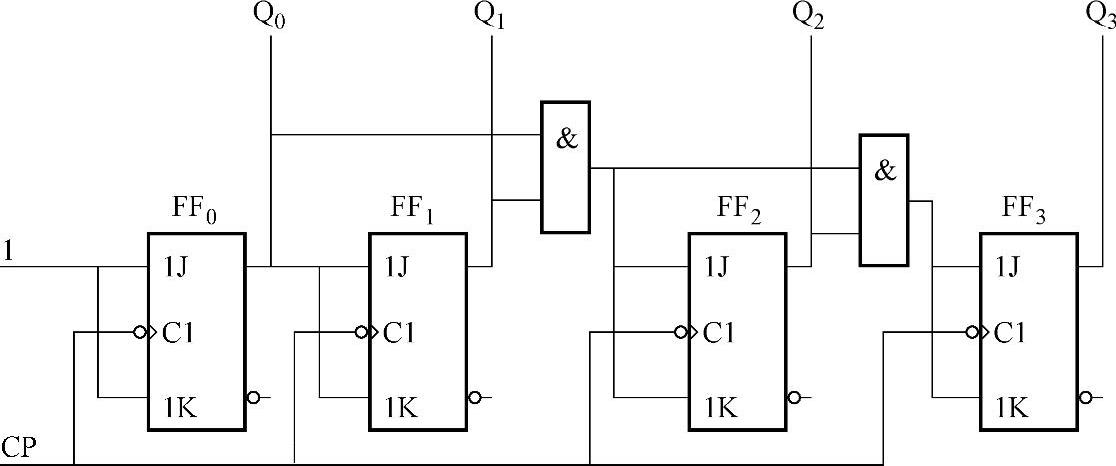

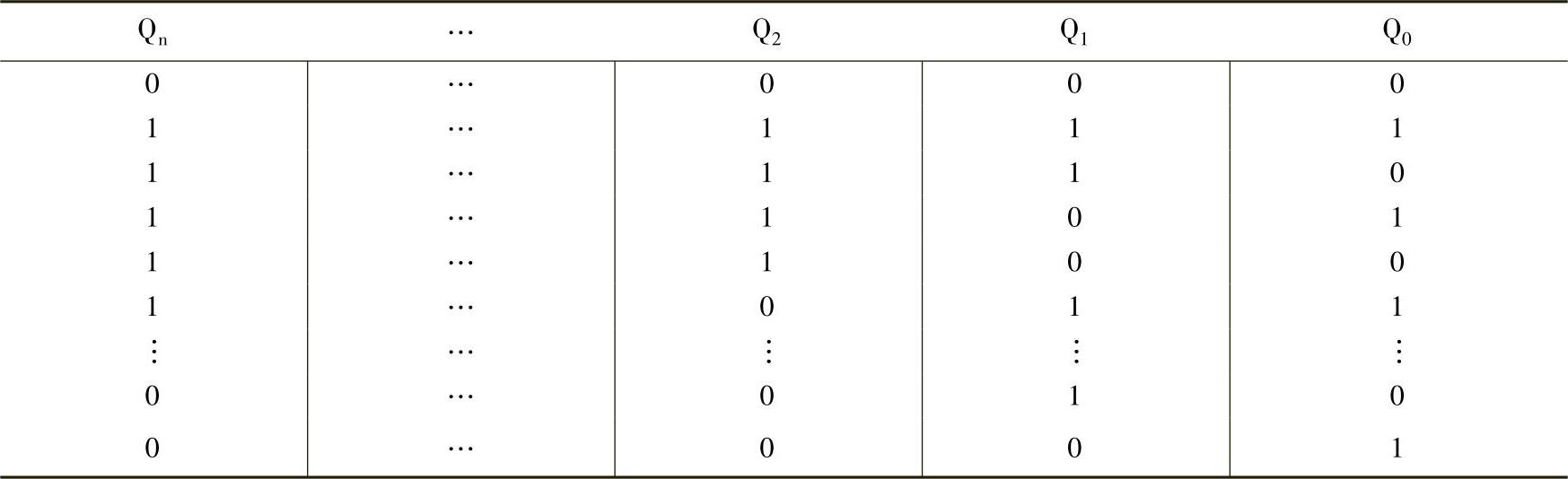

根据这个规律,可以画出如图11-25所示的同步二进制加法计数器的逻辑图。

图11-25 同步二进制加法计数器的逻辑图

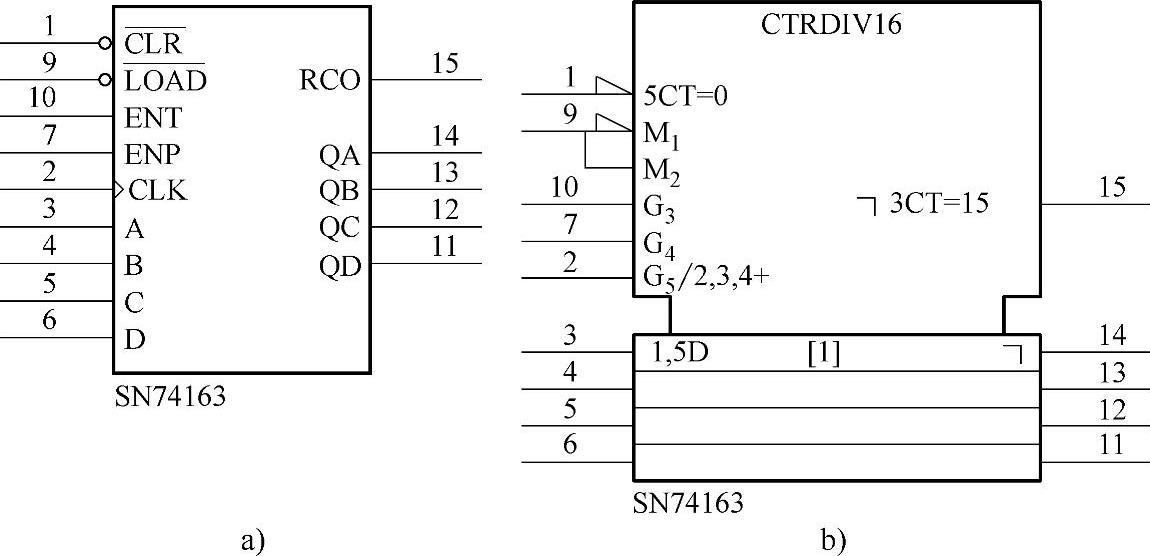

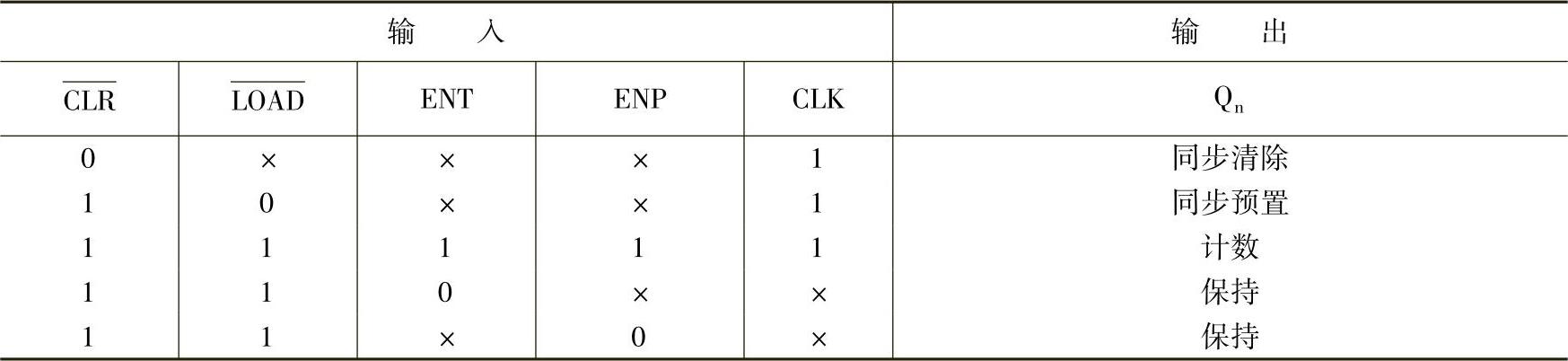

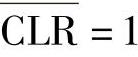

74163是四位二进制加法计数器。图11-26是74163的流行符号和IEEE符号。功能见表11-13。它具有同步预置 、清除

、清除 、使能控制ENT、ENP和纹波进位端RCO,计数器在时钟上升沿时进行预置、清除和计数器操作。

、使能控制ENT、ENP和纹波进位端RCO,计数器在时钟上升沿时进行预置、清除和计数器操作。

图11-26 74163的流行符号和IEEE符号

表11-13 74163功能表

2.同步二进制减法计数器

二进制减法计数器状态见表11-14。从表中可以知道,Q0只要有时钟脉冲就翻转,而Q1要在Q0为0时翻转,Q2要在Q1和Q0都是0时翻转,由此类推,若要Qn翻转必须Qn-1…Q2、Q1和Q0都为0。若使用JK触发器组成同步减法计数器,则任何一个触发器的翻转条件:

表11-14 二进制减法计数器状态表

根据这个规律,可以画出如图11-27所示同步二进制减法计数器的逻辑图。

图11-27 同步二进制减法计数器的逻辑图

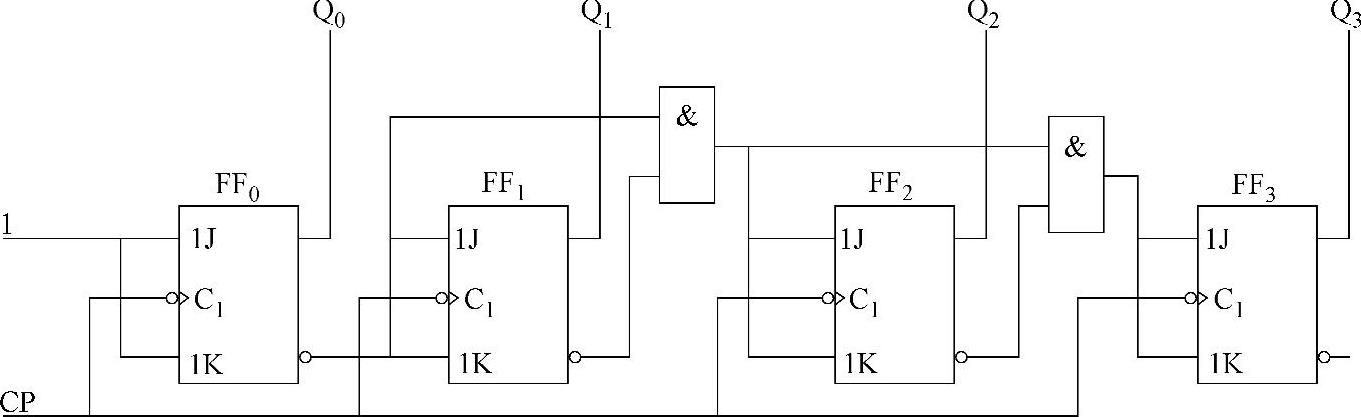

74191是可预置数4位二进制同步可逆(加减)计数器,流行符号和IEEE符号如图11-28所示。它具有置数端 、加减控制端

、加减控制端 和计数控制端

和计数控制端 ,为方便级连,设置了两个输出端

,为方便级连,设置了两个输出端 和MAX/MIN。当加减控制端

和MAX/MIN。当加减控制端 =减计数,

=减计数, 时加计数;当置数端

时加计数;当置数端 时预置数;当计数控制端

时预置数;当计数控制端 时禁止计数;

时禁止计数; 时,计数器将在时钟上升沿开始计数;当计数器产生正溢出或下溢出时,MAX/MIN端输出与时钟周期相同的正脉冲,而

时,计数器将在时钟上升沿开始计数;当计数器产生正溢出或下溢出时,MAX/MIN端输出与时钟周期相同的正脉冲,而 产生一个宽度为时钟低电平宽度的低电平。详细功能见表11-15。

产生一个宽度为时钟低电平宽度的低电平。详细功能见表11-15。

图11-28 74191流行符号和IEEE符号

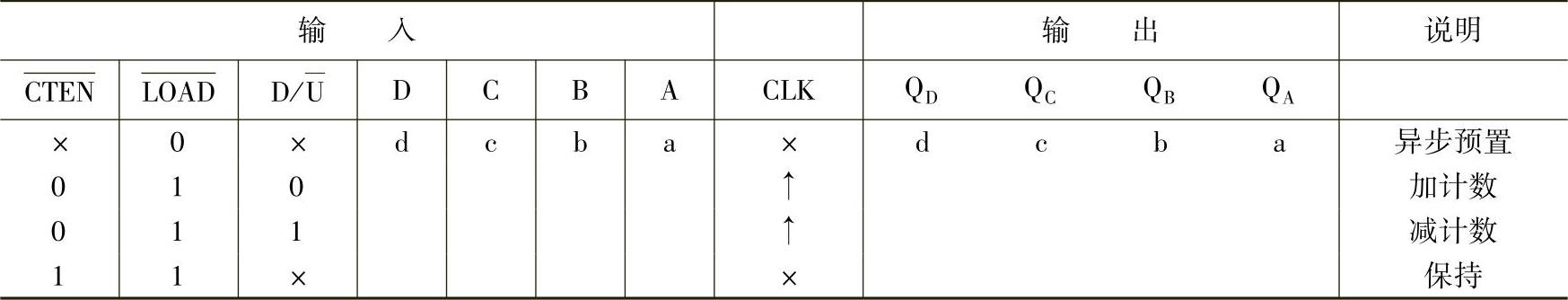

表11-15 74191功能表(https://www.xing528.com)

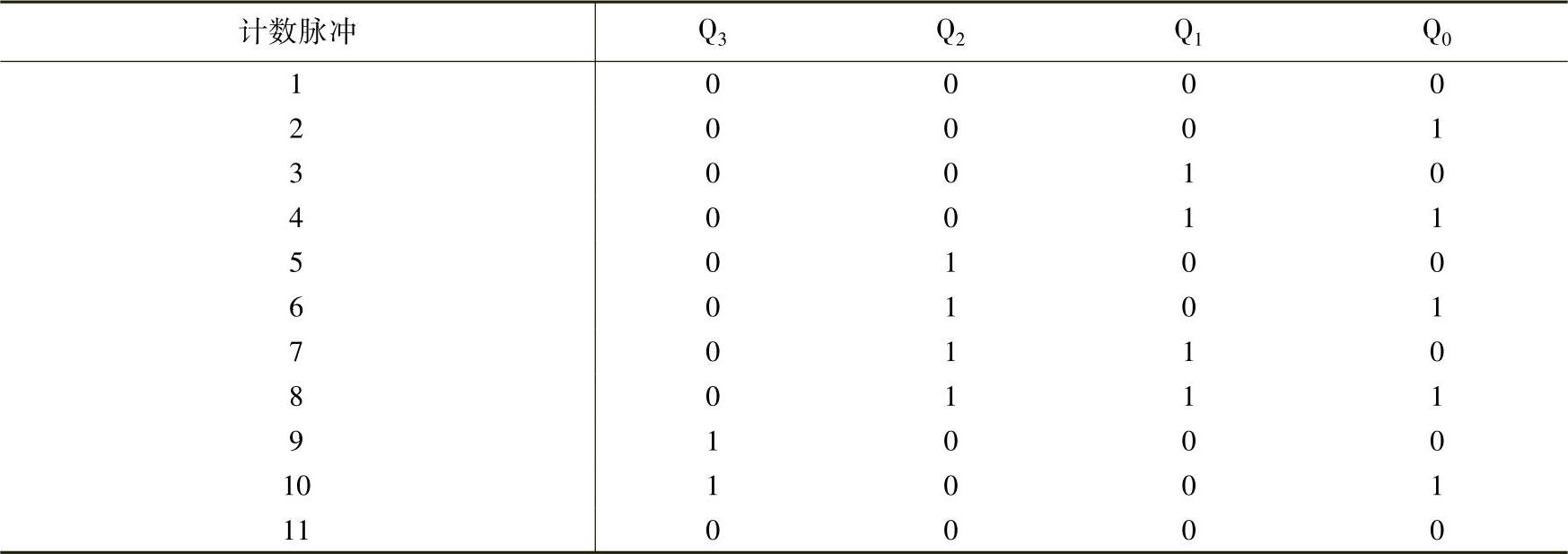

表11-16 十进制计数器状态表

3.同步十进制加法计数器

下面以JK触发器为例,讨论同步十进制加法计数器。从状态表11-16可以看出,在第10个脉冲到来之前的情况,与同步二进制计数器相同,只要在第10个脉冲后,解决如下问题:

第一问题:使Q1和Q2保持不变。

从状态表可以看出,Q3为1时,Q1和Q2保持为零,所以可以取Q3信号保持Q1为0,只要Q1为0,Q2就保持不变。

第二问题:使Q0和Q3翻转置0。

Q0自由翻转,当第10个脉冲到来前,Q0=1,所以当第10个脉冲到来后,Q0=0。

从状态表可以看出,只有当Q3自己为1时,同时Q0也为1时,Q3才置0。

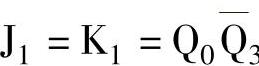

从以上分析我们有如下驱动方程:

J0=K0=1

J2=K2=Q1Q0

J3=K3=Q2Q1Q0+Q3Q0

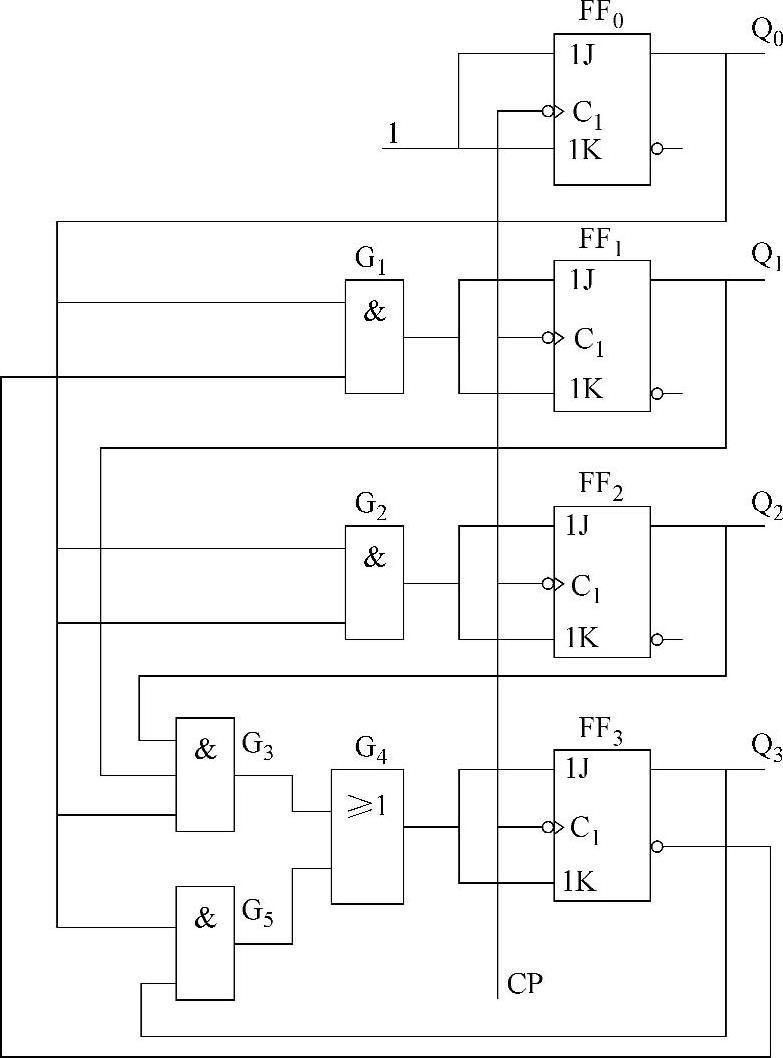

由此可以画出如图11-29所示逻辑电路。

图11-29 同步十进制加法计数器逻辑电路

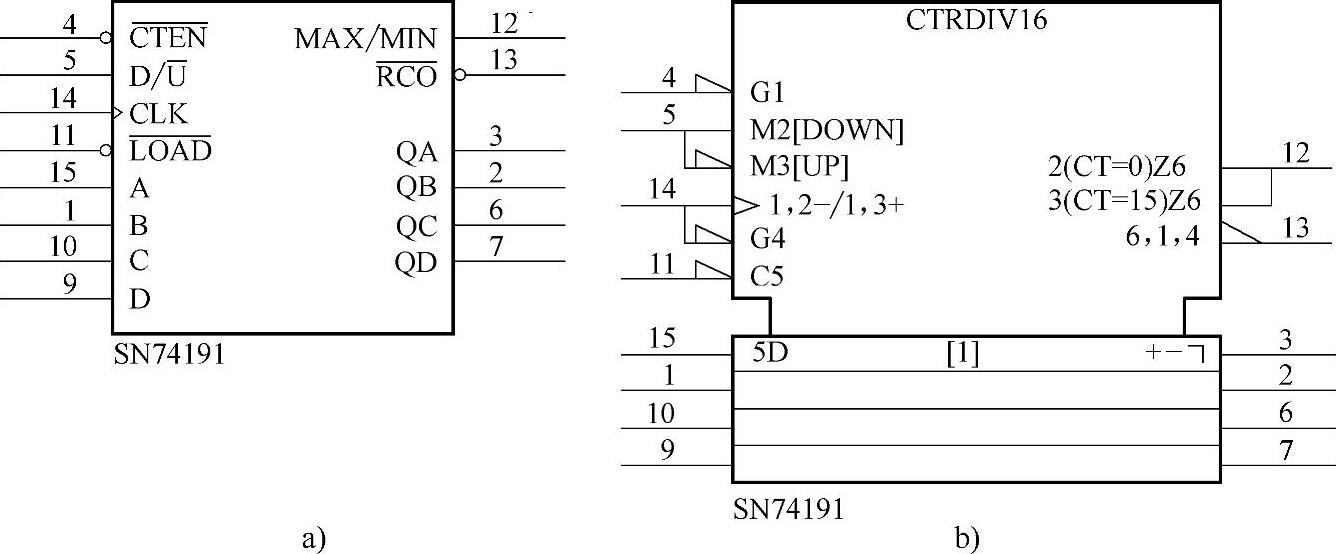

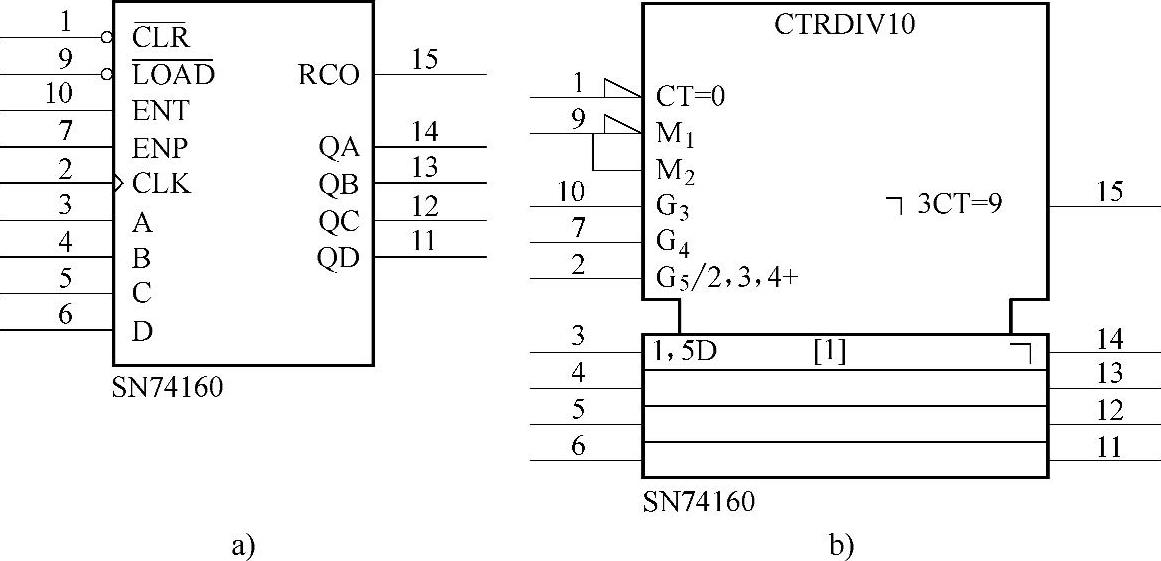

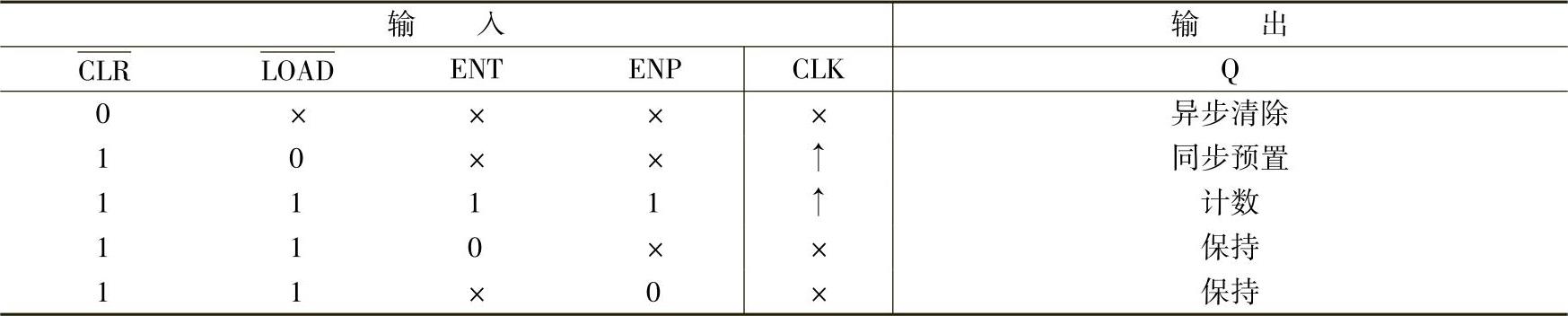

74160是可预置数十进制同步加法计数器,它的流行符号与IEEE符号如图11-30所示。

它具有数据输入端A、B、C和D,置数端L 、清除端

、清除端 和计数控制端ENT和ENP,为方便级连,设置了输出端RCO。当置数端

和计数控制端ENT和ENP,为方便级连,设置了输出端RCO。当置数端 、

、 、CP脉冲上升沿时预置数。当

、CP脉冲上升沿时预置数。当 ,而ENT=ENP=0时,输出数据和进位RCO保持。当ENT=0时,计数器保持,但RCO=0。

,而ENT=ENP=0时,输出数据和进位RCO保持。当ENT=0时,计数器保持,但RCO=0。

,电路工作在计数状态。详细功能见表11-17。

,电路工作在计数状态。详细功能见表11-17。

图11-30 74160同步十进制计数器的流行符号与IEEE符号

表11-17 74160功能表

同步二进制计数器74161的功能同74160,它也是直接清零的计数器。74190是可预置数同步可逆(加减)十进制计数器。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。