在各种复杂的数字电路中,不但需要对数字信号进行逻辑运算,还经常需要将这些信号和结果保存起来。因此,需要使用具有记忆功能的基本逻辑单元——触发器。

触发器具有两个稳定状态,即0态和1态。如果外加合适的触发信号,触发器就能从一个稳态转化到另一个稳态。

触发器从逻辑功能上,可分为RS触发器、T触发器、D触发器、JK触发器等。

图9-12 CMOS反相器及其内部结构

1.基本型RS触发器的特点

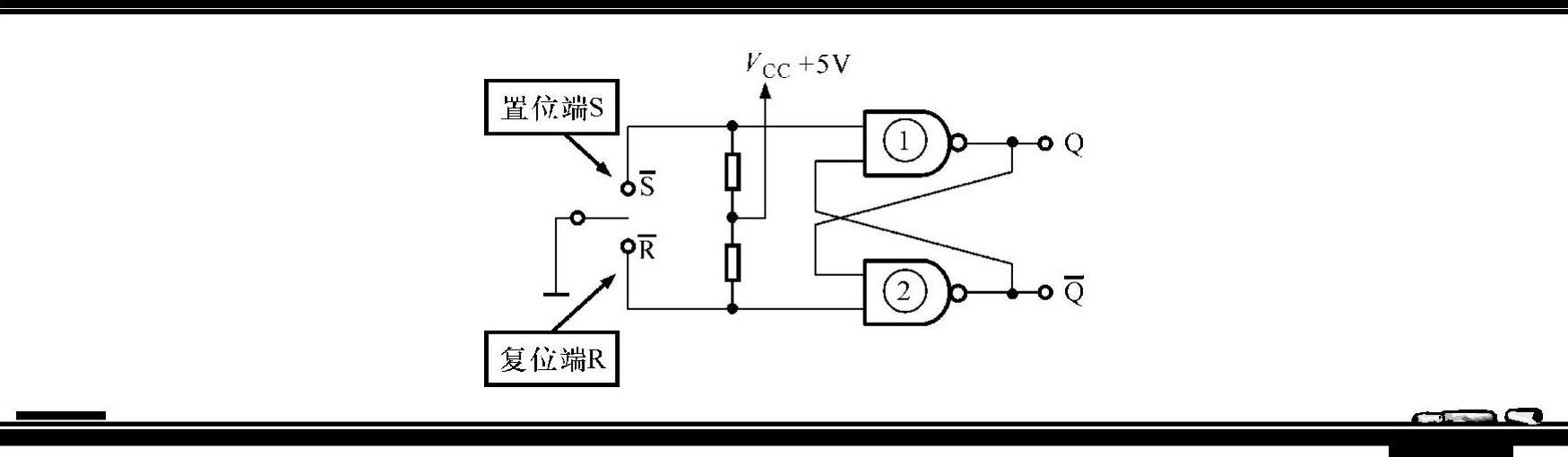

图9-13所示为RS触发器的电路结构,它可以由两个门电路构成,如两个与非门或两个异或门构成。R为复位端(REST),S为置位端(SET),输出Q和Q相反。这种触发器是非同步触发器。

图9-13 RS触发器的电路结构

图9-14为RS触发器的工作原理图。当开关既不在S端、也不在R端时,触发器的输出端是不确定的。当开关置向一侧时,就决定了触发器的输出。例如,当开关置于S端时,S端为低电平(地),R端则为高电平,与非门①的输入为低电平,与非门②的输入为高电平,这样就使触发器的Q端输出为高电平,Q的输出为低电平。

图9-14 RS触发器的工作原理

如果输入开关置于R端,则触发器会反转,Q端变成低电平,Q端变成高电平。

由此可见,输入端R、S既不可能同时为高电平,也不可能同时为低电平,只有两种状况,即其中一个为高电平而另一个为低电平,则触发器Q和Q端口也必然输出状态相反的信号。

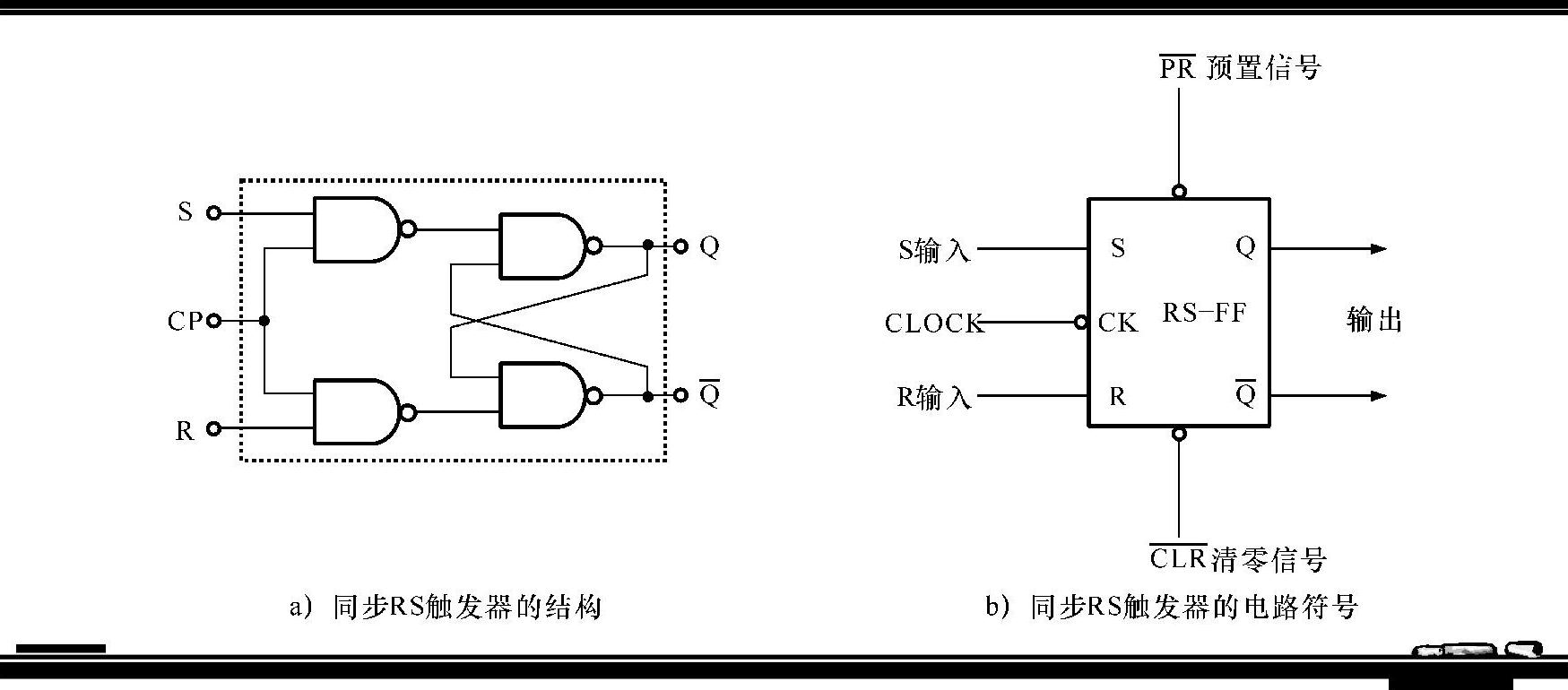

2.同步RS触发器(同步RS-FF)

基本型RS触发器属于非同步RS触发器,不能与系统中的时钟信号同步,同步RS触发器则附加了同步功能,可以与时钟信号同步工作。

图9-15所示为同步RS触发器的电路结构及电路符号。它的两个输入端用了两个与非门,并增加了一个时钟脉冲输入端(CP)。

图9-15 同步RS触发器的电路结构及电路符号

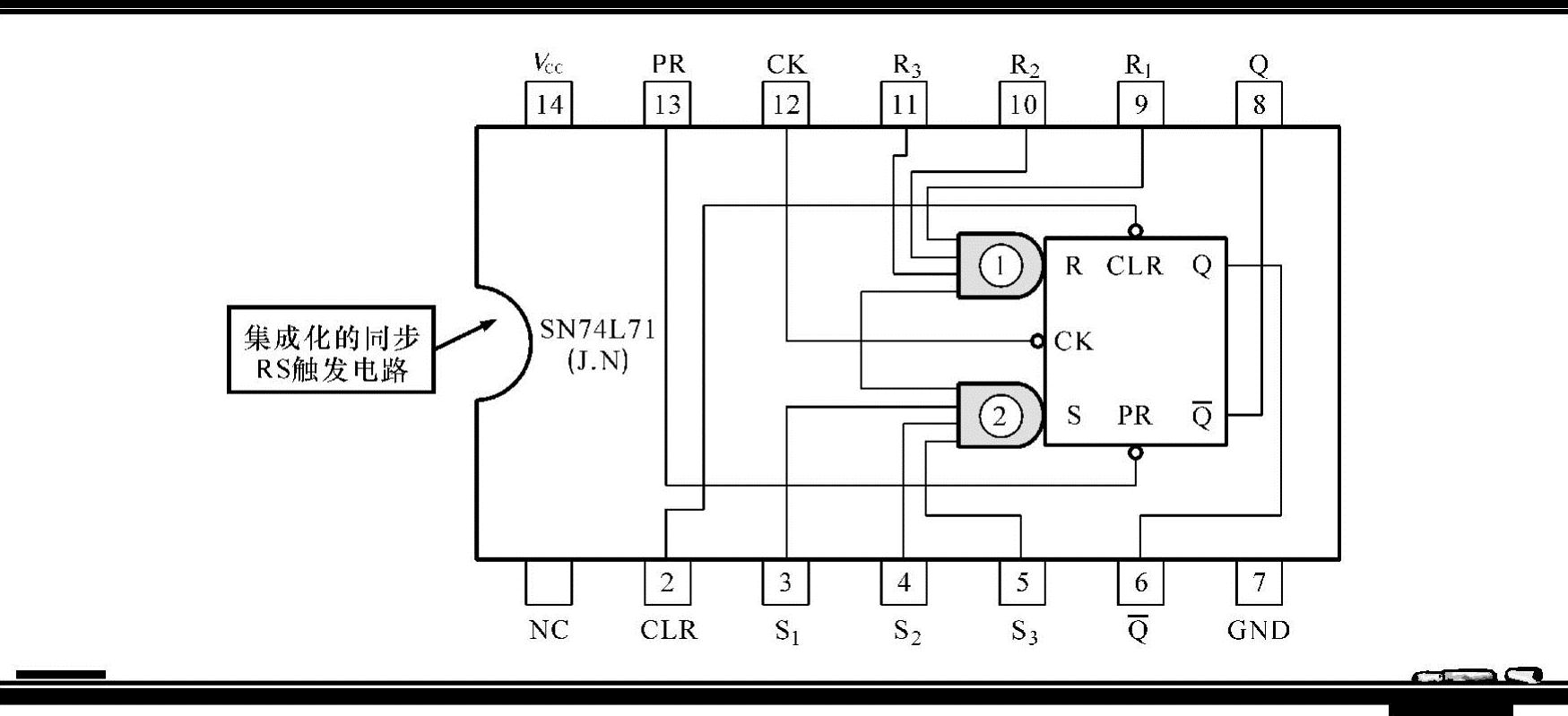

集成化的同步RS触发电路如图9-16所示。

3.T触发器(T-FF)

T触发器是一种触发式双稳态电路,它的T端是信号触发端,当信号触发端的信号发生变化时,双稳态电路的输出也会同时发生变化。

图9-17所示为T触发器的电路结构及输入和输出信号波形。由图可见,T触发器也是一个1/2分频电路,T端输入两个脉冲,而输出端则输出一个脉冲。

图9-16 集成化的同步RS触发电路

(https://www.xing528.com)

(https://www.xing528.com)

图9-17 T触发器的电路结构及输入和输出信号波形

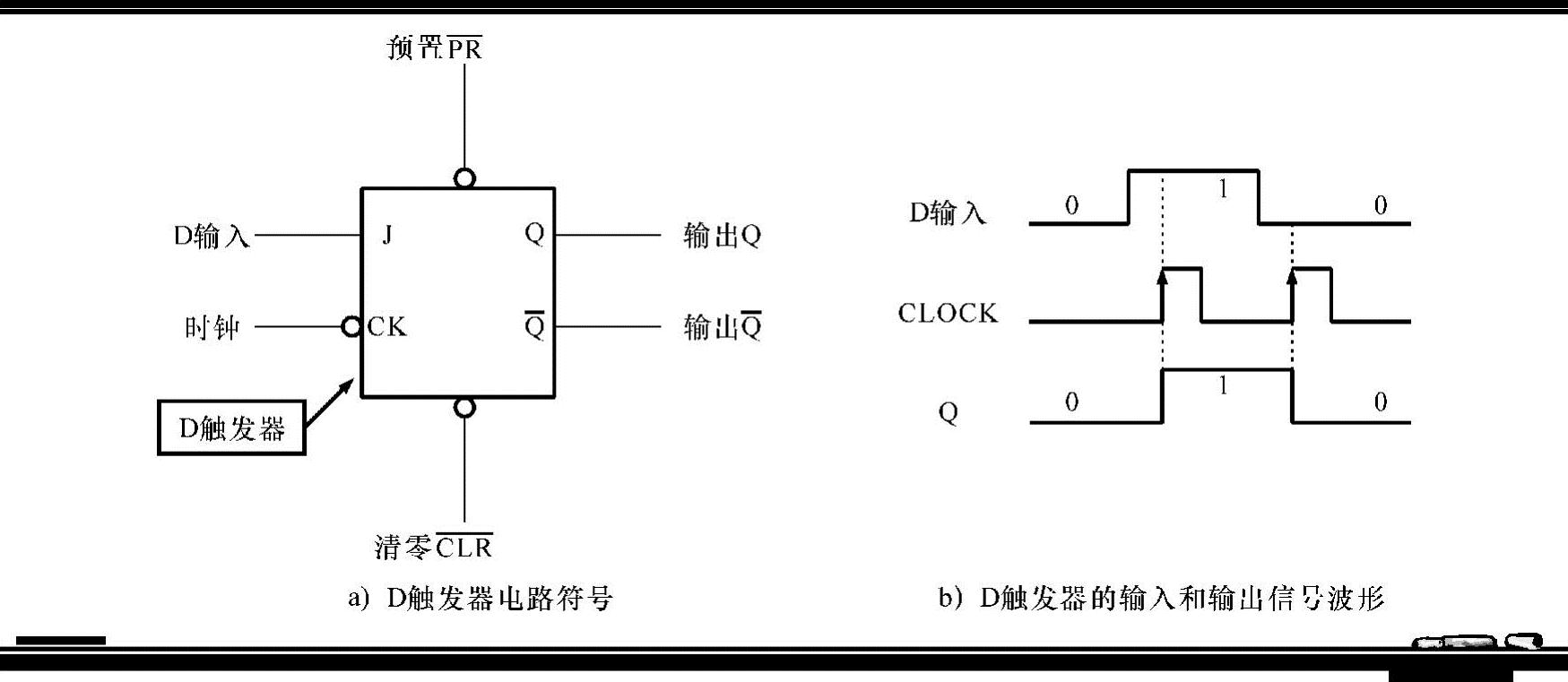

4.D触发器(D-FF)

D-FF的“D”是英文延迟之意,因而D触发器是一种延迟电路。对D触发器如果没有时钟信号,D触发端不管输入“1”还是输入“0”,触发器都不动作,只有当有时钟信号输入时才会动作。

图9-18所示为D触发器的电路符号及输入和输出信号波形。

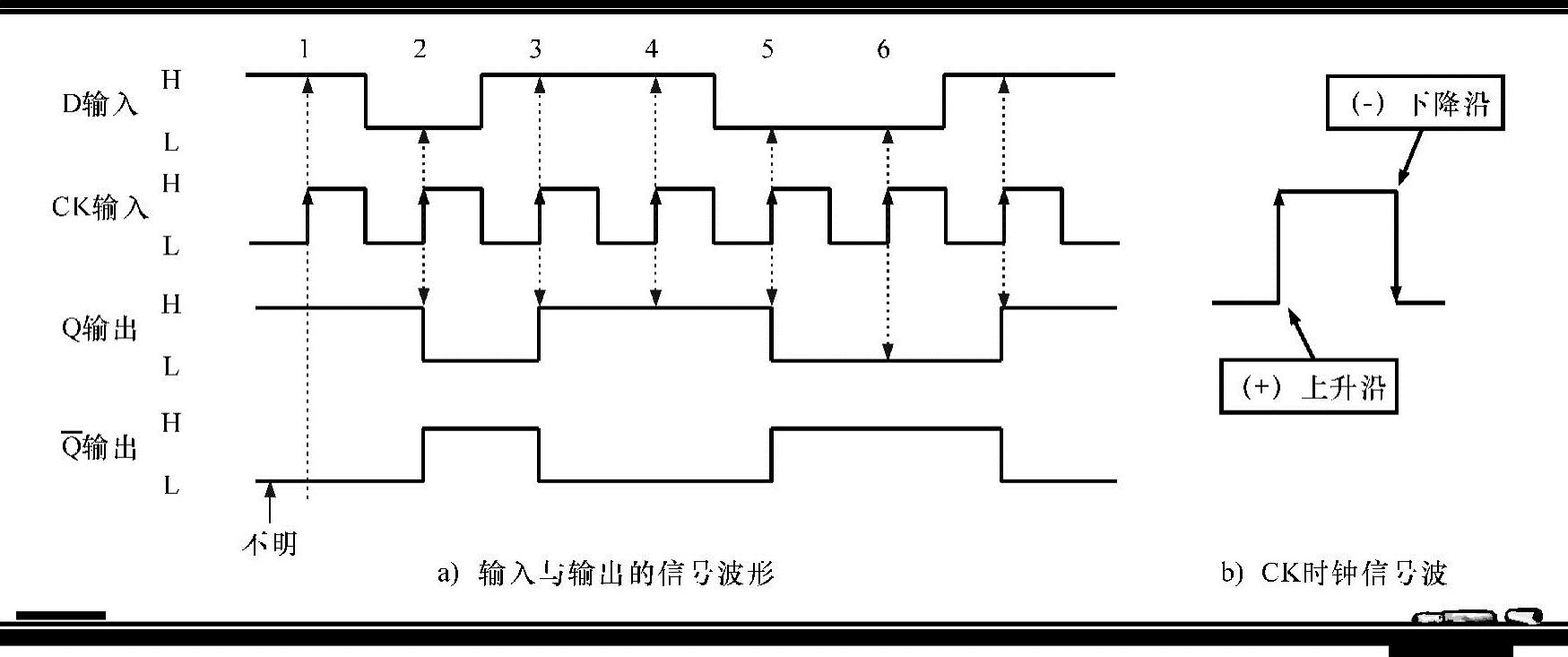

当D触发器有连续脉冲信号输入时,D触发器实际的信号波形如图9-19所示。

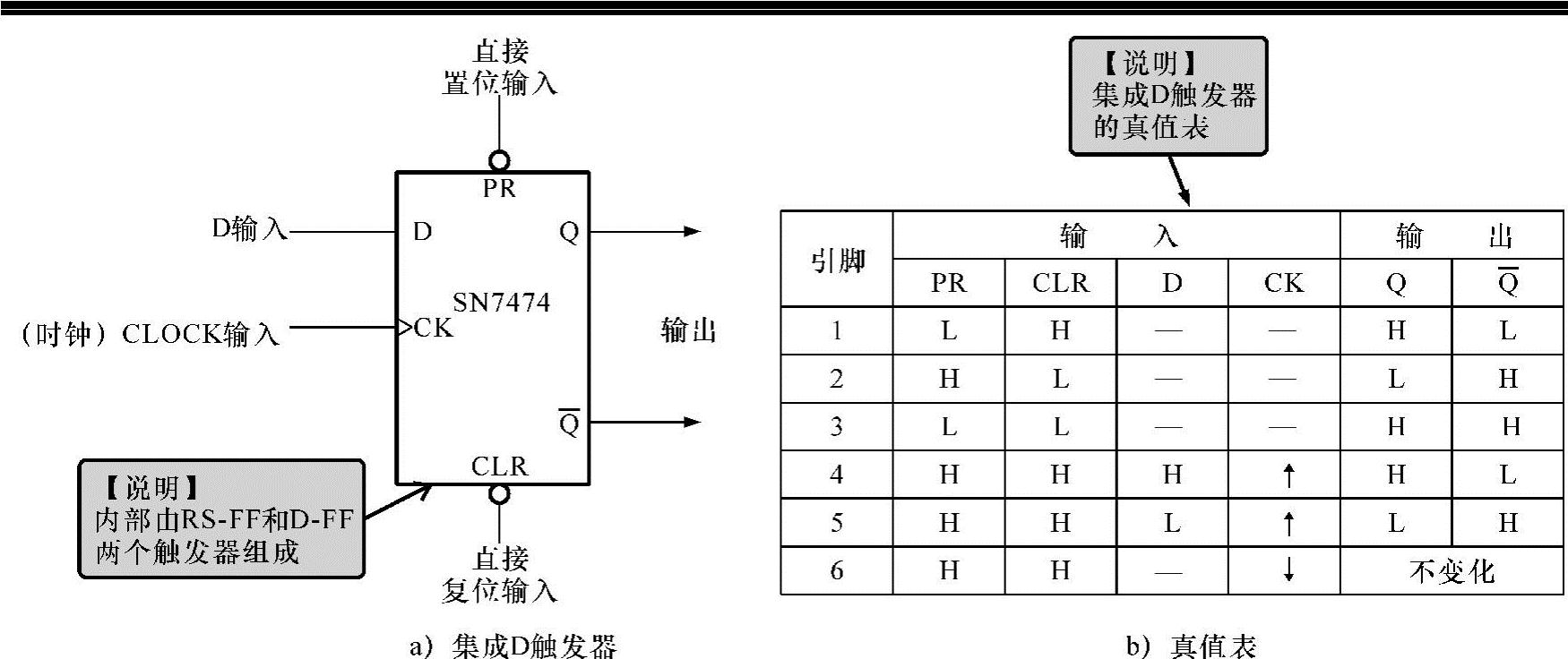

图9-20所示为集成D触发器的电路结构、真值表和信号波形。集成D触发器SN7474是由RS-FF和D-FF两个触发器组成的。

图9-18 D触发器的电路符号及输入和输出信号波形

图9-19 D触发器实际的信号波形

图9-20 集成D触发器电路结构、真值表和信号波形

图9-20 集成D触发器电路结构、真值表和信号波形(续)

5.JK触发器(JK-FF)

JK触发器是主从触发器,它有两个输入端J、K,称为主从触发信号。JK触发器的电路结构及信号波形如图9-21所示。

T-FF、D-FF、RS-FF等触发器通过简单的连接和变换可以进行变换和组合,完成所需要的功能。

图9-21 JK触发器的电路结构及信号波形

图9-21 JK触发器的电路结构及信号波形(续)

【资料】

D触发器(D-FF)同其他触发器的比较如图9-22所示。

图9-22 D触发器(D-FF)同其他触发器的比较

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。