在数字通信系统中,由于噪声和干扰的影响,在帧同步码组中会出现误码情况,这样就会发生漏同步问题;另外由于信息码中也可能会出现与帧同步码组一样的码元组合,这样就会产生假同步问题。假同步和漏同步的存在,都会使帧同步系统出现不稳定和不可靠。

在实际通信系统中,假如系统发现一个帧同步码码组就认为系统已经同步,或当出现一次漏同步就认为系统失步,那么这样的系统可能会一直在同步态和失步态之间来回转换,无法正常工作。因此,必须对帧同步系统采取一些措施进行保护,以提高帧同步的性能。对帧同步系统常采用的保护措施是将帧同步的工作状态划分为两种状态,即捕捉态和维持态。即在系统开始时或处于捕捉态(搜索态,也叫做失步态)时,通过一定的规律多次检测到帧同步信号,系统才由捕捉态转换到维持态(同步态)。在维持态时,系统不会因一次偶然的无帧同步信号而转换工作状态,而是经过多次按规律的检测,的确发现系统已经失步才转换到捕捉态,重新进行捕捉。下面针对两种不同的帧同步方法分别加以介绍。

1.在连贯式插入法中的帧同步保护

依据连贯式插入法实现帧同步的原理,从要求漏同步概率P1和假同步概率P2均要小来看,对巴克码识别器的判决门限电平的选择是相互矛盾的。当然,从系统的可靠性考虑:

在捕捉态时,能够提高识别器判决门限电平(m减少),使假同步概率P2减少;

在维持态时,减少识别器判决门限电平(m增大),使漏同步概率P1减少。

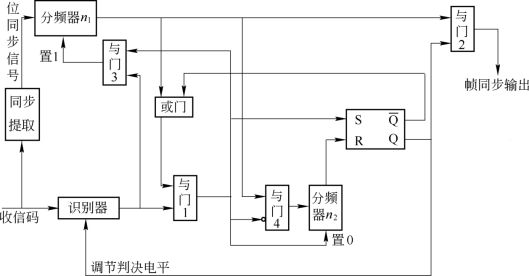

在连贯式插入法中,进行帧同步保护的原理方框图如图9.4.11所示,其主要由RS触发器、计数器、与门、或门电路组成。下面从两个工作状态来介绍其工作原理。

图9.4.11 连贯式插入法中的帧同步保护

(1)系统处于失步态

当系统处于失步态(捕捉态)时,即系统同步未建立时,RS触发器(作工作状态转换用)的Q端此时为低电平,该电平通过一个控制电路(图中未画出)来调节巴克码识别器的门限电平,低电平时,调节能力弱,这时同步码组识别器的判决电平较高,因而减小了假同步概率的发生。一旦巴克码识别器有输出脉冲,由于触发器的Q端此时为高电平,于是经或门使与门1有输出。与门1电路的输出共有3路,一路至分频器n1使之置“1”,这时分频器输出脉冲信号输入与门2电路;该脉冲信号还分出一路经过或门电路和与门1电路,其输出加至RS状态触发器,使系统由捕捉转为维持态,这时Q端变为高电平,打开与门2电路,分频器n1输出的脉冲通过与门2形成帧同步脉冲输出,因而同步建立。

(2)系统处于同步态(https://www.xing528.com)

同步建立以后,系统处于同步态(维持态)。为了提高系统的抗噪声和抗干扰的性能以减小漏同步概率,让图9.4.11中触发器在维持态时Q端输出高电平,从而降低识别器的判决门限电平,这样就可以减小漏同步概率。另外同步建立以后,若在分频器输出帧同步脉冲的时刻,识别器无输出,这可能是系统已经失去同步,也可能是由于偶然的干扰引起的,只有连续出现n2次这种情况才能认定系统已经失步。这时与门1电路连续无输出,经非门后加至与门4电路的信号便是高电平。分频器n1每输出一个脉冲信号,与门4电路就相应输出一个脉冲信号,这样连续n2个脉冲信号使计数器n2计满,随即输出一个脉冲信号至RS触发器,使状态由同步态转为捕捉态。当与门1电路不是连续无输出时,计数器n2未计满就会被置零,状态则不会转换。因此增加了系统在同步态时的抗干扰能力,从而达到了帧同步系统的保护。

同步建立以后,信息码中的假同步码组也可能使识别器有输出而造成干扰。然而在同步态下,这种假识别的输出与分频器的输出不会同时出现的。因此,这时与门1电路没有输出,不会改变RS触发器的工作状态。

2.在间歇式插入法中的帧同步保护

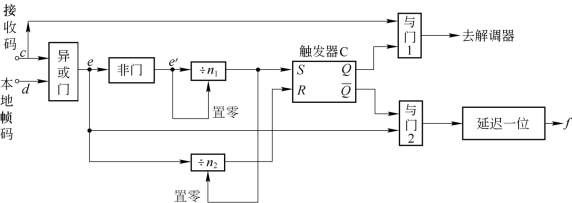

在间歇式插入法中用逐码移位法实现帧同步时,要实现帧同步系统的保护,关键是增加两个计数器n1和n2。下面仍从失步态和同步态来介绍其工作原理。

(1)系统处于失步态

在用逐码移位法实现帧同步时,由于信息码中与帧同步码组相同的码元非常多,约占一半,因而在建立帧同步的过程中,假同步的概率会非常大。解决这个问题的保护电路如图9.4.12所示。要求必须连续n1次检测到接收码元和本地帧码一致,才认为帧同步建立,这样可使假同步的概率减小。图9.4.12是在图9.4.8的基础上构成的。状态触发器在同步未建立时处于“失步态”(此时Q端为低电平),本地帧码d和接收码只有连续n1次一致时,“÷n1”电路才输出一个脉冲使状态触发器的Q端由低电平变为高电平。此时,系统由失步态转为同步态,表示同步已经建立。接收码就可通过与门1加至解调器。偶然的一致是不会使状态触发器改变状态的,因为在n1次中只要有一次不一致,就会使“÷n1”电路置零。

图9.4.12 逐位移码法帧同步保护原理图

(2)系统处于同步态(维持态)

在同步建立以后,即系统处于同步态(维持态)时,要防止漏同步以提高同步系统的抗干扰能力,这个作用是由状态触发器C和“÷n2”电路完成的。一旦转为维持状态以后,触发器C的Q端输出为低电平,将与门2电路封闭。这时即使由于某些干扰使e有输出,也不会调整本地帧码的相位。如果是真正的失步,e就会频繁不断地输出到“÷n2”电路中。同时,e也频繁不断地将“÷n1”电路置零,“÷n1”电路不会再有输出到“÷n2”电路的置零脉冲。而当“÷n2”电路输入脉冲的累计数达到n2时,就输出一个脉冲信号使状态触发器由同步态转为失步态,C触发器的Q端转为高电平。这样,一方面与门2电路打开,帧同步系统又重新进行逐码移位;另一方面封闭与门1电路,使解调器暂停工作。由此可以看出,逐码移位法帧同步系统划分为失步态和同步态后,既提高了同步系统的可靠性,又增加了系统的抗干扰能力。

在间歇式插入法中用逐码移位法实现帧同步时,两个计数器的次数n1和n2可以根据漏同步概率P1和假同步概率P2的具体要求来计算和设计。如果要求假同步概率P2要小,则计数器n1的值应该增大;如果要求帧同步系统的漏同步概率P1要小,则计数器n2的值应该增大。两个计数器的次数n1和n2的选择是在进行逐码移位法实现帧同步系统设计时的关键。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。