帧同步的实现常用以下两种方法:一种是插入特殊码组法,这种方法是在每群信息码元中(通常在开头处)插入一个特殊的码组,这个特殊的码组应该与信息码元序列有较大的区别。接收端通过识别这个特殊码组,就可以根据这些特殊码组的位置确定出群的“头”,从而实现帧同步。另一种方法不需要外加的码特殊组,它类似于载波同步和位同步的直接法,是利用信息码组本身之间彼此不同的特性来实现帧同步的。本节主要介绍插入特殊码组法实现帧同步的方法。

插入特殊码组法具体分为连贯式插入法和间歇式插入法。在介绍这两种方法之前,先介绍一种在电传机中广泛应用的起止式同步法。

1.起止式同步法

在电传报文中,一个字由7.5个码元组成,其中5个码元是信息码元,1个码元是字开始码元,1.5个码元是字结束码元。字开始码元通常用1个码元宽度的低电平表示,字结束码元通常用1.5个码元宽度的高电平表示。起止式同步法的字结构如图9.4.1所示。

图9.4.1 起止式同步法的字结构

起止式同步法的效率较低,仅为2/3,而且止脉冲的宽度与码元宽度不一致,这给数字信号的传输和识别带来了困难。因此,在一般的数字通信系统中不采用起止式同步法。

2.连贯式插入法

连贯式插入法就是在每帧的开头集中插入一个帧同步码组,接收端通过识别该特殊码组来确定帧的起始时刻的方法。该方法的关键是要找出一个特殊的帧同步码组,对这个帧同步码组的要求是:要与信息码元有较大的区别,即信息码元序列中出现帧同步码组的概率尽量小。帧同步码组要容易产生和容易识别。码组的长度要合适,不能太长,也不能太短,如果太短,会导致假同步概率的增大;如果太长,则会导致系统的效率变低。帧同步码组的长度要综合考虑。

帧同步码组最常用的形式是巴克码。

(1)巴克码

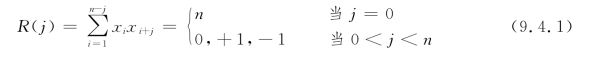

巴克码是一种具有特殊规律的二进制码组,它的特殊规律是:如果一个长度为n的巴克码{x1,x2,x3,…,xn},每个码元xi只可能取值+1或-1,则它的自相关函数为

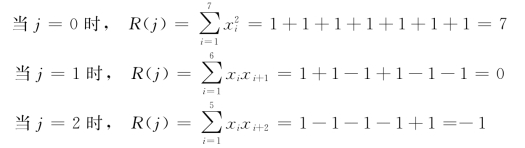

通常把这种非周期序列的自相关函数R(j)=![]() 称为局部自相关函数。常见位数较低的巴克码组如表9.4.1所示,表中“+”表示+1,“-”表示-1。

称为局部自相关函数。常见位数较低的巴克码组如表9.4.1所示,表中“+”表示+1,“-”表示-1。

表9.4.1 常见的巴克码组

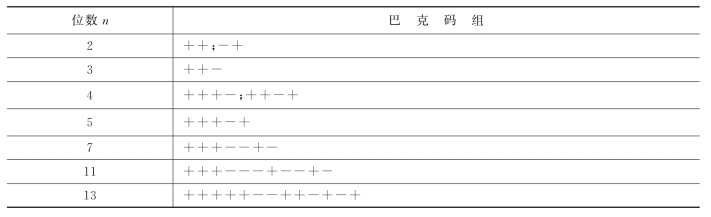

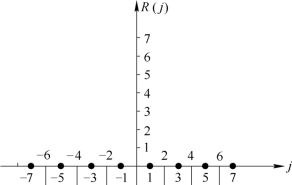

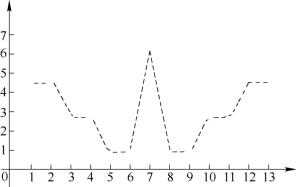

下面以n=7的巴克码为例,求出它的局部自相关函数如下:

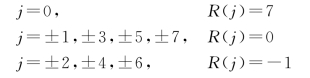

同样可以求出j=3,4,5,6,7以及j=-1,-2,-3,-4,-5,-6,-7时R(j)的值为

根据这些值,可以做出7位巴克码(+++--+-)的关系曲线,如图9.4.2所示。从图中可以看出,自相关函数在j=0时具有尖锐的单峰特性。局部自相关函数具有尖锐的单峰特性正是连贯式插入帧同步码组的主要要求之一。

图9.4.2 7位巴克码的自相关函数

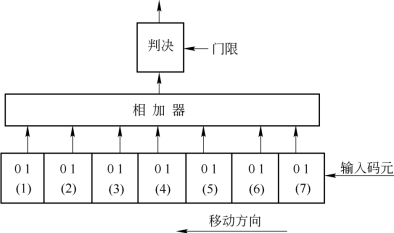

(2)巴克码识别器

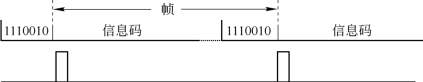

巴克码识别器是指在接收端从信息码流(信息码+巴克码)中识别出巴克码的电路。巴克码识别器一般由移位寄存器、加法器和判决器组成。以7位巴克码为例,识别器如图9.4.3所示。7级移位寄存器的1、0按照1110010的顺序接到加法器(注意各级移位寄存器接到加法器处的位置),寄存器的输出有1端和0端,接法与巴克码的规律一致。当输入码元加到移位寄存器时,若某移位寄存器中进入的是1码,该移位寄存器的1端输出为+1,0端输出为-1;反之,则该移位寄存器的1端输出为-1,0端输出为+1。

图9.4.3 7位巴克码识别器

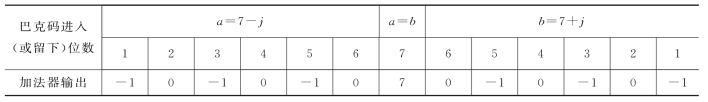

接收端接收到的信息码元自右向左逐比特进入移位寄存器,首先考虑一个简单的情况:假设只计算巴克码(1110010)进入的几个移位寄存器的输出,即不考虑巴克码前后码元的影响,此时将有巴克码进入1位,2位,…,7位全部进入,第1位移出尚留6位……前六位移出只留一位13种情况。经过计算可得加法器的输出就是自相关函数,不过要注意码元进入移位寄存器的数目a,码元尚留在移位寄存器的位数b与j的关系。例如码元只进入一位,此时a=1,相当于j=6,故a=7-j,显然七位全部进入a=7,j=0;巴克码码元全部进入后再向左移一位,此时留下六位,b=6,相当于j=-1,故b=7+j,由此可得加法器输出与a、b的关系如表9.4.2所示。

表9.4.2 7位巴克码加法器输出a、b的关系

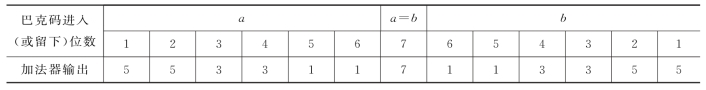

在实际数字通信系统中,帧同步码的前后都有信息码,而信息码又是随机的,若考虑一种最不利的情况,即当巴克码只有部分码在移位寄存器时,信息码占有的其他移位寄存器的输出全部是+1。在这样一种最不利的情况下,加法器的输出如表9.4.3所示,由此可得识别器的输出波形如图9.4.4所示。图中横坐标用a表示,由b=7+j,a=7-j的关系可得a=14-b。

表9.4.3 最不利时7位巴克码加法器输出a、b的关系

图9.4.4 巴克码波形(https://www.xing528.com)

通过图9.4.4可以看出,如果判决电平选择在6,就可以根据a=7时加法器输出的7,大于判决电平6而判定巴克码全部进入移位寄存器的位置。此时识别器输出一个帧同步脉冲,表示帧的开始时刻。一般情况下,信息码不会正好都使移位寄存器的输出为+1,因此实际上更容易判定巴克码全部进入移位寄存器的位置。如果7位巴克码中有一位误码,则加法器的输出将由7变为5,这个电平低于判决器的判决电平。因此为了提高帧同步的抗干扰性能,防止漏同步,判决电平可以改为4,但改为4以后假同步概率明显增大。

当信息码流进入巴克码识别器时,识别器的输出波形如图9.4.5所示。

图9.4.5 巴克码识别器的输出波形

3.间歇式插入法

(1)应用场合

连贯式插入法是在每帧的前面集中插入一组特殊的码组作为帧同步码组,它主要用在数据传输中,连贯式插入法每帧插入一次。而间歇式插入法是将帧同步码组分散地插入在帧中,即每隔一定数量的信息码元,插入一个帧同步码元。间歇式插入法比较多地用在多路数字电话系统中。数字电话主要有PCM和ΔM两种。单路数字电话如果用增量调制时,可以不需要帧同步,这是因为ΔM系统中解调器只要用一个积分器译码即可。在PCM系统中编、译码器都有定时脉冲,收、发端的定时脉冲必须同步,因此一定要用位同步。另外在多路数字电话系统中,要完成多路信号的复用,都需要帧同步,而且往往用间歇式插入法。例如,在一些数字微波设备中,帧同步就是用1、0相间的码作为帧同步码,等间隔地插入在信息流中。在PCM多路数字电话中,帧同步码可以连贯式插入也可以间歇式插入,如30/32路PCM系统中,实际上只有30路电话,另外两路中的一路专门作为插入帧同步码组用,另一路作其他插入各路信令信号及复帧同步码用。

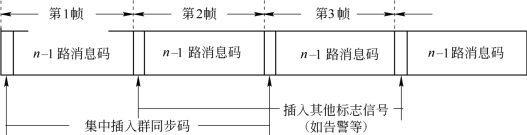

为了清楚地区分集中式插入帧同步码和分散式插入帧同步码的方法,图9.4.6和图9.4.7分别画出了一个在n路PCM系统中集中插入帧同步码的示意图和分散插入帧同步码的示意图。

图9.4.6 集中插入帧同步码

在图9.4.6中,每帧用一路专门集中插入帧同步码或其他标志信号,帧同步码和其他标志信号两者交替插入。n-1路为语音信号,如果采用8位码代表一个抽样值,则帧同步码也可以用8位码,但也可以用7位码。例如,PCM30/32路系统帧结构中,偶帧时帧同步码为0011011(第1位空着)。

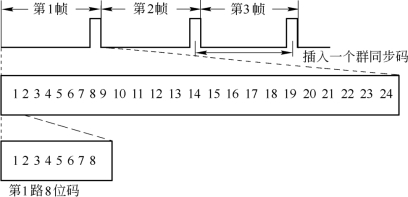

图9.4.7是一个在24路PCM系统中分散插入帧同步码的示意图,每帧共193个码元(192个信息码和一个帧同步码)。

显然,位同步频率是帧同步频率的193倍,因此帧同步频率可以通过对位同步频率进行193次分频得到。分频后的帧同步脉冲的相位不稳定,通常用逐码移位法加以调整。下面介绍逐码移位法实现帧同步的原理。

图9.4.7 分散插入帧同步码

(2)逐码移位法实现帧同步的原理

①组成

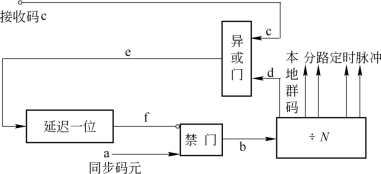

逐码移位法实现帧同步的原理方框图如图9.4.8所示,由N分频器、本地帧码(本地群码)、1比特迟延器、异或门、禁门组成。

图9.4.8 逐码移位法实现帧同步的组成

②基本原理

逐码移位法的基本原理是由位同步脉冲(位同步码)经过n次分频以后的本地帧码(频率是正确的,但相位不确定)与接收到的码元中间歇式插入的帧同步码进行逐码移位比较,使本地帧码与发送来的帧同步码同步。

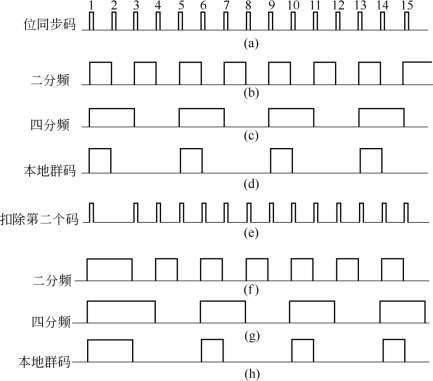

③本地帧码的产生

为了方便各点波形的画法,假定n=4,即每个帧有4个码元,其中第一个码元为帧同步码,其他三个是信息码,本地帧码由位同步码二分频波形〔如图9.4.9(b)所示〕和位同步码四分频的波形〔如图9.4.9(c)所示〕相乘得到,本地帧码的波形如图9.4.9(d)所示,是全1码。在实现电路上可以用一个与门完成,把二、四分频的输出加到与门电路即可。经过分频器得到的本地帧码,在正常情况下宽度为一个码元的宽度Tb,重复频率为位同步脉冲重复频率fb的1/n,即fb/n(图中假定是fb/4)。

如果把图9.4.9(a)中位同步码的第2个码扣除,如图9.4.9(e)所示,此时二次和四次分频波形分别变为图9.4.9(f)和图9.4.9(g)所示的波形,而本地帧码的波形如图9.4.9(h)所示。可以看出,在位同步码中扣除一个码,将使本地帧码的位置延迟一个码元的宽度。

图9.4.9 逐码移位法实现帧同步各点波形

④实现帧同步过程

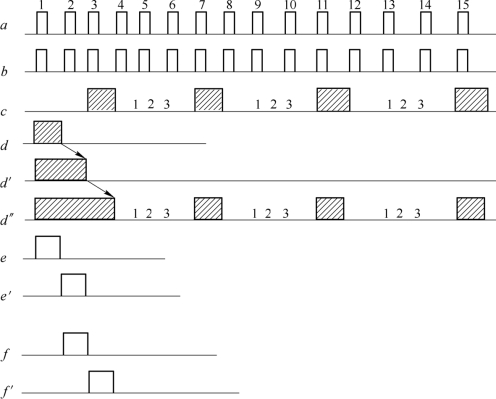

逐码移位法实现帧同步的方框图如图9.4.8所示,图中异或门、延迟一位电路和禁门是专门用来扣除位同步码以调整本地帧码的相位的,具体过程可以通过图9.4.10加以说明。

图9.4.10 逐码移位法的过程

设接收码中的帧同步码如图9.4.10中c(阴影部分)所示,后面的1、2、3表示各路的信息码,为作图方便起见只画了三个码元的位置,且没有画出它是0码还是1码。如果已经实现了帧同步,那么本地帧码的位置应该和信码中帧码的位置相同(即相位一致)。现在假设本地帧码如图9.4.10中d所示,它与接收信码中的帧码相位不一致,差两个码元的位置,即本地帧码(波形d)超前信码中的帧码(波形c)两个码元。假设信码均为0,此时接收码的波形和本地帧码的波形通过异或门得c⊕d=e(参见图9.4.8),e的波形与d一样,图9.4.8中异或门输出波形e经过1比特延迟电路后得到的波形如图9.4.10中f所示。波形f加到图9.4.8中的禁门,扣除一个位同步码,即位同步码中的第2个码元被扣除。由于位同步码中第2个码元被扣除,二分频器状态在原来第2个位同步位置处不变,在第3个位同步脉冲处发生变化,这样波形展宽了一个码元宽度,如图9.4.9(f)所示。因而本地帧码也迟后了一个码元宽度,如图9.4.10中的波形d′所示。

在位同步码元的第2个码元被扣除的时刻,图9.4.8中c与d′经过异或门,c⊕d′=e′,其波形如图9.4.10中的e′所示,e′再经过1比特延迟电路得到如图9.4.10中f′所示的波形,它使图9.4.8中的禁门扣除同步码元中的第3个码元。同理,由于同步码第3个码元的扣除,使本地帧码再展宽一个码元,如图9.4.10中的波形d″。d″再与信码c一起通过图9.4.8中的异或门得输出为0,不再扣除同步码元,此时本地帧码与信码中的帧码位置对准,从而实现了帧同步。

在实现了帧同步后,系统会依据一定的规律产生出各分路定时脉冲,它们与信码相与就会把各路信号从信息码流中区分出来。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。