ARM Cortex-M3是一种基于ARM7v架构的最新ARM嵌入式内核,它采用哈佛结构,使用分离的指令和数据总线。ARM公司对Cortex-M3的定位是向专业嵌入式市场提供低成本、低功耗的芯片。在成本和功耗方面,Cortex-M3具有相当好的性能,和所有的ARM内核一样,ARM公司将内该设计授权给各个制造商来开发具体的芯片。迄今为止,已经有多家芯片制造商开始生产基于Cortex-M3内核的微控制器。目前Cortex-M3处理器内核的授权客户包括东芝、ST、Ember、Accent、Actel、ENERGY、ADI、NXP、TI、Atmel、Broadcom、Sam-sung、Zilog和Renesas等,其中ST、TI、NXP、Atmel和东芝等已经推出基于Cortex-M3的MCU产品。

1.Cortex-M3内核介绍

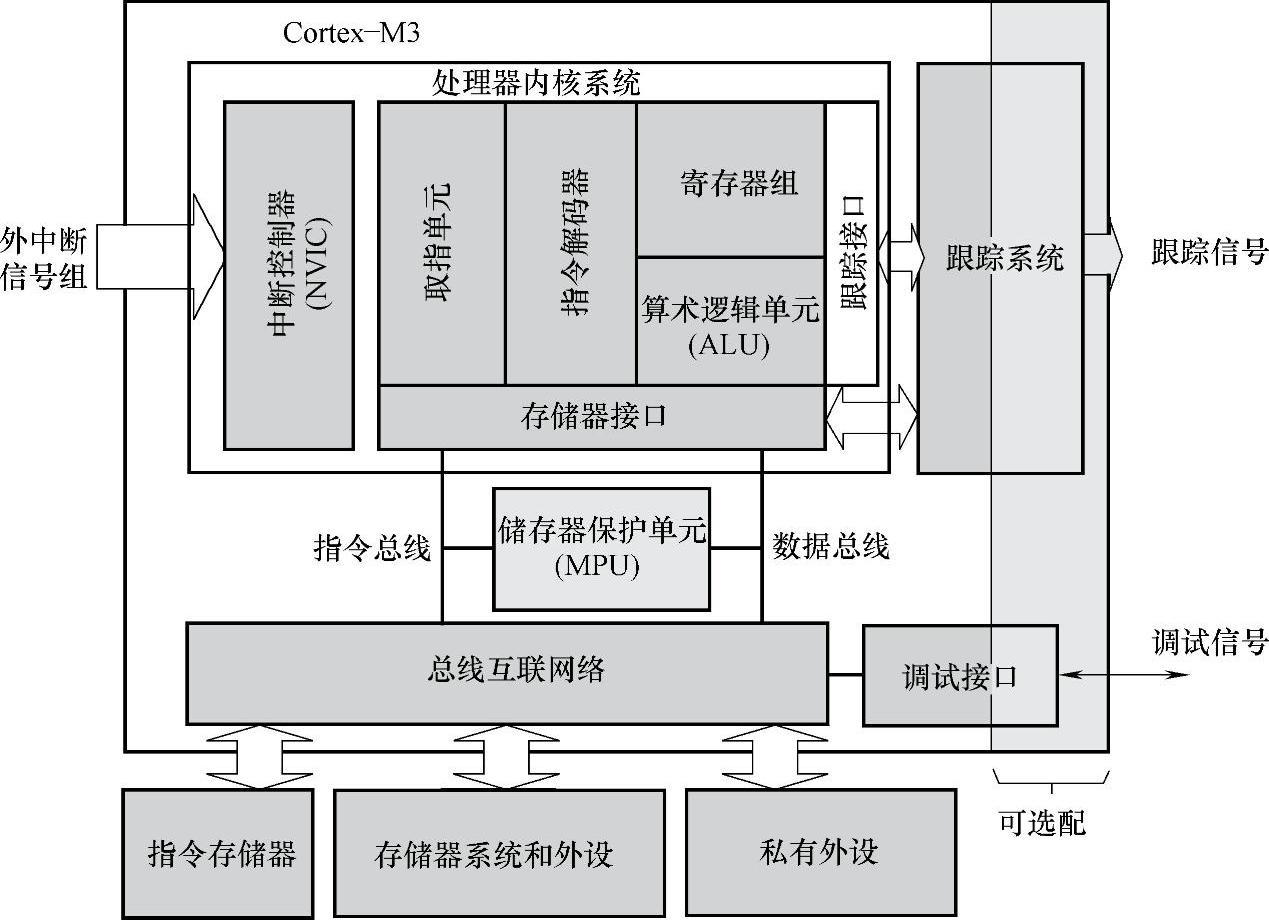

Cortex-M3处理器是一个32位的处理器。内部的数据路径是32位的,寄存器是32位的,寄存器接口也是32位的。基于ARMv7架构的Cortex-M3处理器带有一个分级结构。它集成了名为CM3Core的中心处理器内核和先进的系统外设,实现了内置的中断控制、存储器保护以及系统的调试和跟踪功能。这些外设可进行高度配置,允许Cortex-M3处理器处理大范围的应用并更贴近系统的需求。

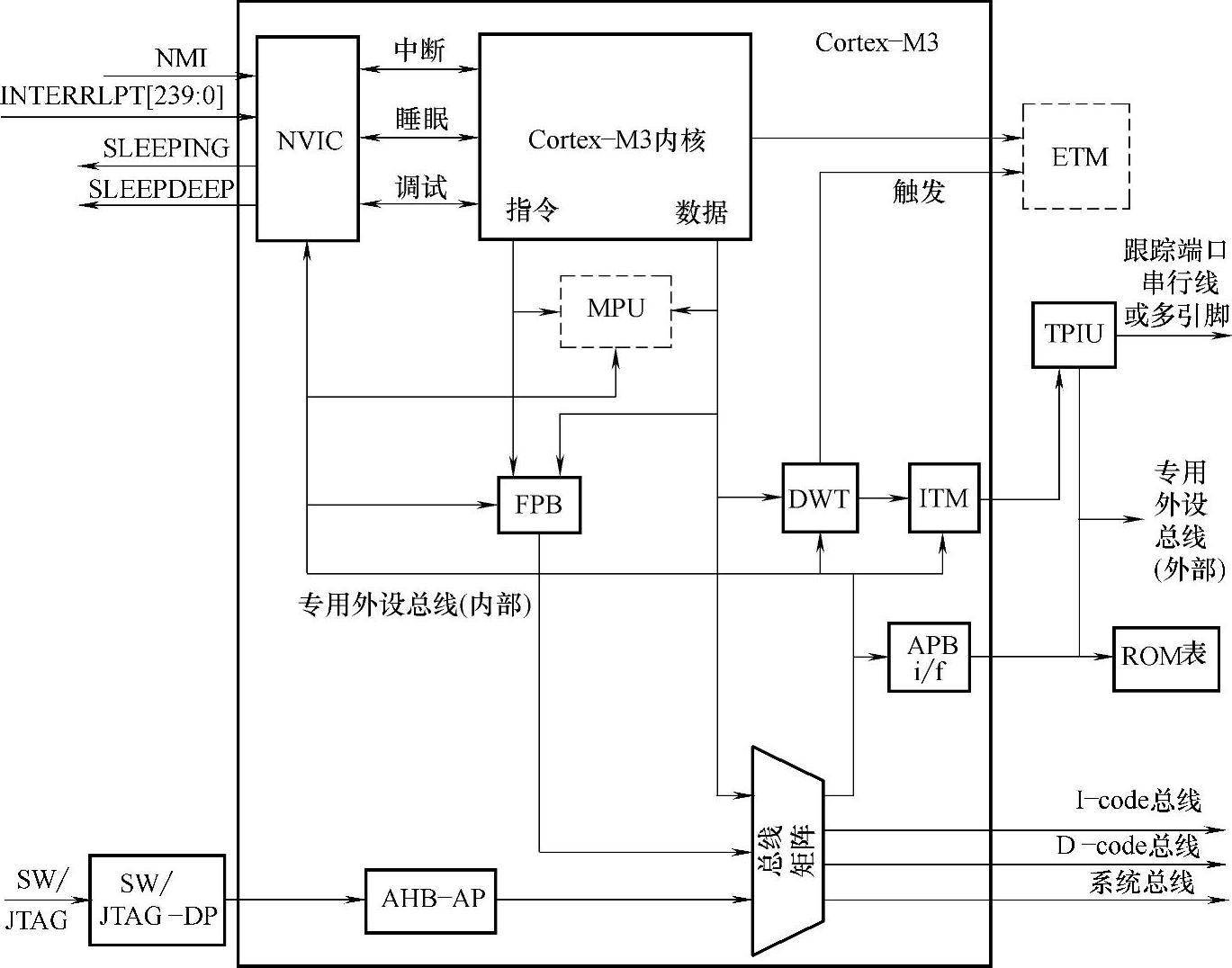

Cortex-M3中央内核基于哈佛架构,指令和数据各使用一条总线,所以Cortex-M3处理器对多个操作可以并行执行,加快了应用程序的执行速度。内核流水线分3个阶段:取指、译码和执行。当遇到分支指令时,译码阶段也包含预测的指令取指,这提高了执行的速度。处理器在译码阶段自行对分支目的地指令进行取指。在稍后的执行过程中,处理完分支指令后便知道下一条要执行的指令。如果分支不跳转,那么紧跟着的下一条指令随时可供使用。如果分支跳转,那么在跳转的同时分支指令可供使用,空闲时间限制为一个周期。Cortex-M3内核图如图3-5所示,其模块框图如图3-6所示。

Cortex-M3内核包含一个适用于传统Thumb和新型Thumb-2指令的译码器、一个支持硬件乘法和硬件除法的先进ALU、控制逻辑和用于连接处理器其他部件的接口。Cortex-M3处理器是一个32位处理器,带有32位宽的数据路径,寄存器库和存储器接口。其中有13个通用寄存器,两个堆栈指针,一个链接寄存器,一个程序计数器和一系列包含编程状态寄存器的特殊寄存器。Cortex-M3处理器支持两种工作模式[线程(Thread)和处理器(Han-dler)]和两个等级的访问形式(有特权或无特权),在不牺牲应用程序安全的前提下实现了对复杂的开放式系统的执行。无特权代码的执行限制或拒绝对某些资源的访问,如某个指令或指定的存储器位置。Thread是常用的工作模式,它同时支持享有特权的代码以及没有特权的代码。当异常发生时,进入Handler模式,在该模式中所有代码都享有特权。

基于传统ARM7处理器的系统只支持访问对齐的数据,只有沿着对齐的字边界才可以对数据进行访问和存储。Cortex-M3处理器采用非对齐数据访问方式,使非对齐数据可以在单核访问中进行传输。当使用非对齐传输时,这些传输将转换为多个对齐传输,但这一过程不为程序员所见。

图3-5 Cortex-M3的内核图

图3-6 Cortex-M3模块框图

Cortex-M3处理器除了支持单周期32位乘法操作之外,还支持带符号的和不带符号的除法操作,这些操作使用SDIV和UDIV指令,根据操作数大小的不同在2~12个周期内完成。如果被除数和除数大小接近,那么除法操作可以更快地完成。Cortex-M3处理器凭借着这些在数学能力方面的改进,成为了众多高数字处理强度应用(如传感器读取和取值或硬件在环仿真系统)的理想选择。

2.Cortex M3应用与编程

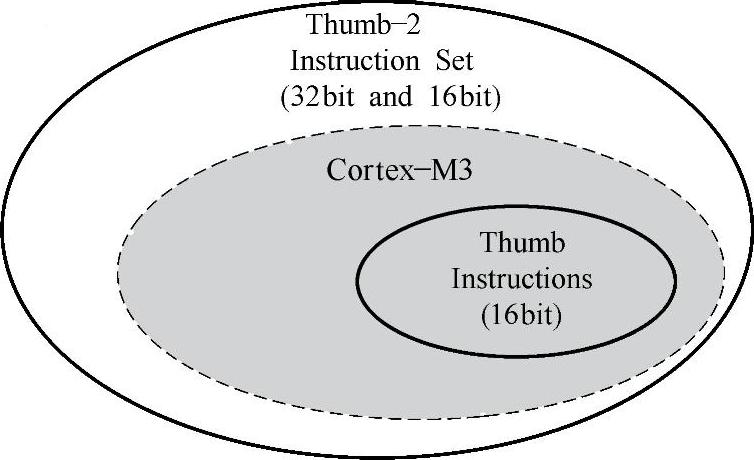

Cortex M3只使用Thumb-2指令集,它允许32位指令和16位指令同时,代码密度与处理性能大幅提高。以前的ARM开发必须处理好两个状态,它们是32位的ARM状态和16位的Thumb状态。当处理器在ARM状态下时,所有的指令均是32位的(甚至是个“NOP”指令),此时性能相当高。而在Thumb状态下,所有的指令均是16位的,代码密度提高了一倍。不过,Thumb状态下的指令功能只是ARM下的一个子集,结果可能需要更多条的指令去完成相同的工作,导致处理性能下降。为了取长补短,很多应用程序都混合使用ARM和Thumb代码段。然而,这种混合使用是有额外开销(overhead)的,时间上的和空间上的都有,主要发生在状态切换之时。另一方面,ARM代码和Thumb代码需要以不同的方式编译,这也增加了软件开发管理的复杂度。

伴随着Thumb-2指令集的横空出世,终于可以在单一的操作模式下完成所有处理了。事实上,Cortex-M3内核干脆都不支持ARM指令,中断也在Thumb状态下处理(以前的ARM总是在ARM状态下处理所有的中断和异常)。它使Cortex-M3在许多方面都比传统的ARM处理器更先进:

1)消灭了状态切换的额外开销,节省了boot执行时间和指令空间。

2)不再需要把源代码文件分成按ARM编译的和按Thumb编译的,软件开发的管理大大减负。(https://www.xing528.com)

3)无需再反复地求证和测试。

图3-7为Thumb-2指令集与Thumb指令集的关系。

图3-7 Thumb-2指令集与Thumb指令集的关系

ARM Cortex-M处理器提供优于8位和16位体系结构的代码密度。这在减少对内存的需求和最大限度地提高芯片上闪存的使用率方面具有很大的优势,主要表现在以下几个方面。

(1)指令宽度

认为8位微控制器使用8位指令,基于ARM Cortex-M处理器的微控制器使用32位指令,这是一种常见的误解。事实上,PIC18和PIC16指令宽度分别是16位和14位。对于8051体系结构,虽然某些指令的长度为1B,但许多其他指令的长度为2B或3B。通常,对于16位体系结构也是如此,其中某些指令可能占用6B或更多内存。

ARM Cortex-M3和Cortex-M0处理器利用可提供极佳代码密度的ARM Thumb-2技术。借助于Thumb-2技术,Cortex-M处理器可以支持已扩展为包括更强大的32位指令的16位Thumb指令的根本基础。在许多情况下,C语言编译器将使用16位版本的指令,除非使用32位版本可以更有效地执行运算。

(2)指令效率

在许多情况下,单个Thumb指令可相当于数个8/16位微控制器指令;这意味着Cortex-M设备的代码量更少,因此可以更低的总线速度完成同一任务。必须注意,Cortex-M处理器支持8位和16位数据传输,可以有效利用数据内存。这意味着程序员可以继续使用它们在面向8/16位的软件中使用的相同数据类型。

(3)能效优势

对不断增加连接(例如,USB、蓝牙和IEEE 802.15)、具有复杂模拟传感器(例如,加速计和触摸屏)且成本日益降低的产品的需求,已导致需要将模拟设备与数字功能更紧密地集成,以对数据进行预处理和传输。大多数8位设备在不显著增加频率(并因此不显著增加功率)的情况下不提供支持这些任务的性能,因此嵌入式开发人员需要寻找具有更高级处理器技术的替代设备。16位设备以前曾被用来解决微控制器应用中的能效问题。但是,16位设备相对不高的性能意味着它们通常需要较长的活动工作周期或较高的时钟频率才能完成32位设备所完成的相同任务。

(4)使软件开发更加容易

基于ARM Cortex处理器的微控制器的软件开发可能比8位微控制器产品的开发容易得多。Cortex处理器不但是完全可通过C语言进行编程的,而且还附带各种高级调试功能以帮助定位软件中的问题。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。