该类规则用于设置信号完整性所涉及的各项要求,如对信号上升沿、下降沿等的要求,这里的设置会影响到电路的信号完整性仿真,下面对其进行简单介绍。

(1)“Signal Stimulus”信号激励规则

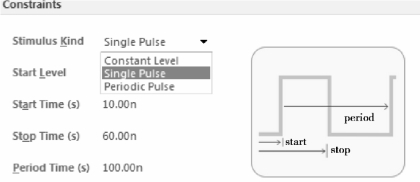

在信号激励规则中可以设置信号完整性分析和仿真时的激励,用来模拟实际信号传输的情况。在分析时,软件将此激励加到被分析网络的输出型管脚上,如图6-79所示。

图6-79 “Signal Stimulus”设置

“Stimulus Kind”:信号分析时的激励形式。有单脉冲、恒定电平激励、周期脉冲激励。默认为单脉冲。

“Stimulus Kind”:信号分析时的激励形式。有单脉冲、恒定电平激励、周期脉冲激励。默认为单脉冲。

“Start Level”:激励信号初始电平,可高可低,默认为低电平。

“Start Level”:激励信号初始电平,可高可低,默认为低电平。

“Start Time”:激励信号开始发生时间,默认值为10 ns。

“Start Time”:激励信号开始发生时间,默认值为10 ns。

“Stop Time”:激励停止时间,默认为60 ns。

“Stop Time”:激励停止时间,默认为60 ns。

“Period Time”:激励信号周期,默认为100 ns。

“Period Time”:激励信号周期,默认为100 ns。

(2)“Overshoot-Falling Edge”下降沿过冲规则

此规则设置信号分析时允许的最大下降沿过冲,过冲值是最大下降沿过冲和低电平振荡摆的中心电平的差值,设置如图6-80所示。

图6-80 “Overshoot-Falling Edge”设置

图6-81 “Overshoot-Rising Edge”设置

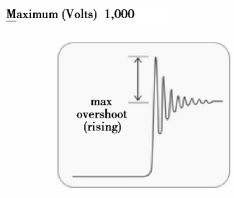

(3)“Overshoot-Rising Edge”上升沿过冲规则

此规则设置信号分析时允许的最大上升沿过冲,过冲值是最大上升沿过冲和高电平振荡摆的中心电平的差值。设置如图6-81所示。

(4)“Undershoot-Falling Edge”下降沿下冲规则

此规则设置信号分析时允许的最大下降沿下冲,下冲值是最大下降沿下冲和低电平振荡摆的中心电平的差值。设置如图6-82所示。

图6-82 “Undershoot-Falling Edge”设置

图6-83 “Undershoot-Rising Edge”设置

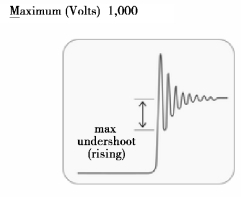

(5)“Undershoot-Rising Edge”上升沿下冲规则

此规则设置信号分析时允许的最大上升沿下冲,下冲值是最大上升沿下冲和高电平振荡摆的中心电平的差值。设置如图6-83所示。

(6)“Impedance”网络阻抗规则

设置信号分析时允许的最大、最小网络阻抗。(https://www.xing528.com)

(7)“Signal Top Value”信号高电平规则

此规则可以设置信号分析时所用高电平的最低数值,只有超过了这个电平才被看作高电平。设置情况如图6-84所示。

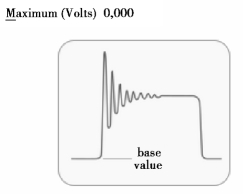

(8)“Signal Base Value”信号低电平规则

此规则可以设置信号分析时所用低电平的最高数值,只有低于这个电平才被看作低电平。设置情况如图6-85所示。

图6-84 “Signal Top Value”设置

图6-85 “Signal Base Value”设置

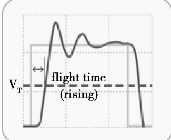

(9)“Flight Time-Rising Edge”上升沿延迟时间规则

此规则可以设置信号分析时的上升沿驱动实际输入到阈值电压的时间与驱动一个参考负荷到阈值电压的时间的差值。这个差值和信号传输的延迟有关,因此会受到传输线负载大小的影响,如图6-86所示。

图6-86 “Flight Time-Rising Edge”设置

(10)“Flight Time-Falling Edge”下降沿延迟时间规则

此规则可以设置信号分析时的下降沿驱动实际输入到阈值电压的时间与驱动一个参考负荷到阈值电压的时间的差值。这个差值和信号传输的延迟有关,因此会受到传输线负载大小的影响,如图6-87所示。

图6-87 “Flight Time-Falling Edge”设置

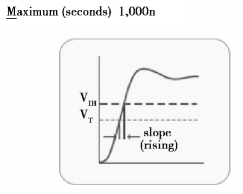

图6-88 “Slope-Rising Edge”设置

(11)“Slope-Rising Edge”上升沿的斜率规则

此规则可以设置信号分析时的上升沿的斜率,即信号从阈值电压VT上升到一个有效的高电平VIH的时间。这条规则可规定允许范围内的最大斜率值,如图6-88所示。

(12)“Slope-Falling Edge”下降沿的斜率规则

此规则可以设置信号分析时的下降沿的斜率,即信号从阈值电压VT下降到一个有效的低电平VIL的时间。这条规则可规定允许范围内的最大斜率值,如图6-89所示。

图6-89 “Slope-Falling Edge”设置

(13)“Supply Nets”电源网络规则

此规则可以为信号分析规定具体的电源网络,并输入其数值。要想进行信号分析则需要指定PCB文件中的电源网络,并且设置各个网络的电压。

从以上对PCB布线规则的说明可知,Altium Designer 17对PCB布线作了全面规定。这些规定只有一部分运用在元件的自动布线中,而所有规则将运用在PCB的DRC检测中。在对PCB手动布线时可能会违反设定的DRC规则,在对PCB板进行DRC检测时将检测出所有违反这些规则的地方。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。