Electrical Rule Check,电路规则检查,简称ERC,是电路设计完成后必不可少的一步。

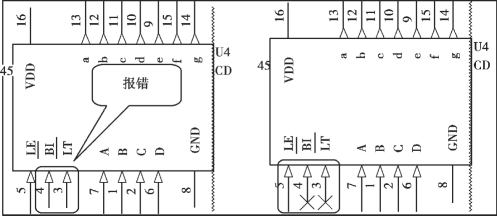

ERC可以帮助设计者找出电路中常见的连接错误。但有时候,设计者并不需要对所有的器件或连接进行ERC检查,只要在不需要进行ERC的器件引脚上放置No ERC标记就能避开检查。如图3-74所示,单片机系统中的CD4011芯片BI和LT两个输入引脚并没有信号输入导致了系统编译报错,我们可以放置No ERC标记来避免这种错误。选择“Place”|“Directives”下的“No ERC”命令,将鼠标上粘附的红色“×”标记放置在报错的引脚上再次编译,系统就不再报错了。

图3-74 No ERC效果

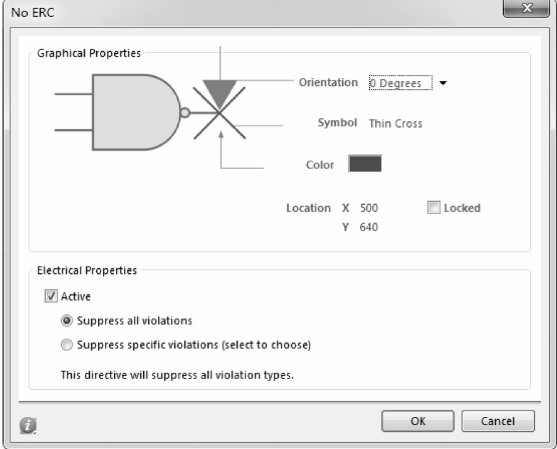

双击No ERC标记进入No ERC标记属性设置对话框,如图3-75所示,只需设置标记的颜色和位置即可。

图3-75 No ERC标记属性设置

No ERC标记可以对单个器件的引脚错误规则检查进行屏蔽,当有大量不同器件的不同错误需要屏蔽检查怎么办?这时可以使用编译屏蔽“Compile Mask”工具,它可以告诉编译器在指定的区域内不进行规则检查。(https://www.xing528.com)

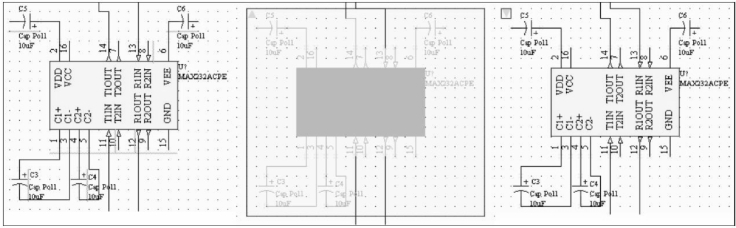

如图3-76所示的电路中,用于单片机与上位机通信的MAX232有管脚未连接和未定义标号等多种错误,若要用No ERC标记来屏蔽检查显然不可能。选取“Place”|“Directives”下的“Compile Mask”命令,此时光标上会粘附一个矩形选框,用光标在所要屏蔽的区域拉出合适大小的屏蔽区域,则选框内所有的错误都将被屏蔽,同时选框内所有被屏蔽的元件和导线连接等都呈暗灰色显示。

图3-76 编译屏蔽效果

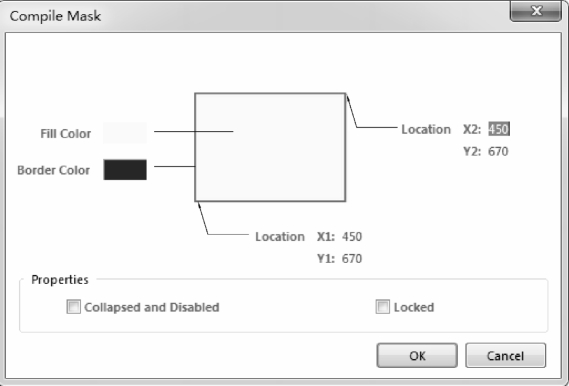

双击暗灰色的屏蔽层,在弹出的属性对话框中设置编译屏蔽的属性,如图3-77所示。在此可以设置屏蔽层的填充颜色(默认为暗灰色)和边框颜色,以及矩形的对角点位置。

编译屏蔽还有一个特殊的属性设置,那就是“Collapsed and Disabled”,即取消编辑屏蔽。选取此项后,屏蔽层将会收叠呈小三角形形状,如图3-76的最右图所示,同时,屏蔽功能也失效。其实,在编辑区内直接点击屏蔽层左上角的小三角形就能使屏蔽层消失,取消编译屏蔽;再次点击则恢复屏蔽功能。

图3-77 编译屏蔽属性设置

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。