【摘要】:图4-40 基本的采样保持电路采样保持电路用于对信号定期进行采样,并且将采样值保持到下一次采样,如此往复总是保持新的电平。基本的采样保持电路如图4-40所示。图4-41 改进的采样保持电路在组成实际电路时,要选用偏置电流小的集成运放和漏电流小的场效应晶体管,并选漏电小的电容器,以保证其精度。

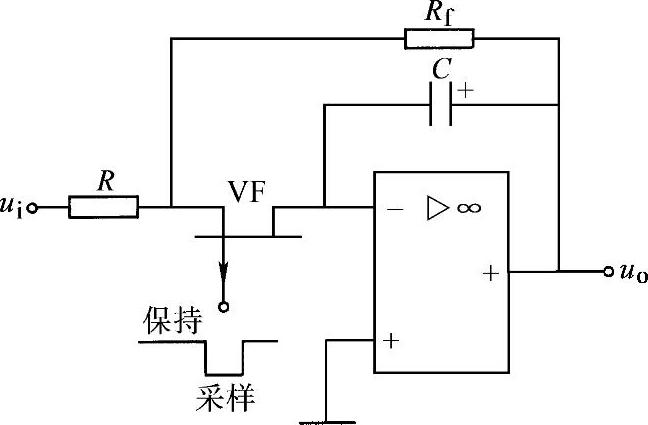

图4-40 基本的采样保持电路

采样保持电路用于对信号定期进行采样,并且将采样值保持到下一次采样,如此往复总是保持新的电平。基本的采样保持电路如图4-40所示。在电路中,场效应晶体管VF作为开关,其栅极是控制端。当控制端为低电平时,VF处于导通状态,输入信号ui通过R和VF向C充电。如果选R=Rf且忽略VF的UDS,则经过5倍时间常数(即5RC)的时间后,输出电压|uo|≈uC≈ui,即实现了采样。当控制端为高电平时,VF截止,ui就被保持在电容器的两端。

图4-40所示的采样保持电路存在两个问题:第一,采样的时间取决于RC的值,如果在采样期间信号有显著的变化,则采样所得到的数据将有较大的误差。第二,由于集成运放有偏置电流IB的存在和电容器的漏电作用,uC将逐渐改变其原有的数值,使精度下降,故应对电路进行改进。

图4-41所示为改进的采样保持电路,输入信号ui经运放A1隔离后直接通过VF2向电容器C1充电,这样可缩短充电的时间;再将相同容量的电容器C2(即C2=C1)接在运放A2的反相输入端和输出端之间,当uC1下降时,uC2将做同样的上升,使输出电压uo基本维持不变。(https://www.xing528.com)

图4-41 改进的采样保持电路

在组成实际电路时,要选用偏置电流小的集成运放和漏电流小的场效应晶体管,并选漏电小的电容器,以保证其精度。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。