时序逻辑电路简称时序电路,它由逻辑门电路和触发器组成,是一种具有记忆功能的逻辑电路。其输出状态不仅与该时刻的输入变量有关,而且与过去的输出状态有关。

锁存器与触发器是两类典型的双稳态器件。双稳态器件有两个稳定的状态,分别为置位和复位,或者说是1和0。由于双稳态器件可以永久地保存在1或0上,所以特别适合构成存储器。

2.2.1 锁存器

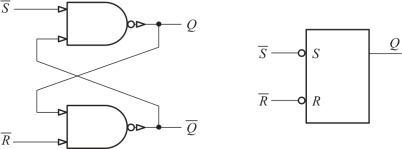

锁存器是一种双稳态器件,或者说是多谐振荡器。图8-21所示为![]() 锁存器结构,由两个与非门交叉耦合组成,

锁存器结构,由两个与非门交叉耦合组成,![]() 和

和![]() 是信号输入端,

是信号输入端,![]() 和

和![]() 为输出端。

为输出端。![]() 锁存器中任意一个与非门的输出与另一个与非门的输入相连以形成负反馈——这是所有锁存器和触发器的特征所在。

锁存器中任意一个与非门的输出与另一个与非门的输入相连以形成负反馈——这是所有锁存器和触发器的特征所在。

图8-21  锁存器

锁存器

在正常条件下两个输出端Q和![]() 状态相反。一般用输出端Q代表锁存器的输出,即当Q=1时,锁存器为置位状态;当Q=0时,锁存器为复位状态。表8-13所示为

状态相反。一般用输出端Q代表锁存器的输出,即当Q=1时,锁存器为置位状态;当Q=0时,锁存器为复位状态。表8-13所示为![]() 锁存器真值表。

锁存器真值表。

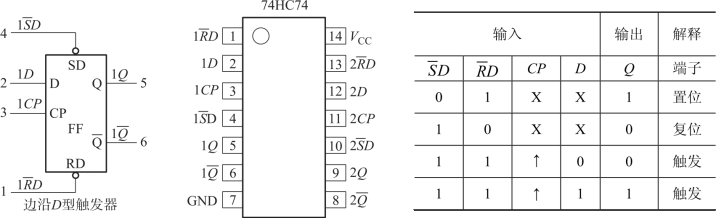

表8-13  锁存器真值表

锁存器真值表

2.2.2 边沿触发器(https://www.xing528.com)

与锁存器不同,边沿触发器多了一个时钟脉冲输入端(CP),并只会在时钟脉冲的上升沿或下降沿中翻转。

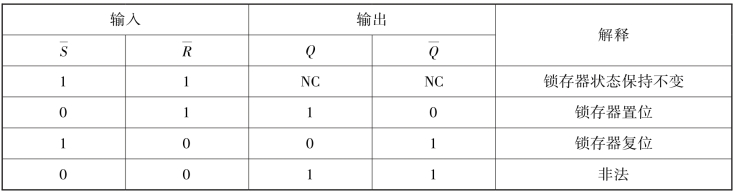

1.边沿D型触发器

边沿D型触发器(74HC74)如图8-22所示,其基本功能为:当置位端![]() 和复位端

和复位端![]() 都等于1时为触发模式,此时输出Q将在时钟脉冲输入端CP出现上升沿(↑)时翻转至与输入端D相同的状态。

都等于1时为触发模式,此时输出Q将在时钟脉冲输入端CP出现上升沿(↑)时翻转至与输入端D相同的状态。

图8-22 边沿D触发器

从图8-22中的集成芯片74HC74真值表可以看出,只有处在时钟脉冲上升沿时触发器才会翻转,且翻转之后的输出信号Q与输入端D一致。

2.边沿J-K触发器

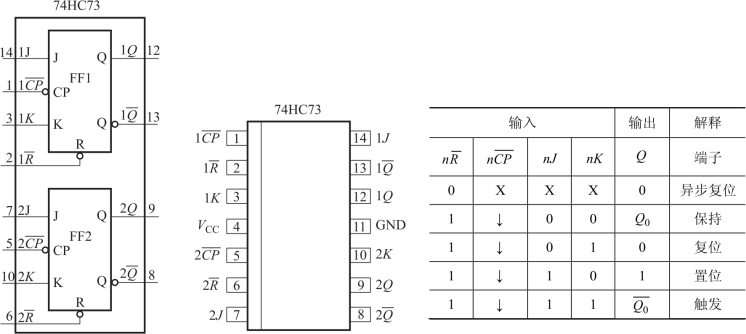

边沿J-K触发器是一类通用的触发器,如图8-23所示的74HC73为下降沿触发J-K触发器(内部有两个独特的边沿J-K触发器),当异步复位端![]() 时74HC73正常工作,此时如果输入端nJ=nK=0,则触发器输出端Q保持原来的状态;如果输入端nJ=nK=1,则触发器输出端Q与原来的状态相反。

时74HC73正常工作,此时如果输入端nJ=nK=0,则触发器输出端Q保持原来的状态;如果输入端nJ=nK=1,则触发器输出端Q与原来的状态相反。

图8-23 边沿J-K触发器

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。