梯形图程序中的不同逻辑处理指令所需要的存储容量和执行时间是不相同的,因此,在不影响程序执行结果的前提下,有时只需要调整指令的先后顺序,便可简化程序、缩短程序执行时间、优化程序。常用的PLC梯形图程序优化方法如下。

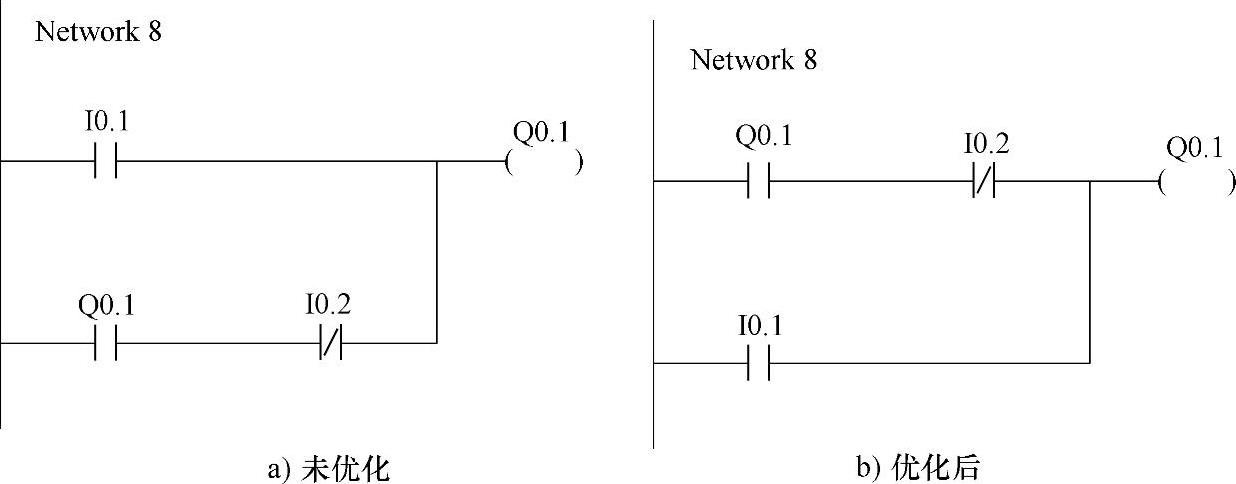

1.并联支路的优化

当输出由若干并联支路进行控制时,应根据“先与后或”的逻辑运算规则,将带有串联触点的并联支路放在只有独立触点的并联支路上方,这样,处理指令时就可以避免堆栈操作,减少指令所占的步数和执行时间。

例如,对于图2.3-10a所示的程序,PLC处理程序时,首先需要读入I0.1的状态,并将其压入堆栈中;接着读入Q0.1的状态、进行Q0.1& 的运算;然后再取出堆栈状态,进行I0.1和Q0.1&

的运算;然后再取出堆栈状态,进行I0.1和Q0.1& 的逻辑“或”运算,并将结果输出到Q0.1上。

的逻辑“或”运算,并将结果输出到Q0.1上。

当程序按照图2.3-10b所示优化后,PLC处理程序时,首先读入Q0.1的状态,接着直接进行Q0.1& 的运算;然后,直接以当前运算结果和I0.1进行逻辑“或”运算,并将结果输出到Q0.1上。显然,优化后的程序执行更简单,指令所占的步数和执行时间更短。

的运算;然后,直接以当前运算结果和I0.1进行逻辑“或”运算,并将结果输出到Q0.1上。显然,优化后的程序执行更简单,指令所占的步数和执行时间更短。

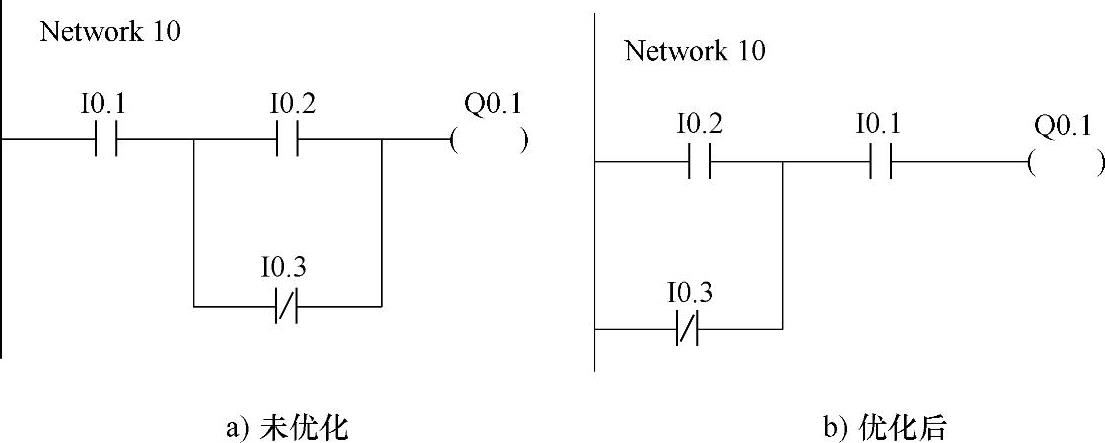

2.串联支路的优化

当输出由若干支路串联进行控制时,应根据PLC“从左向右”的处理规则,将有带有并联触点的支路放在最前面,它同样可以避免堆栈操作,减少指令所占的步数和执行时间。

例如,对于图2.3-11a所示的程序,PLC处理程序时,首先需要读入I0.1的状态,并将其压入堆栈中;接着读入I0.2的状态、进行I0.2和 的逻辑“或”运算;然后再取出堆栈状态,进行I0.1&(I0.2+I0.3)的逻辑“与”运算,并将结果输出到Q0.1上。

的逻辑“或”运算;然后再取出堆栈状态,进行I0.1&(I0.2+I0.3)的逻辑“与”运算,并将结果输出到Q0.1上。

当程序按照图2.3-11b所示优化后,PLC处理程序时,首先读入I0.2的状态、接着直接进行I0.2和 的逻辑“或”运算;然后,直接以现行运算结果和I0.1进行逻辑“与”运算,并将结果输出到Q0.1上。优化后的程序更简单,指令所占的步数和执行时间更短。

的逻辑“或”运算;然后,直接以现行运算结果和I0.1进行逻辑“与”运算,并将结果输出到Q0.1上。优化后的程序更简单,指令所占的步数和执行时间更短。

图2.3-10 并联支路的优化

图2.3-11 串联支路的优化(https://www.xing528.com)

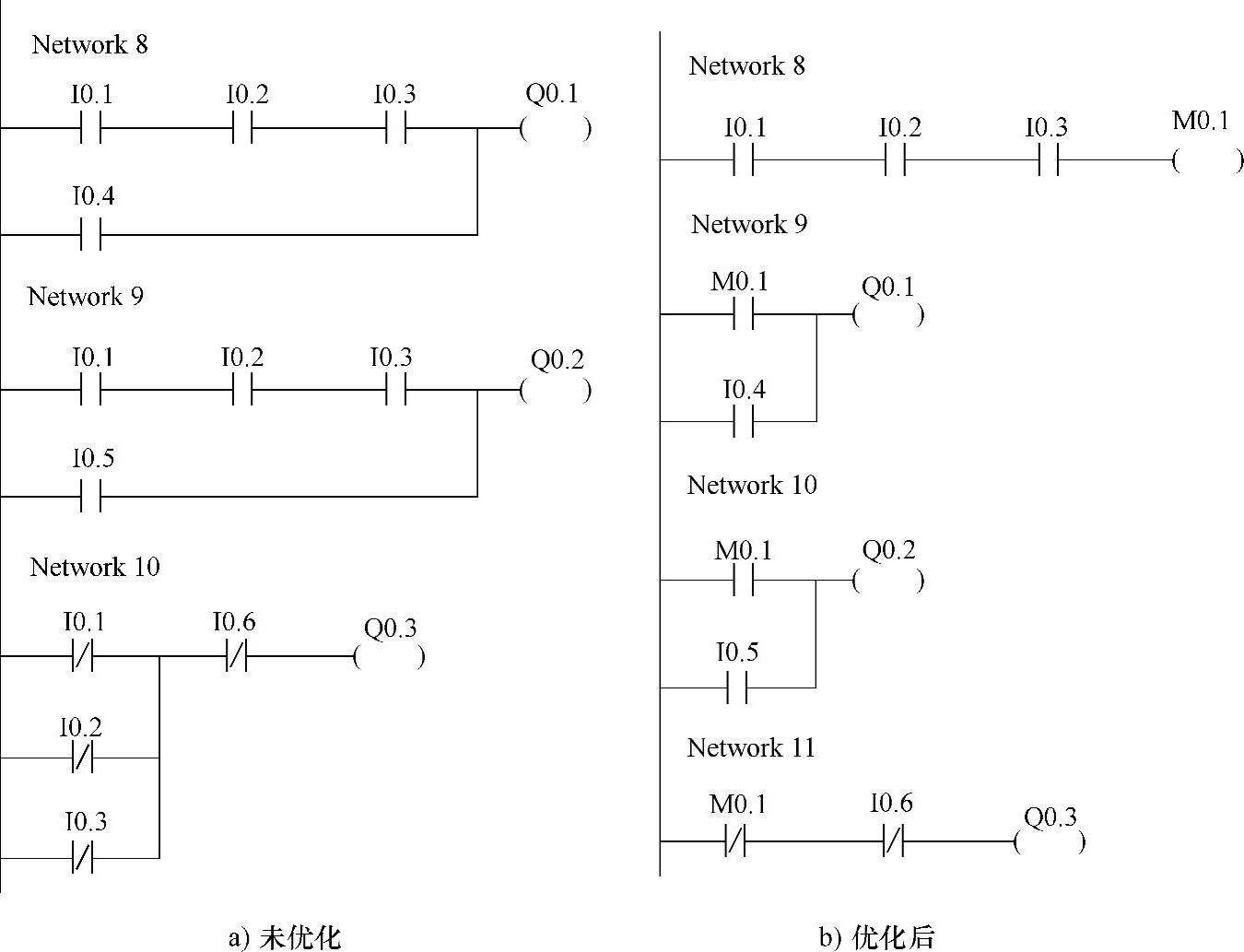

3.内部继电器的使用

在进行梯形图程序设计时,有时需要多次使用某些逻辑运算的结果,此时,应尽量使用内部继电器,这样不仅可简化程序,而且可以方便程序修改。例如,2.3-12a所示的程序可以按照2.3-12b进行优化。

在图2.3-12a所示的程序上,Q0.1、Q0.2具有共同的控制条件I0.1&I0.2&I0.3,Q0.3的控制条件为 ,程序长度15步。如果将控制条件I0.1&I0.2&I0.3作为内部继电器,则可得到图2.3-12b所示的程序,程序长度将减少至13步。

,程序长度15步。如果将控制条件I0.1&I0.2&I0.3作为内部继电器,则可得到图2.3-12b所示的程序,程序长度将减少至13步。

图2.3-12b所示程序的另一优点是修改方便。例如,当输入I0.1需要更改为M10时,对于图2.3-12a所示的程序,必须同时将Network8~Network10中的I0.1改为M10。而在图2.3-15b所示的程序上,则只需将Network8中的I0.1改为M10,程序修改简单且可避免遗漏。

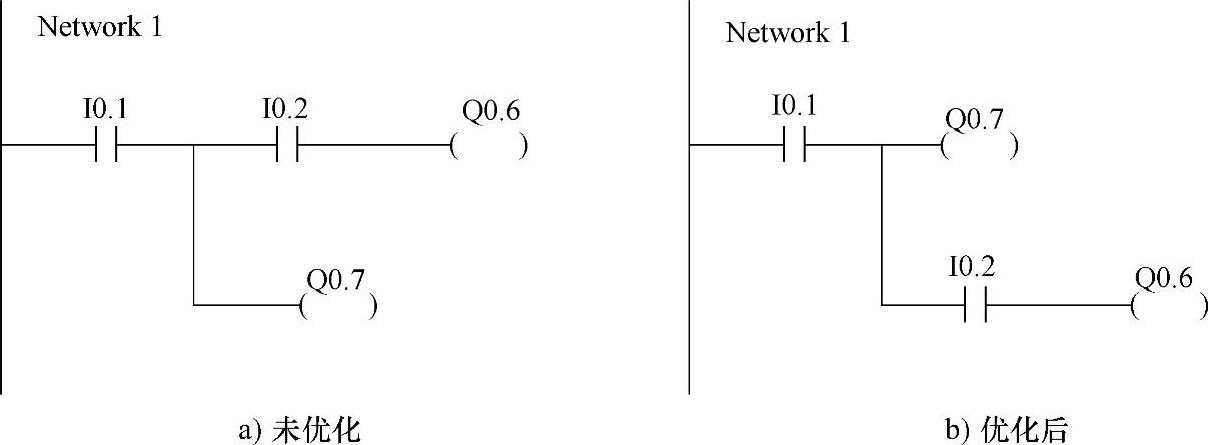

4.中间输出的优化

如果梯形图允许进行共用控制条件的多个输出线圈的编程时,同样也需要按照逻辑运算规则,保证逻辑处理动作依次进行,以避免堆栈操作,减少指令所占的步数和执行时间。

例如,对于2.3-13a所示的程序,按照梯形图“从上至下”的处理规则,首先需要读入I0.1的状态,并将其压入堆栈中;接着进行I0.1和I0.2的逻辑“与”运算,将结果输出到Q0.6上。然后再取出堆栈中的I0.1的状态,将其输出到Q0.7上。

图2.3-12 利用内部继电器的优化

图2.3-13 输出位置的优化

当程序优化为2.3-13b后,按照梯形图“从上至下”的处理规则,读入I0.1的状态后,就可将结果输出到Q0.6上。接着,以当前结果和I0.2进行逻辑“与”运算,然后输出到Q0.7上。其处理简单,指令步数和执行时间短。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。