经过前面的基本学习,我们已经初步掌握了版图编辑器L-Edit的基本设定与使用,下面就用L-Edit设计并绘制几个基本单元的版图。

1.工艺库数据的设定

进行版图设计前,要先了解并熟悉将来所要采用的工艺水平。从工艺厂家那里要到所需要的库文件,并把需要用到的设置信息输入到L-Edit编辑环境中去。

启动版图编辑器L-Edit,启动后首先进行基本的设置,先进行应用参数的设置,具体内容前面已经讲过,此处采用默认设置。然后进行设计参数的设置,主要设置工艺单位、鼠标参数等,此处也采用默认设置,默认设置时每个次栅格对应的物理尺寸为1μm,主栅格的尺寸为10μm。最后进行工艺参数的设定,首先要读取工艺厂家提供的数据包,把基本的图层设置信息、设计规则信息等在该软件中进行设置,这里不再详细介绍,此处采用L-Edit软件所自带的1.25μm工艺的工艺参数进行替换,具体的设置文件为软件安装目录下的“.\Samples\SPR\example1\lights.tdb”文件,替换设置的操作前面也已经讲过,此处不再详述。

替换后的图层信息和设计规则也可以通过设置窗口进行查看,此处列出基本设计中主要用到的一些图层和规则。

用到的图层主要有以下一些:五个特殊图层是Grid Layer(栅格图层)、Drag Box Layer(拖动矩形图层)、Origin Layer(原点图层)、Cell Outline Layer(单元外轮廓图层)和Error Layer(错误图层)。绘图图层是Poly(多晶硅)、Poly2(多晶硅2)、Active(有源区)、 Metal1(金属1)、Metal2(金属2)、N Well(N阱)、N Select(N选择区)、P Select(P选择区)、Poly Contact(多晶硅孔)、Poly2 Contact(多晶硅2孔)、Active Contact(有源区孔)和Via(通孔)等。

主要的设计规则如下所示。

1.1Well Minimum Width阱区的最小宽度10λ

1.2Well to Well(Different potential)Not checked不同类型阱的最小间距

1.3Well to Well(Same Potential)Spacing相同类型阱的最小间距6λ

2.1Active Minimum Width有源区的最小宽度3λ

2.2Active to Active Spacing有源区到有源区的间距3 Lambda

2.3aSource/DrainActiveto Well Edge源漏有源区到阱的边缘距离5 Lambda

2.3bSource/DrainActiveto Well Space源漏有源区到阱的间距5 Lambda

2.4aWellContact(Active)to Well Edge阱孔到阱的边缘3 Lambda

2.4bSubsContact(Active)to Well Spacing衬底孔到阱的间距3 Lambda

3.1 Poly Minimum Width多晶硅的最小宽度2 Lambda

3.2 Poly to Poly Spacing多晶硅的最小间距2 Lambda

3.3 Gate Extension out of Active栅延伸有源区 2 Lambda

3.4a/4.1a Source/Drain Width源漏区的最小宽度3 Lambda

3.4b /4.1b Source/Drain Width源漏区的最小宽度3 Lambda

3.5 Poly to Active Spacing多晶硅到有源区的间距1 Lambda

4.2a /2.5 Active to N-Select Edge有源区到N选择的边缘距离 2 Lambda

4.2b /2.5 Active to P-Select Edge有源区到P选择的边缘距离 2 Lambda

4.3a Select Edge to ActCnt选择区边缘到有源区孔1 Lambda

4.3b Select Edge to ActCnt选择区边缘到有源区孔1 Lambda

4.4a Select Minimum Width N选择区最小宽度2 Lambda

4.4b Select Minimum Width P选择区最小宽度2 Lambda

4.4c Select to Select Spacing N选择到N选择的间距2 Lambda

4.4d Select to Select Spacing P选择到P选择的间距2 Lambda

5.1A Poly Contact Exact Size 多晶硅孔的精确间距=2 Lambda

5.2A /5.6B FieldPoly Overlap of PolyCnt场区多晶硅包含多晶硅孔的间距1.5 Lambda

5.3A PolyContact to PolyContact Spacing多晶硅孔到多晶硅孔的间距2 Lambda

6.1A Active Contact Exact Size有源区孔的精确宽度=2 Lambda

6.2A FieldActive Overlap of ActCnt场有源区包含有源区孔的间距1.5 Lambda

6.3A ActCnt to ActCnt Spacing有源区孔到有源区孔间距2 Lambda

6.4A Active Contact to Gate Spacing有源区孔到栅的间距2 Lambda

7.1 Metal1 Minimum Width金属1的最小宽度3 Lambda

7.2 Metal1 to Metal1 Spacing金属1到金属1的间距3 Lambda

7.3 Metal1 Overlap of PolyContact金属1包含多晶硅孔的间距1 Lambda

7.4 Metal1 Overlap of ActiveContact金属1包含有源区孔的间距1 Lambda

8.1 Via Exact Size通孔的精确宽度=2 Lambda

8.2 Via to Via Spacing通孔到通孔的间距3 Lambda

8.3 Metal1 Overlap of Via金属1包含通孔的间距1 Lambda

8.4a Via to PolyContact spacing通孔到多晶孔间距2 Lambda

8.5b.Via to ActiveContact Spacing通孔到有源区孔间距2 Lambda

8.5a Via to Poly Spacing通孔到多晶硅间距2 Lambda

8.5b Via (On Poly) to Poly Edge多晶硅包含多晶通孔的间距2 Lambda

8.5c Via to Active Spacing通孔到有源区间距2 Lambda

8.5d Via (On Active)to Active Edge有源区包含有源通孔的间距2 Lambda

9.1 Metal2 Minimum Width金属2最小宽度3 Lambda(https://www.xing528.com)

9.2 Metal2 to Metal2 Spacing金属2到金属2的间距4 Lambda

9.3 Metal2 Overlap of Via1金属2包含通孔的间距1 Lambda

在绘制版图之前一定要详细了解这些规则的具体数据,只有这样才能在版图设计中设计出性能良好、面积最优的芯片版图。

2.版图编辑实例

设置好设计规则以后,就可以进行版图设计。我们的主要目的是学习软件的基本使用,因此下面的设计实例只考虑最少的绘图层,以前面讲过的图层为基础,本实例只考虑如下几个绘图层:N阱层、有源区层、N型选择层、P型选择层、多晶硅层和有源区接触孔层。

下面以实际的版图设计为例,来讲述如何用L-Edit软件设计版图,所有绘制的版图都是对应的草图,即版图中的所有尺寸没有经过严格精确的计算。

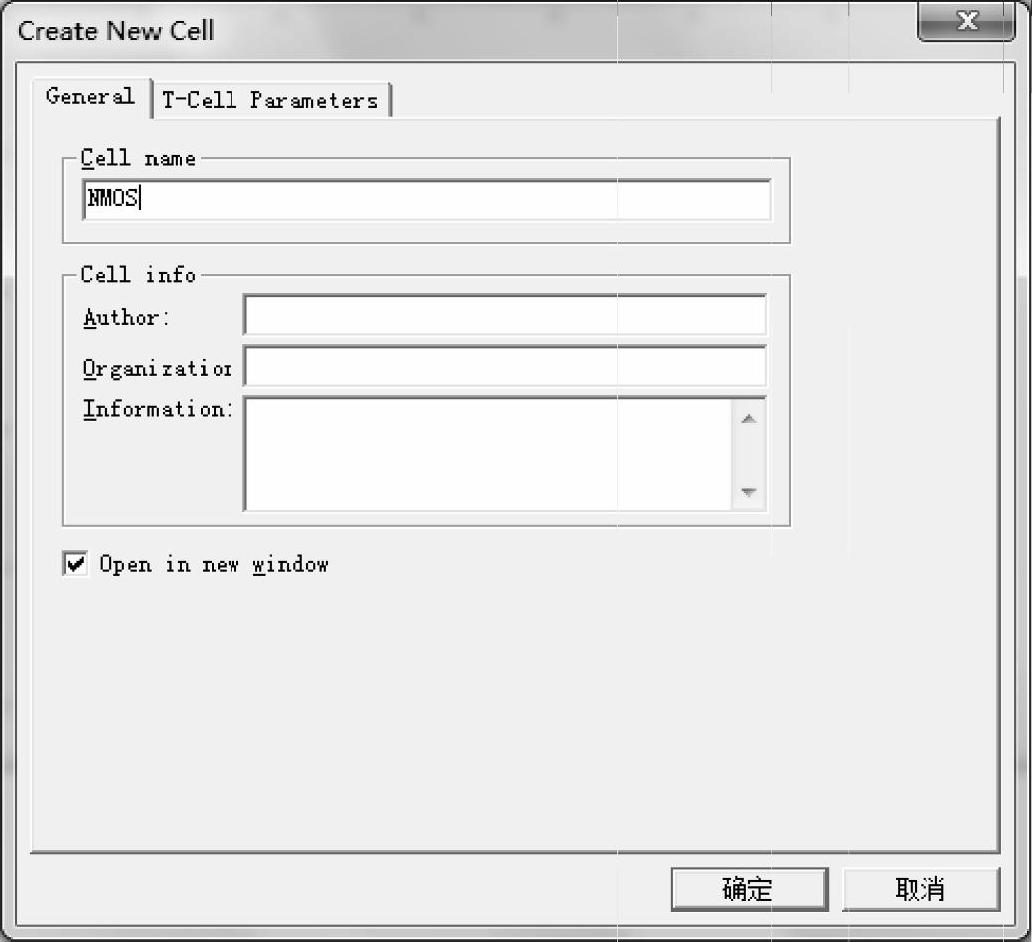

(1)NMOS晶体管版图设计 首先新建一个单元,命名为NMOS,单击确定按钮。新建NMOS单元示意图如图6-47所示。

图6-47 新建NMOS单元示意图

此时标题栏中会显示文件名和单元名。

在绘图区可以进行版图的绘制。

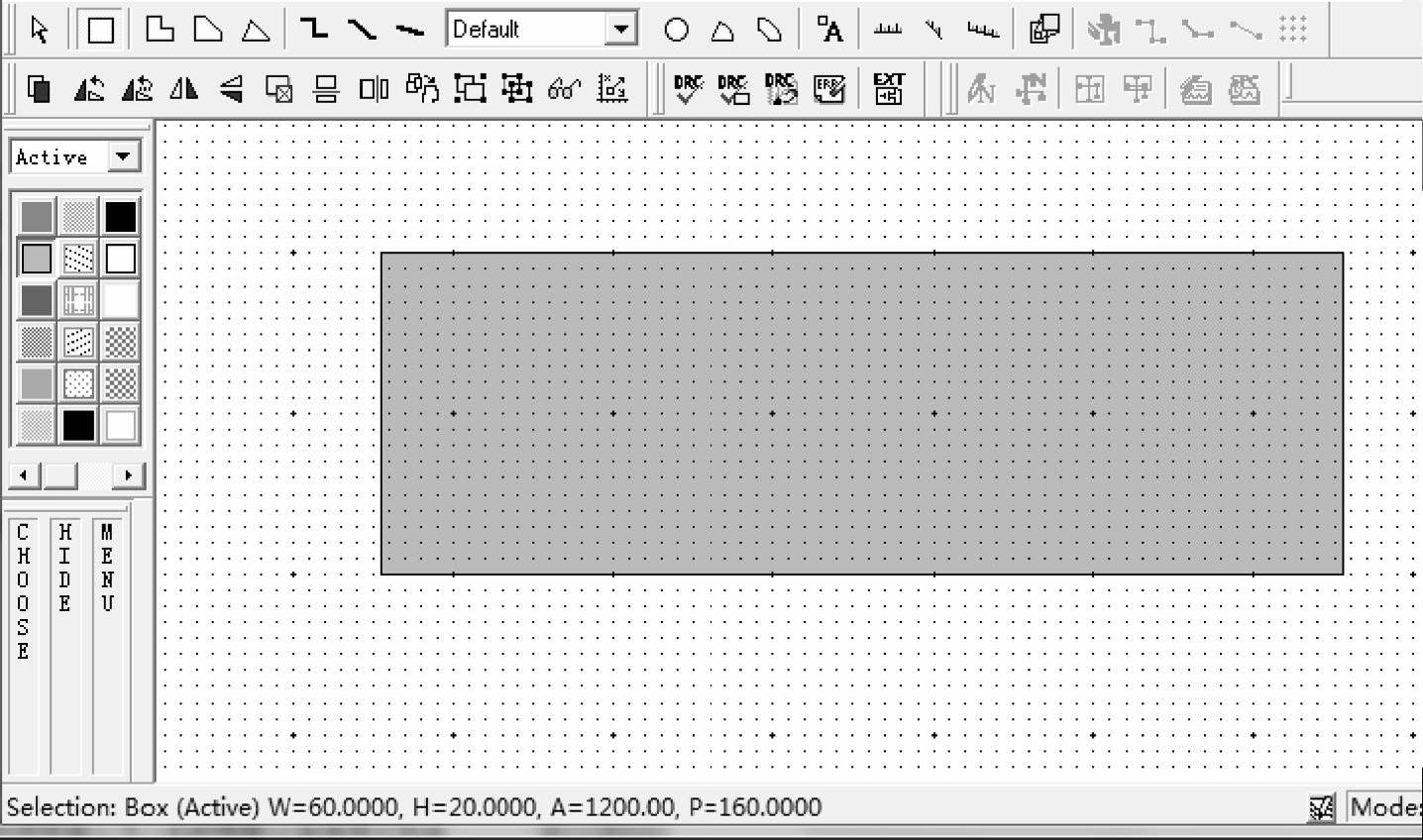

1)绘制有源区。考虑NMOS器件需要的Active图层的大小,在Active中要有一个有源区的接触孔,因此要考虑孔的大小和有源区包含孔的尺寸,即有源区的宽度最小为“孔的最小宽度规则值+2倍有源区包含孔的规则值”。宽度定好以后,考虑有源区的长度,在源区和漏区要各有一个孔区,则有源区的长度最少为“2倍有源区包含孔的规则值+2倍孔的最小宽度规则值+2倍孔与栅区的间距的规则值+沟道长度的规则值”。

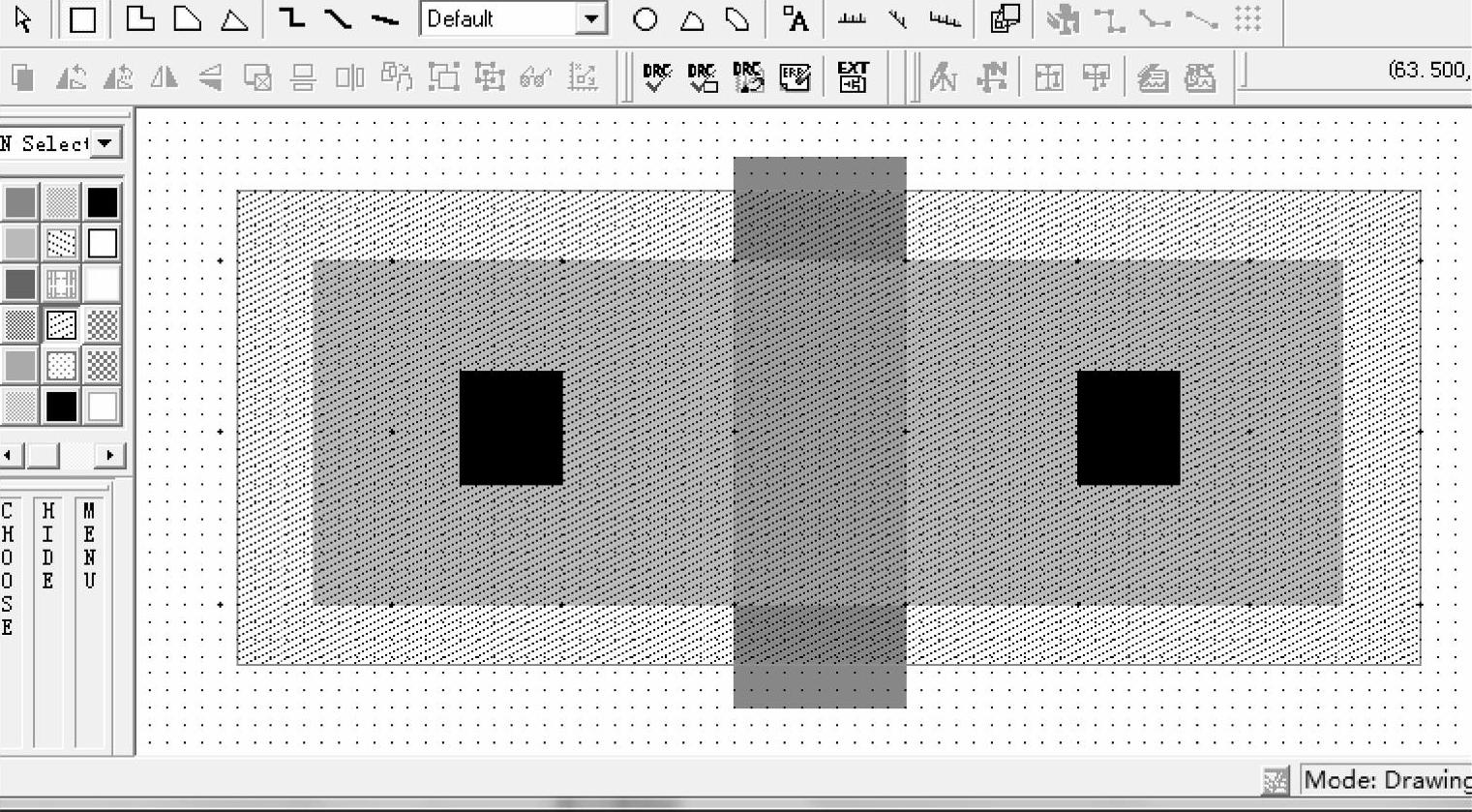

在图层板中选择有源区(Active)图层按钮,然后在绘图工具栏中选择矩形工具,按照计算好的尺寸绘制有源区的图形,如图6-48所示。

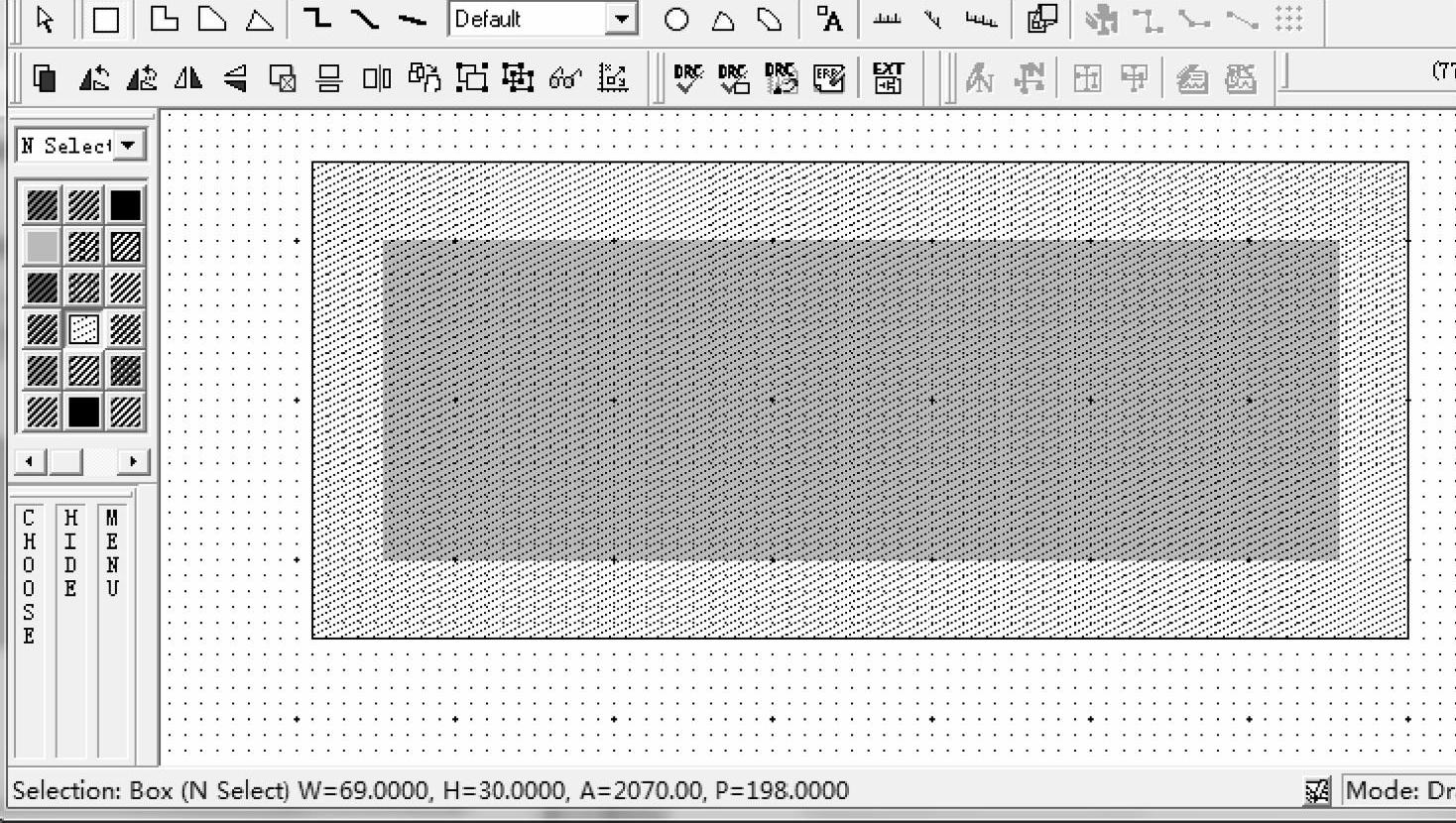

2)绘制N型选择层。绘制N型选择层时要考虑N型选择层的最小宽度,同时要考虑有源区的具体尺寸,即N型选择区的最小尺寸为“有源区的尺寸+2倍N型选择区包含有源区的最小包含规则值”。在图层板中选择N型选择层(NSelect)图层按钮,然后在绘图工具栏中选择矩形工具,按照计算好的尺寸绘制N型选择层的图形,如图6-49所示。

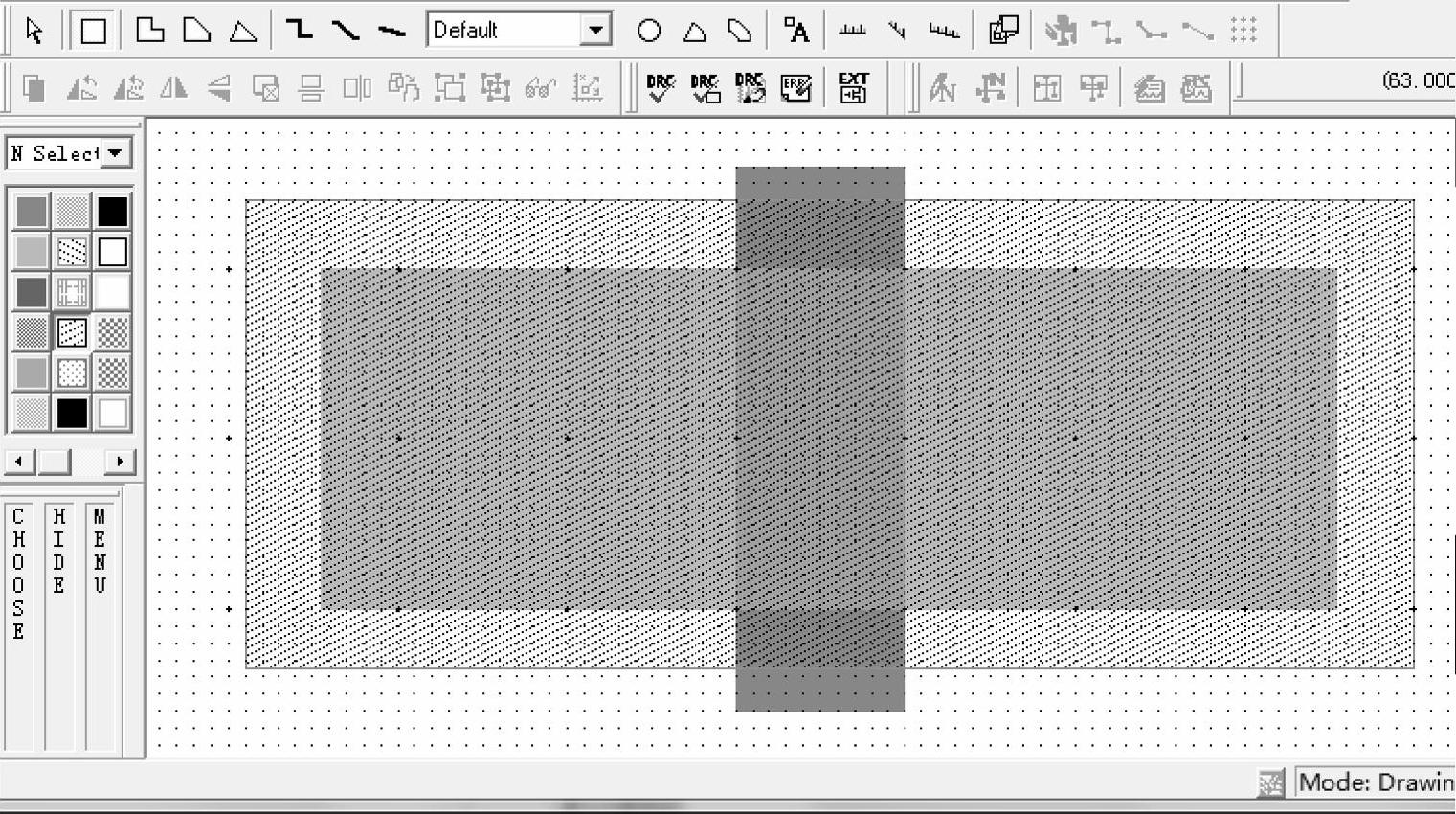

3)绘制栅区。绘制栅区时要考虑栅区的最小宽度、栅区延伸出有源区的最小长度。栅区延伸有源区时两边都要有延伸,因此所绘制栅区的最小宽度为“多晶硅的最小宽度”,最小长度为“有源区的宽度+2倍栅区延伸有源区的规则值”。

在图层板中选择栅区(Poly)图层按钮,然后在绘图工具栏中选择矩形工具,按照计算好的尺寸绘制栅区图形,如图6-50所示。

4)绘制有源区的接触孔。根据设计规则中接触孔的最小宽度值,在有源区两端规定的区域内绘制两个接触孔,同时要注意考虑有源区包含孔的有关规则值。接触孔的尺寸为“接触孔的最小宽度规则值”,同时要注意接触孔的位置,即接触孔与有源区的包含关系(有源区包含接触孔的规则),同时又要考虑接触孔与栅区之间的距离(接触孔与栅区的最小间距值)。

在图层板中选择有源区接触孔(Active Contact)图层按钮,然后在绘图工具栏中选择矩形工具,按照计算好的尺寸绘制图形,如图6-51所示。

图6-48 绘制的有源区图形

图6-49 绘制N型选择层的图形

图6-50 绘制栅区的图形

图6-51 绘制有源区接触孔的图形

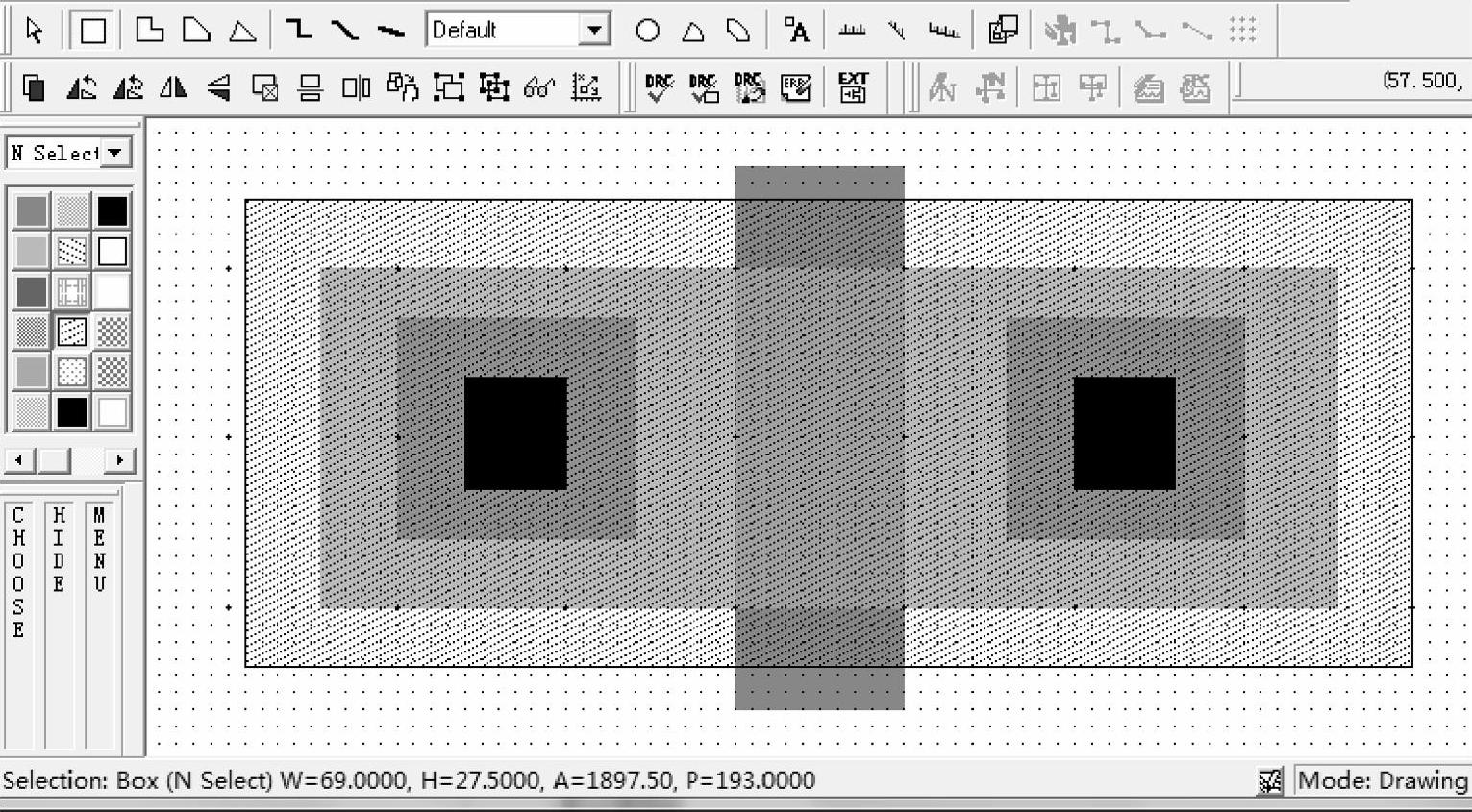

5)绘制金属图层。根据设计规则中有关金属连线的规则,首先考虑金属连线的最小宽度,其次要考虑金属线包含接触孔的规则值,即金属线的宽度值为“接触孔的最小宽度值+2倍金属线包含接触孔的值”,按照计算好的尺寸绘制两个金属连线的图形。

在图层板中选择金属(Metal1)图层按钮,然后在绘图工具栏中选择矩形工具,按照计算好的尺寸绘制图形,如图6-52所示。

至此,一个基本的NMOS晶体管就绘制完成,不过多晶硅栅区并没有接触孔。接下来可以进行版图设计规则检查,以保证设计的尺寸符合工艺要求。

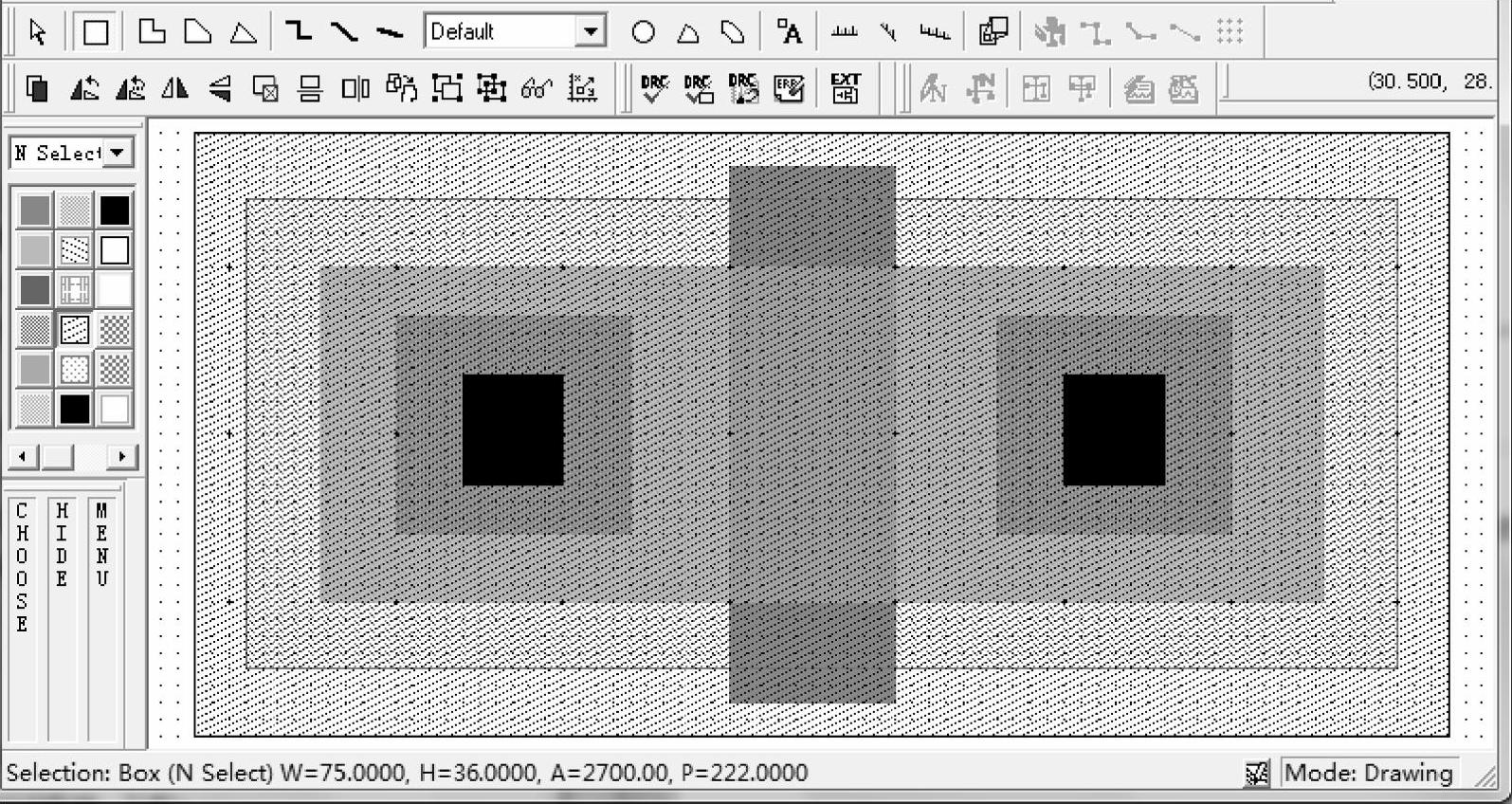

(2)PMOS晶体管版图设计 PMOS晶体管的绘制过程与NMOS晶体管的绘制过程基本相似,只是在绘制PMOS晶体管的时候,要绘制在N型阱区中,因此绘制的过程多了一步,同时选择层也要绘制成P型选择层。PMOS晶体管的具体绘制顺序为:N型阱层、有源区层、P型选择层、多晶硅层、有源区接触孔层和金属层。注意N型阱区的尺寸要考虑阱区的最小宽度规则值和阱区包含有源区的规则值,即阱区的尺寸为“有源区的尺寸+2倍阱区包含有源区的规则值”。具体的绘制过程不再详述,绘制好的基本PMOS晶体管版图如图6-53所示。

图6-52 绘制金属线的图形

图6-53 绘制好的基本PMOS晶体管版图

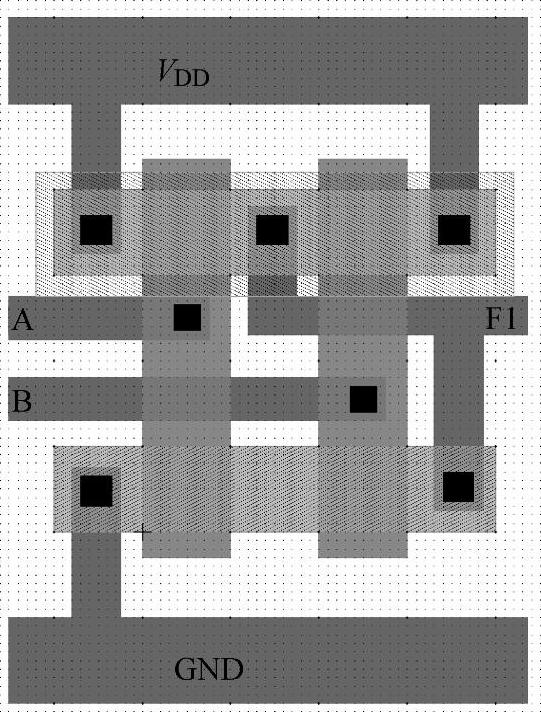

(3)反相器 基本的CMOS反相器有一个NMOS晶体管和一个PMOS晶体管,在设计CMOS反相器的时候,可以按照设计基本MOS晶体管的方式进行尺寸的分析计算并绘制图形,也可以采用例化的方式进行设计。采用例化的方式设计版图时,直接利用前面已经设计好的NMOS晶体管和PMOS晶体管,例化的具体操作步骤前面已经讲过,可以自己进行练习。

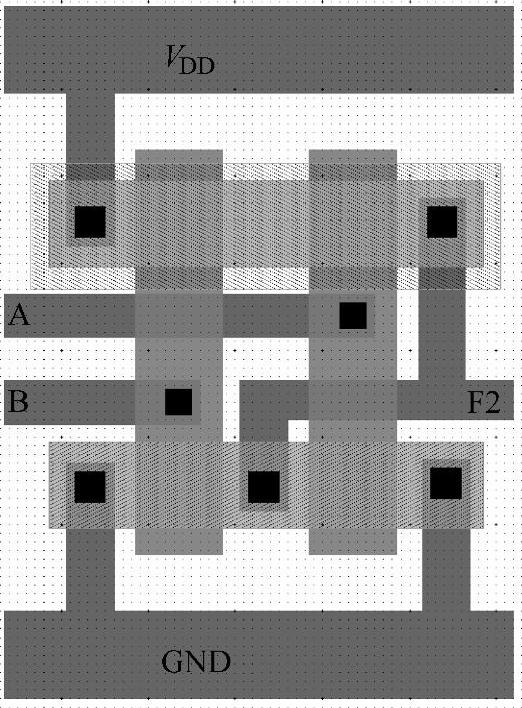

下面给出利用直接绘制的方式设计的CMOS反相器的版图。根据前面讲过的基本连接关系可以绘制CMOS反相器的版图,CMOS反相器的版图如图6-54所示(此版图没有考虑宽长比的影响)。

在实际的设计过程中,版图的布局布线对整体电路的性能有很大影响,因此读者也可以根据实际情况来设定反相器的版图布局。

(4)与非门 与非门是集成电路中重要的基本单元,其逻辑关系可以根据前面的逻辑设计过程来进行设计。对应的简单与非门版图如图6-55所示。

图6-54 CMOS反相器的版图

图6-55 与非门版图

(5)或非门 或非门是集成电路中重要的基本单元,其逻辑关系可以根据前面的逻辑设计过程来进行设计。对应的简单或非门版图如图6-56所示。

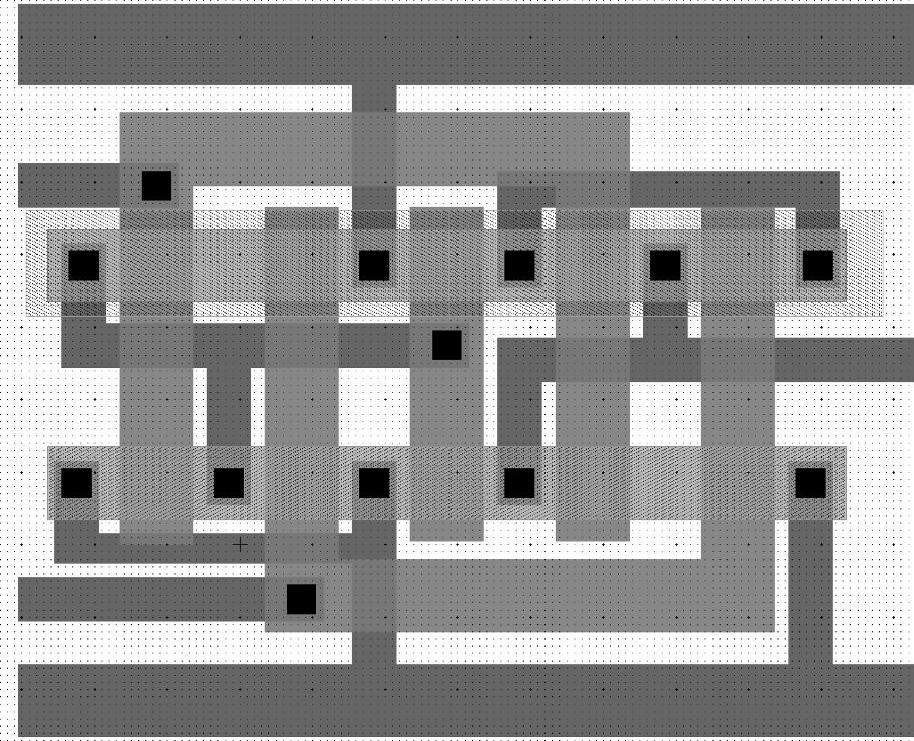

(6)异或门 异或门是集成电路中重要的基本单元,其逻辑关系可以根据前面的逻辑设计过程来进行设计。对应的简单异或门版图如图6-57所示。

图6-56 或非门版图

图6-57 异或门版图

前面给出的四个基本版图只是画出了版图的简单示意图,MOS晶体管的第四个电极体电极没有进行连接,而且版图中MOS晶体管的尺寸没有经过精确计算,或者说上面的版图只能理解为版图的草图。在实际设计的过程中,要根据实际的工艺水平和工艺图层来进行设计,特别是现在随着多层布线的越来越普及,版图变得越来越复杂。而且在真正设计的过程中,基本单元的版图要根据工艺厂家给出的版图库中的版图来进行设计,一般情况下设计者可以使用工艺厂家提供的版图库中的标准单元,而不能修改库中的标准单元的版图布局布线情况。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。