1.信号传输延迟

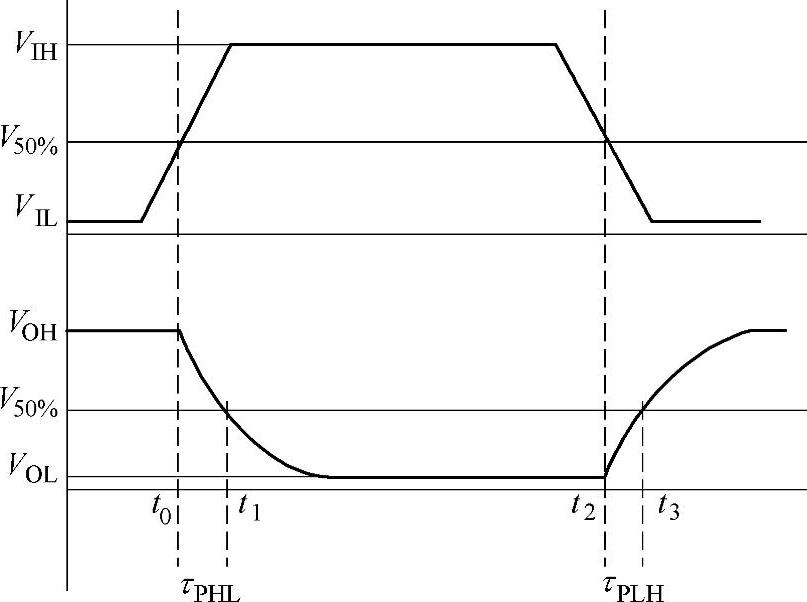

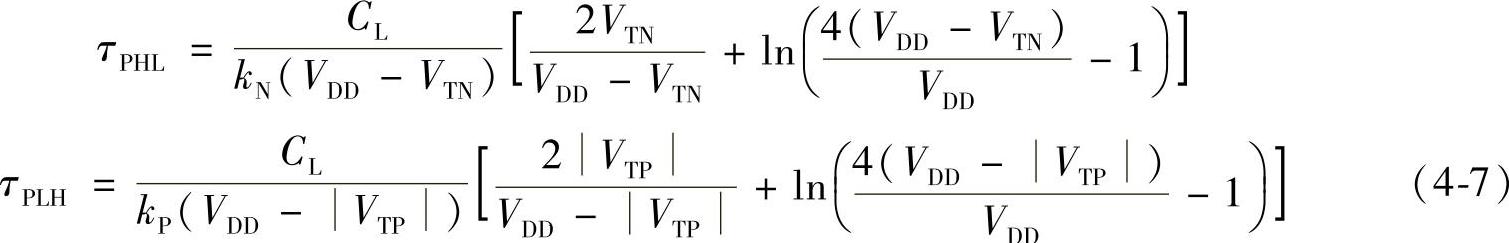

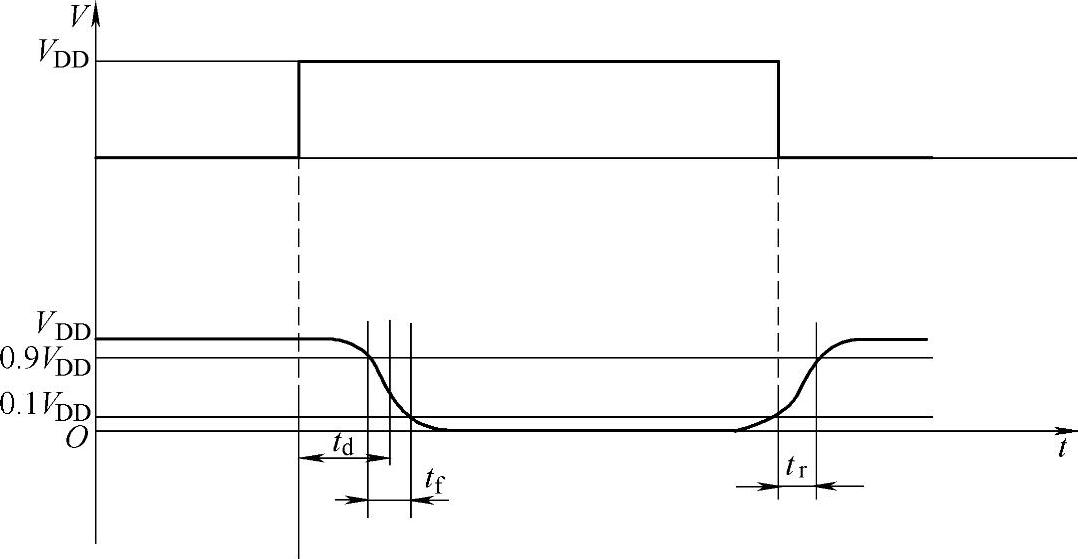

图4-4所示为一典型的反相器输入和输出波形对比示意图。

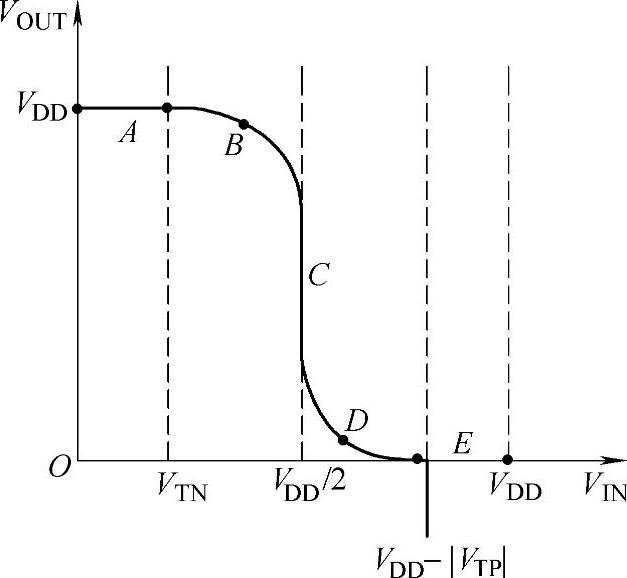

图4-3 CMOS反相器直流特性示意图

图4-4 反相器输入和输出波形对比

传输延迟时间τPHL和τPLH分别决定了输出由高变低和由低变高时的输入到输出的信号延时。

假设输入电压为理想的矩形波形,输入电压的上升和下降时间为0,则输出端50%处的电压为

V50%=VOL+(VOH-VOL)/2=(VOH+VOL)/2

式中,VOL为输出低电平;VOH为输出高电平。

则延迟为

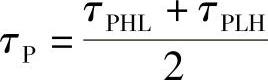

假设VOH=VIH=VH=VDD,VOL=VIL=VL=0,利用电容充电和放电时间的平均电流,根据电压输出翻转时器件的电容电流近似为常量,通过求解输出节点的状态方程可得:

式中,CL是等效负载电容。

根据这两个公式,设计时在考虑延时的情况下可以计算晶体管的宽长比,也就是所谓的有延时约束的设计。

2.噪声容限

噪声容限是与输入输出电压特性密切相关的参数,通常用两个参数——低噪声容限NML和高噪声容限NMH来确定噪声容限。

NML定义为驱动门的最大输出低电平VOL,max与被驱动门的最大输入低电平VIL,max之差的绝对值,即

NML=VIL,max-VOL,max (4-8)

式中,VIL,max为最大输入低电平;VOL,max为最大输出低电平。

NMH定义为驱动门的最小输出高电平VOH,min与被驱动门的最小输入高电平VIH,min之差的绝对值,即

NMH=VIH,min-VOH,min (4-9)

式中,VIH,min为最小输入高电平;VOH,min为最小输出低电平。

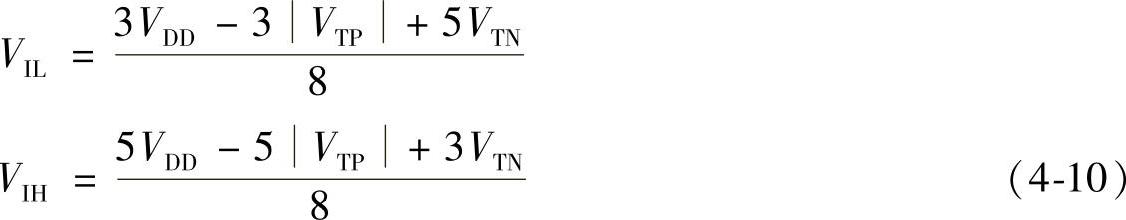

由图4-3可见,在五个工作区的B区和D区,存在着 的两个点,这两点对应的输入电压为VIL和VIH。如果令x=kN/kP,对B区和D区的电流方程求导,并令

的两个点,这两点对应的输入电压为VIL和VIH。如果令x=kN/kP,对B区和D区的电流方程求导,并令 ,就可以解出VIL和VIH。当X=1时,其值为

,就可以解出VIL和VIH。当X=1时,其值为

这样就可以根据MOS反相器的VOH、VOL、VIH、VIL计算出其噪声容限。

3.开关特性

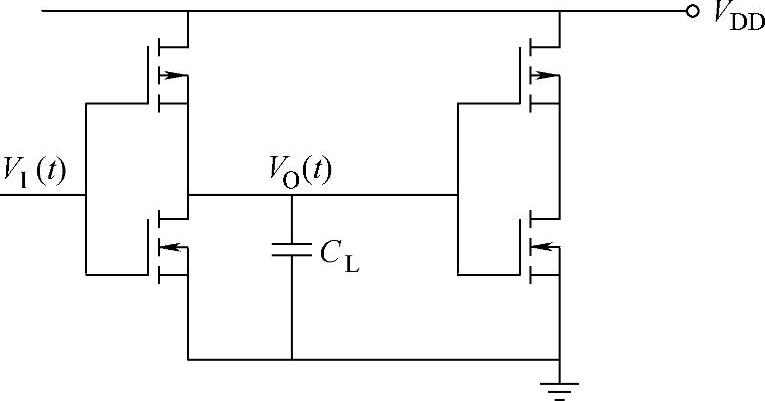

在CMOS电路中,负载电容CL的充电和放电时间限制了门的开关速度。

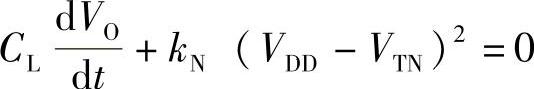

CMOS反相器负载电容示意图如图4-5所示,该反相器具有表示电容负载的负载电容CL(由下一级的输入电容、本级的输出电容和连线电容组成)。当输入是阶跃电压时,输出不是阶跃电压。CMOS反相器的开关特性如图4-6所示。

图4-5 CMOS反相器负载电容示意图

图4-6 CMOS反相器的开关特性

其中上升时间tr是波形从稳态值的10%上升到90%所需的时间,下降时间tf是波形从稳态值的90%下降到10%所需的时间,延迟时间td是输入电压变化到稳态值的50%的时刻和输出电压变化到稳态值的50%的时刻之间的时间差(延迟时间被认为是从输入到输出的逻辑转移时间)。

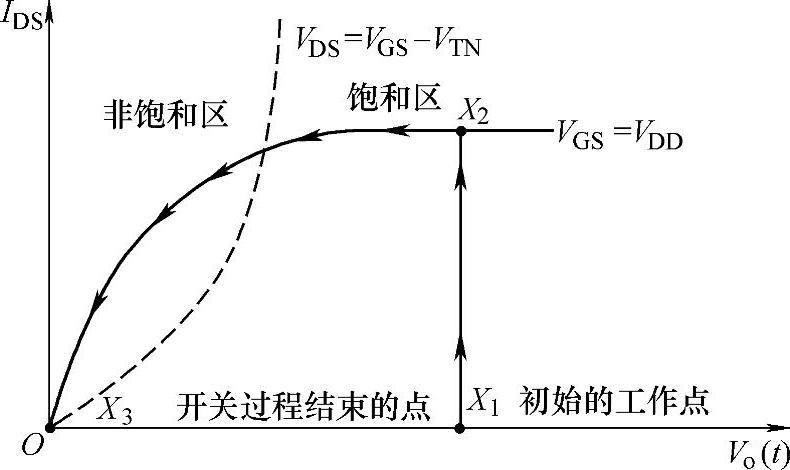

(1)下降时间 开关器件NMOS晶体管工作点的移动轨迹如图4-7所示,其中输入电压从VDD变化到0时的工作点的移动轨迹为图中箭头的示意方向。

最初,NMOS晶体管截止,负载电容充电到VDD,对应于轨迹曲线的X1点,当反相器输入端上加阶跃电压时,工作点变化到X2,此后轨迹沿VGS=VDD的特性曲线向原点X3运动。(https://www.xing528.com)

图4-7 开关器件NMOS晶体管工作点的移动轨迹

因此下降时间由两个时间间隔组成:

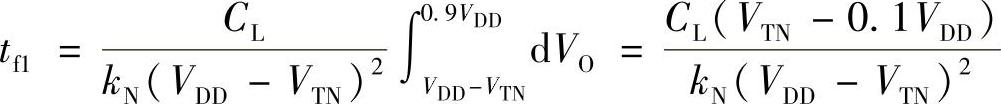

1)电容电压从0.9VDD下降到VDD-VTN所需的时间tf1。

根据公式 进

进

行积分可得到

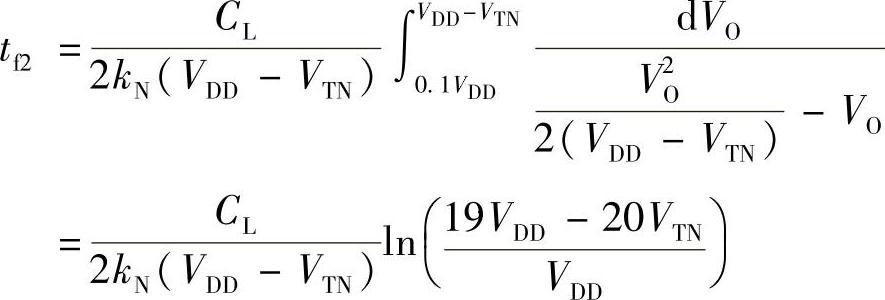

2)电容电压从VDD-VTN下降到0.1VDD所需的时间。经过积分计算可以得到

如果假设VTN=0.2VDD,则下降时间可以近似为

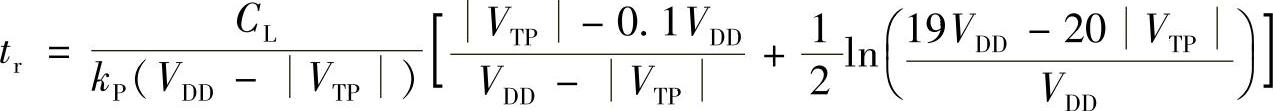

(2)上升时间 可以用类似的方法计算上升时间,可得到

如果取VTP=0.2VDD,则上式可以简化为

4.功耗

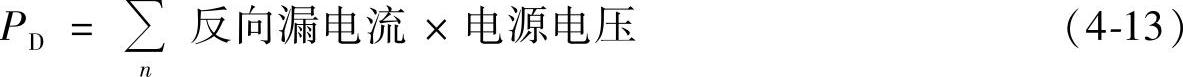

CMOS反相器的功耗P由静态功耗和动态功耗两部分构成。静态功耗PD即是MOS晶体管反向漏电流造成的功耗。而动态功耗PS又由开关的瞬态电流造成的瞬态功耗PA和负载电容的充电与放电造成的交变功耗PT两部分构成。

(1)静态功耗 考虑普通的反相器,在输入为0时,NMOS晶体管截止,PMOS晶体管导通,输出电压是高电平逻辑1;在输入为1时,NMOS晶体管导通,PMOS晶体管截止,输出电压是低电平逻辑0。因此无论CMOS反相器处于这两种逻辑中的哪一个状态,两个MOS晶体管中始终有一个导通,另外一个截止,没有在电源和地之间的通路,也没有电流流入栅极,因此静态功耗是0。

如果考虑扩散区和衬底之间的反向漏电流,则它将产生很小的静态功耗。此时CMOS反相器的静态功耗就是器件的反向漏电流和电源电压的乘积。在室温情况下,合理的估计值是允许每个门的反向漏电流为0.1~0.5nA,那么CMOS门电路总的静态功耗为

式中,n为器件的数目。对于反相器,若电源电压是5V,则由于反向漏电流所造成的静态功耗的典型值是1~2nW。

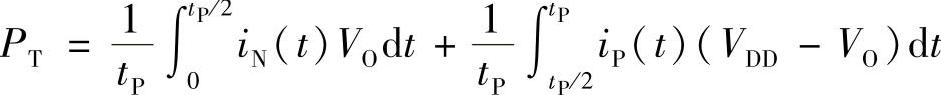

(2)动态功耗 在从0到1或者从1到0瞬变过程中的一个很短的时间间隔内,NMOS晶体管和PMOS晶体管都处于导通状态。这将导致一个从电源VDD到地的窄电流脉冲,由它引起的功耗叫交变功耗PA,其功耗大小取决于负载电容和门的设计。为了对输出端负载电容进行充电和放电,也要求有电流流动,由它引起的功耗叫瞬态功耗PT。

1)瞬态功耗。假设输入端VI是重复频率为fP=1/tP的脉冲信号,且阶跃输入的上升时间和下降时间比其重复周期小很多,在这个输入电压作用下,开关动作消耗的平均动态功耗PS近似为PT。

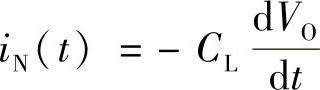

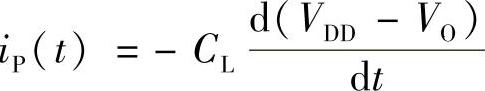

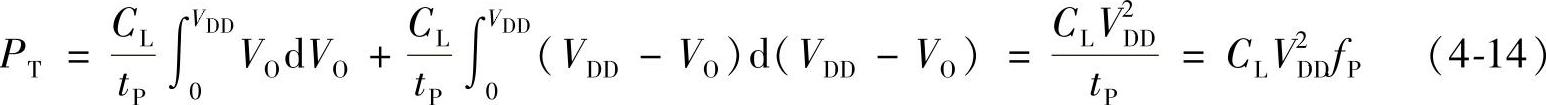

式中,tP是方波的周期;iN为NMOS晶体管的瞬时电流;iP为PMOS晶体管的瞬时电流。在阶跃输入下,并考虑到 ,

, ,可以得到

,可以得到

上式表明瞬态功耗与开关频率成正比,而与器件的参数无关。

2)交变功耗。当电路工作频率升高时,交变功耗PA增大,不容忽视(高速电路的交变功耗PA与瞬态功耗PT近似)。

一个周期tP内的平均交变功耗PA为

式中,i′为交变电流。

近似计算时可以假设交变电流i′的波形为三角形,此时PA可以近似为

式中,I′max为交变电流的峰值。

实际中为便于分析,可以针对交变功耗定义一个“非负载功耗等效电容CPD”,于是PA可以改写为

PA≈CPDfPV2DD (4-17)

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。