1.MOS晶体管特性

(1)I-V特性 当NMOS晶体管工作在截止区时没有沟道,从漏极到源极几乎没有电流。

当NMOS晶体管工作在线性工作区时,电子从源极向漏极漂移,漂移速度正比于这两个区之间的电场强度。电容每个极板上的电量为Q=CV,因此,沟道中的电荷Qchannel为

Qchannel=CG(VGC-VT) (3-12)

式中,CG为栅极到沟道的电容;VGC-VT是去掉PN结反偏所需的最小电压之后的电压,它能够吸引电荷到沟道中去。

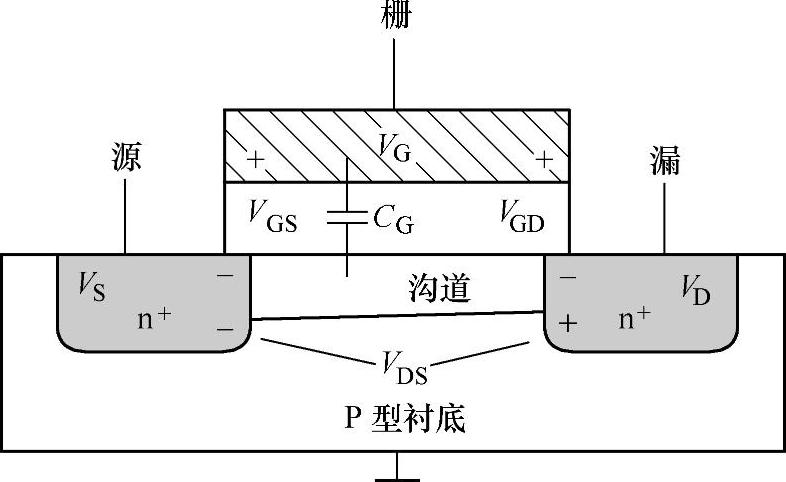

图3-14 栅极到沟道的电压示意图

栅极所加电压是针对参考沟道而言的,沟道并没有接地。如果源极电压为VS,漏极电压为VD,那么平均电压为VC=(VS+VD)/2=VS+VDS/2,因此栅极和沟道电压的平均值差VGC为VGS-VDS/2,栅极到沟道的电压示意图如图3-14所示。

如果栅极的长度为L,宽度为W,栅氧的厚度为tOX,则电容值为

式中,SiO2的介电常数εOX=3.9ε0,真空介电常数ε0为8.85×10-14F/cm。通常把ε0/tOX称为COX,即栅氧单位面积上的电容。

沟道中载流子的平均速度为

v=μnE (3-14)

电场强度E等于漏极和源极之间的电压差除以沟道长度,即

载流子穿越沟道的时间等于沟道长度除以载流子的速率,即L/v。

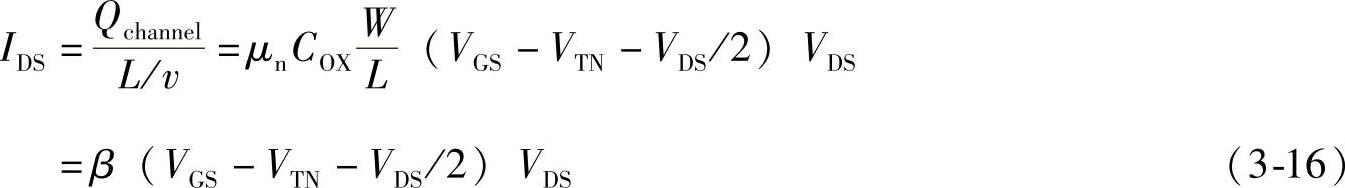

因此漏极和源极之间的电流等于沟道中的总电荷量除以穿越沟道的时间,即

式中,β=μnCOXW/L。

当MOS晶体管工作在饱和区,即VDS>VDsat时,靠近漏极附近的沟道消失,此时继续增大漏极电压对电流没有影响。把临界点的电压值带入公式就可以得到饱和电流的表达式:

综上所述,截止区、线性区和饱和区内的I-V特性关系为

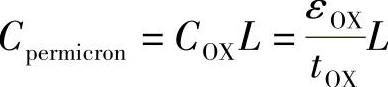

(2)C-V特性 C-V特性是MOS晶体管的栅极电容与栅端电压之间的关系,同时也受到MOS晶体管源极和漏极所加电压的影响。

1)简单的MOS晶体管模型。NMOS晶体管的每个端和其他端之间都存在电容,一般来说这些电容都是非线性的,并且与电压相关。当它们工作在逻辑门的导通与截止电压附近时,我们可以将其近似处理为简单的电容。

MOS晶体管的栅极是一个很好的电容,可以把栅电容看成是一个平板电容,其顶部是栅极,底部是沟道,中间是较薄的氧化层介质,因此其电容为

CG=COXWL (3-19)

电容是一种双端元件,在晶体管导通的时候,如果晶体管未饱和则沟道从源极一直延伸到漏极,如果饱和导通则沟道从源极延伸到夹断位置。因此将栅电容简化近似处理为栅极和源极之间的电容是比较合理的,因此称栅电容为CGS。

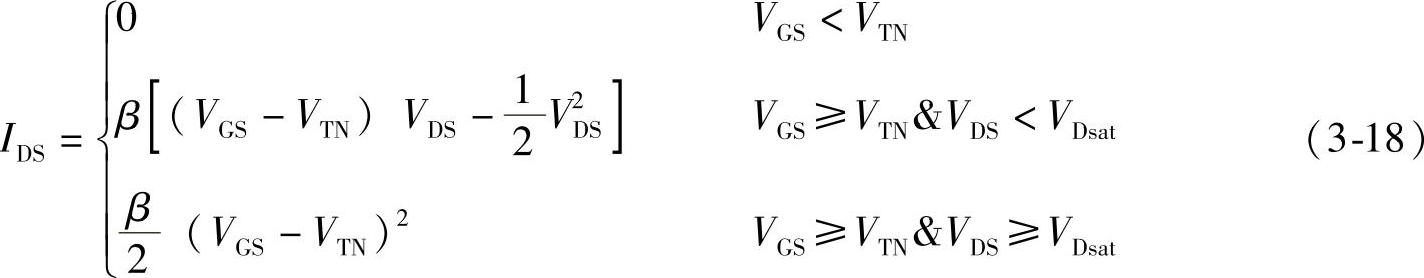

逻辑电路中所用的大部分晶体管都达到了最小的可制造长度,因为这样可以得到最快的速度和最低的功耗。因此在某种特定工艺下将这个最小长度看成常数L,可以定义:

CG=CpermicronW (3-20)

式中, 。

。

注意:如果有更先进的工艺,其中沟道长度和栅氧厚度都缩小了同样的比例,则Cpermicron保持不变(其值等于栅极宽度乘以1.5~2fF/μm)。

2)复杂的MOS晶体管模型 在实际中,MOS晶体管是工作在三种工作状态下,即截止、线性导通和饱和导通状态。

① 截止(Cutoff)。当MOS晶体管截止时,没有沟道形成,栅极上的电荷与硅体中极性相反的电荷是匹配的,将电容称为CGB,即栅极到硅体的电容。当栅极电压增大但仍低于阈值电压时,表面形成耗尽层,这样就相当于将电容的下极板向远离栅氧的方向做有效移动,增加了绝缘介质厚度,降低了电容的大小。

② 线性(Linear)。当VGS>VT时,形成沟道,但沟道是与漏极和源极连接的,而不是与硅体连接的。当VDS较低时,沟道电荷基本上是源极和漏极共享的,因此电容为CGS=CGD=C0/2(此处C0为理想情况下平板电容值);当VDS增大时,漏极附近的区域反型程度减少,从而使更大一部分电容归于源极,较少一部分归于漏极。

③ 饱和(Saturation)。当VDS>VGS-VTN时,MOS晶体管饱和,同时沟道夹断。此时所有本征电容都归于源极,由于发生夹断,饱和状态下的电容近似为 。

。

(3)寄生电容 除了栅极电容之外,漏极和源极也有电容,这些电容并不是器件的基本工作条件,但也影响器件的性能,因此称为寄生电容(Parasitic Capacitor)。这些电容来自于源极或漏极扩散区和硅体之间的反偏PN结,因此也称为扩散电容CSB和CDB。由于扩散区具有较高的电阻和较大的电容,因此人们在版图上一般将其做得尽可能小。(https://www.xing528.com)

在实际的器件中,栅极与源极和漏极有少量的重叠,同时还有一部分终止在源极和漏极的边缘电场,这样就形成了一些重叠电容,这些电容的大小与晶体管的宽度成正比,单位宽度重叠电容的典型值为CGSOL=CGDOL=0.2~0.4fF/μm。

则重叠电容值为

CGS(重叠)=CGSOLW

CGD(重叠)=CGDOLW (3-21)

2.MOS晶体管的基本参数

在设计MOS晶体管的过程中,要经常分析计算的参数包括宽长比、阈值电压等。

(1)宽长比 宽长比是比较重要的参数,它决定了晶体管的版图尺寸,其基本含义就是MOS晶体管沟道的宽度W和长度L的比值为W/L。

(2)阈值电压 阈值电压VT是金属栅电极下面的半导体表面呈现反型从而出现导电沟道时所需要加的电压。由于刚强反型时导电电子少,漏电流比较小,实际中常规定漏电流达到某一值时的栅电源电压值为VT。

强反型是指表面积累的少数载流子(少子)浓度等于甚至超过体内多数载流子浓度的状态,即表面电子浓度ns=体内空穴浓度pP。理想MOS晶体管的阈值电压为

式中,q为电荷常数;NA为P型衬底的掺杂浓度;ε为相对介电常数;ε0为介电常数;Ei为半导体导带能级;EF为费米能级;VS为表面势;Xdmax为耗尽区宽度。

对于实际的MOS晶体管,由于金属和半导体的功函数差不为0,栅氧中也存在一定的电荷,因此对应的阈值电压为

式中,Vms为金属和半导体的功函数差;QOX为栅氧的电荷浓度;QBmax为衬底的电荷浓度。

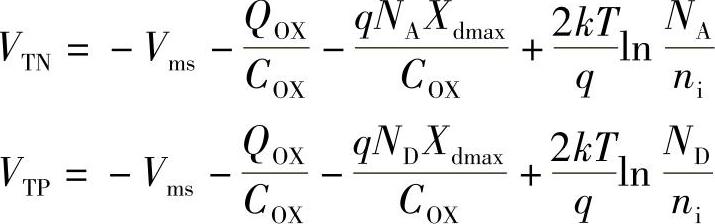

对应的NMOS晶体管和PMOS晶体管的阈值电压为

式中,Vms为金属和半导体的功函数差;Xdmax为耗尽区宽度;T为温度;ni为本征半导体的载流子浓度;NA为P型衬底的掺杂浓度;ND为N型衬底的掺杂浓度;k为波尔兹曼常数。

由此看出,影响MOS晶体管阈值电压的因素主要有:①绝缘介质SiO2中的电荷(QOX)。②衬底的掺杂浓度(NA)。③栅氧化层的厚度(COX)。④栅材料与硅的功函数差(Vms)。

在集成电路工艺中,通常需要对阈值电压进行调整,使之满足电路设计的要求,此工序称为“调沟”,即向沟道区进行离子注入(Ion Implantation),以改变沟道区表面附近载流子浓度。

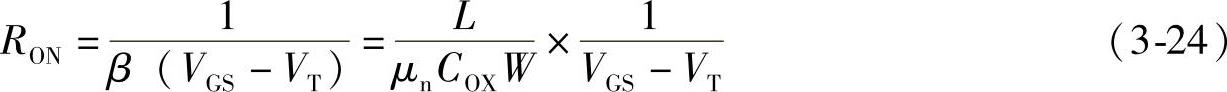

(3)导通电阻RON 当VDS较小,工作在线性区时,MOS晶体管相当于一个电阻,定义当VDS很小时VDS与IDS的比值为导通电阻。

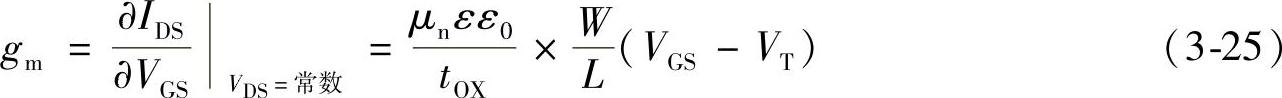

(4)跨导 跨导是MOS晶体管的一个极为重要的参数,表示交流小信号时衡量MOS晶体管VGS对IDS的控制能力的参数(VDS恒定)。

式中,gm为MOS晶体管跨导;IDS为MOS晶体管的漏源电流。

(5)最高工作频率 当栅极输入电容CGC的充放电电流等于漏极和源极交流电流的数值时,所对应的工作频率为MOS晶体管的最高工作频率。

因为当栅极和源极之间输入交流信号时,由源极增加(减少)流入的载流子中的一部分通过沟道对电容进行充(放)电,另一部分通过沟道流向漏极而形成漏源之间电流的变化量。因此当变化的电流全部用于对沟道电容进行充放电时,MOS晶体管也失去了工作能力。

一般情况下,最高工作频率为

式中,μ是沟道载流子迁移率;VT是MOS晶体管的阈值电压。

计算NMOS晶体管或PMOS晶体管的最高工作频率时,只要将相应的载流子迁移率数值和阈值电压数值带入计算即可。从最高工作频率的表达式,我们得到一个重要的信息:最高工作频率与MOS器件的沟道长度L的平方成反比,减小沟道长度L可有效地提高工作频率。

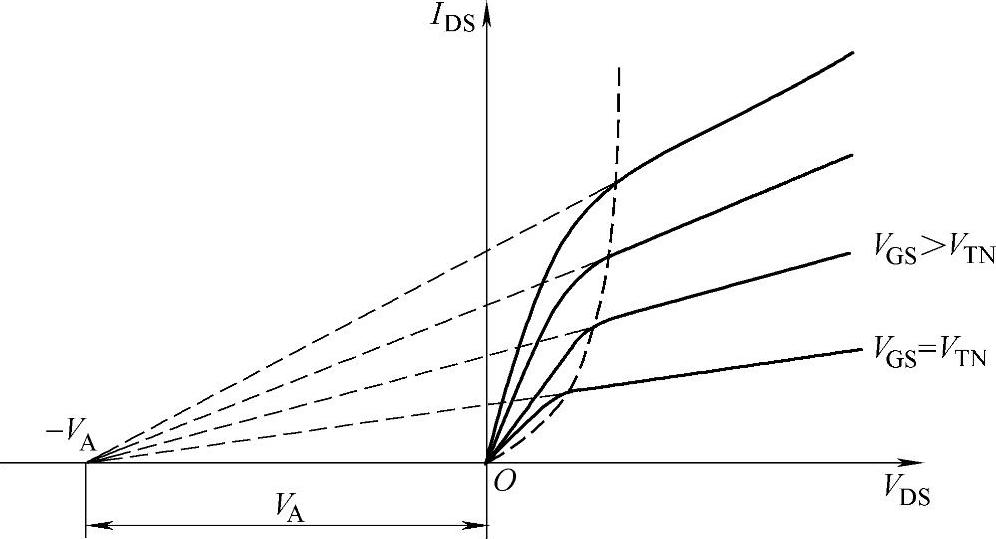

图3-15 沟道长度调制效应的影响

(6)厄莱(Early)电压 当MOS晶体管工作在饱和区时,其沟道长度变小,减小了ΔL,即存在一个沟道长度误差ΔL。由于ΔL的存在,实际的沟道长度L将变短,对于L比较大的器件,ΔL/L比较小,对器件的性能影响不大,但是,对于短沟道器件,这个比值将变大,对器件的特性产生影响。器件的电流-电压特性在饱和区将不再是水平直线的形状,而是向上倾斜,也就是说,工作在饱和区的NMOS晶体管的电流将随着VDS的增加而增加。这种在VDS作用下沟道长度的变化引起饱和区输出电流变化的效应,被称为沟道长度调制效应。衡量沟道长度调制的大小可以用厄莱电压VA表示,它反映了饱和区输出电流曲线上翘的程度。受到沟道长度调制效应影响的NMOS晶体管伏-安特性曲线将发生变化,沟道长度调制效应的影响如图3-15所示。

(7)衬底偏置电压 一般情况下我们都假设衬底和源极相连,但有时候衬底和源极不是相连的,而是衬底单独接一个电位,此时衬底与源极之间的电压差VBS不等于0。

如果衬底接一个正电位,对NMOS晶体管而言,衬底和源区形成的PN结处于反偏状态,对应的耗尽层变宽,耗尽层的增加必然导致可动载流子的减少,从而导致电流下降,为了保持原来的导电水平,必须增加栅极上的电压,因此衬底偏置电压的存在导致管子的阈值电压升高。

阈值电压的变化近似为 ,γ为衬底偏置效应系数,它随衬底掺杂浓度变化而变化,典型值:NMOS晶体管,γ=0.7~3.0;PMOS晶体管,γ=0.5~0.7。对于PMOS晶体管,ΔVT取负值;对于NMOS晶体管,ΔVT取正值。

,γ为衬底偏置效应系数,它随衬底掺杂浓度变化而变化,典型值:NMOS晶体管,γ=0.7~3.0;PMOS晶体管,γ=0.5~0.7。对于PMOS晶体管,ΔVT取负值;对于NMOS晶体管,ΔVT取正值。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。