元器件在集成电路中扮演着重要的角色,根据集成电路的不同,对应的元器件也有所不同,比较常见的元器件主要包括无源元件和有源器件,无源元件一般主要包括电阻、电容和电感,有源器件主要包括二极管、双极型晶体管和MOS晶体管等。

不管在哪一种集成电路中,一般情况下都同时包括无源元件和有源器件。

1.无源元件

无源元件一般主要包括互连线、电阻、电容和电感等。

(1)互连线 互连线是各种集成电路的基本元件,互连线的版图设计是集成电路设计中的基本任务。在混合集成电路和单片集成电路的衬底上,互连线大部分是由金属薄层形成的条带。不同衬底上的电路互连线可能用到金属裸线或电缆。对于各种互连线设计,应该注意到以下几个问题:

1)为了减少信号或电源引起的损耗,以及为了减小芯片面积,大多数互连线应该尽量短。实际上,版图设计中只要对那些传输高频信号的互连线按照最小长度布线就可以。

2)为了提高集成度,在传输电流非常微弱时,大多数互连线应以制造工艺所能提供的最小宽度来布线。

3)在互连线传输大电流时,应估计电流容量并保留足够的余量。

4)制造工艺提供的多层金属能有效提高集成度。

5)在微波和毫米波范围内,应注意互连线的趋肤效应和寄生参数。

6)在某些情况下,可以有目的地利用互连线的寄生效应。

集成电路工艺发展到深亚微米阶段后,互连线的延迟已经超过内部逻辑门的延迟,成为时序分析的重要组成部分。这时应采用链状RC网络、RLC网络或进一步采用传输线来模拟互连线。同时为了保证元器件模型的精确度和信号的完整性,需要对互连线的版图结构加以约束并进行规整布线。

(2)电阻 在集成电路中,制造电阻的方式有很多种,比较常见的有以下几种:

1)体管结构中不同导体材料层的片式电阻,这种电阻的阻值可以根据导体层材料的方块电阻值来进行确定。一般可以作为电阻的区域主要有掩埋层、基区层和有源区层等,具体在设计的过程中要根据电阻的阻值来进行确定,不同的层对应的方块电阻之间差别很大。在双极型硅工艺中,掩埋集电极的n+层具有每方块2~10Ω的电阻率,基极p-层有每方块几千欧姆的电阻率。在CMOS工艺中,可以用阱区形成片式电阻,这类片式电阻能实现从10Ω到十几千欧姆范围的电阻值。这种由晶体管材料层构成的电阻随工艺和温度的变化较大。

2)专门加工的高质量、高精度电阻,这类电阻一般要求电阻值非常精确。在CMOS工艺中,通常采用多晶硅层形成薄膜电阻。

3)用互连线(金属线)实现的电阻是阻值相对较低的电阻,在高频电路中,必须要考虑电阻的寄生参数。任何电阻只能承受有限的功耗,在给定的工艺中,工艺数据会给出每种电阻单位面积允许的最大功耗,根据这些数据可以决定每个电阻的最小宽度。

4)有源电阻,所谓有源电阻是指采用晶体管进行适当的连接并使其工作在一定的状态时所对应的电阻,利用其直流导通电阻和交流电阻作为电路中的电阻元件使用。双极型晶体管和MOS晶体管都可以作为有源电阻使用。以NMOS晶体管为例,连接NMOS晶体管的栅极和漏极,只要NMOS晶体管的VGS大于其阈值电压,将使导通的NMOS晶体管始终工作在饱和区,此时的NMOS晶体管就可以等效为一个电阻。

在集成电路中,比较常用的电阻是体管结构中不同导体材料层的片式电阻,其电阻的阻值主要由方块电阻R□来决定。对于一个长度为L,宽度为W的半导体材料,其电阻值为

R=(ρ/d)L/W=R□L/W (3-1)

式中,ρ为电阻率;d为厚度。

当半导体层材料层的长度和宽度相等时,即W=L,其阻值大小就是一个方块电阻的值,方块电阻与此正方形的边长大小无关,即与W和L的值无关,只与半导体材料的工艺参数有关。对于集成电路来说,方块电阻是电阻的基本组成单元,其量纲为Ω/□。我们在应用方块电阻进行计算时不用考虑半导体材料的厚度,因为厚度是由工艺厂家的工艺参数所决定,我们只需要考虑此半导体材料层电阻的平面尺寸,即长度L和宽度W。

一般情况下,半导体材料层电阻的阻值可以根据方块电阻和面积对应的方块数进行计算,例如,考虑一个由4个方块组成的电阻R1,如果方块电阻值为R□=5kΩ/□,那么该电阻R1对应的电阻值为

电阻值R1=方块电阻值×方块数,即R1=R□×n=5kΩ/□×4□=20kΩ。

但在实际的版图中,这样的计算不是很精确,因为在实际的版图中,常常会有弯折的电阻版图和连接金属线的电阻版图,这样的电阻在计算其阻值的过程中要充分考虑拐角处的电阻和两端的电阻,一般情况下要进行电阻值的修正。对于不同的工艺,其修正因子一般不同,但工艺厂家一般都会把电阻的修正计算公式提供给设计者。

另外,半导体材料的电阻值还会随着温度的变换而变化,一般情况下为温度的多项式函数,同样,对于不同的制作工艺线,其电阻值受温度的影响也不尽相同,即温度影响系数不尽相同。

在真正设计半导体材料电阻的过程中,一定要仔细阅读工艺厂家提供的相关资料。

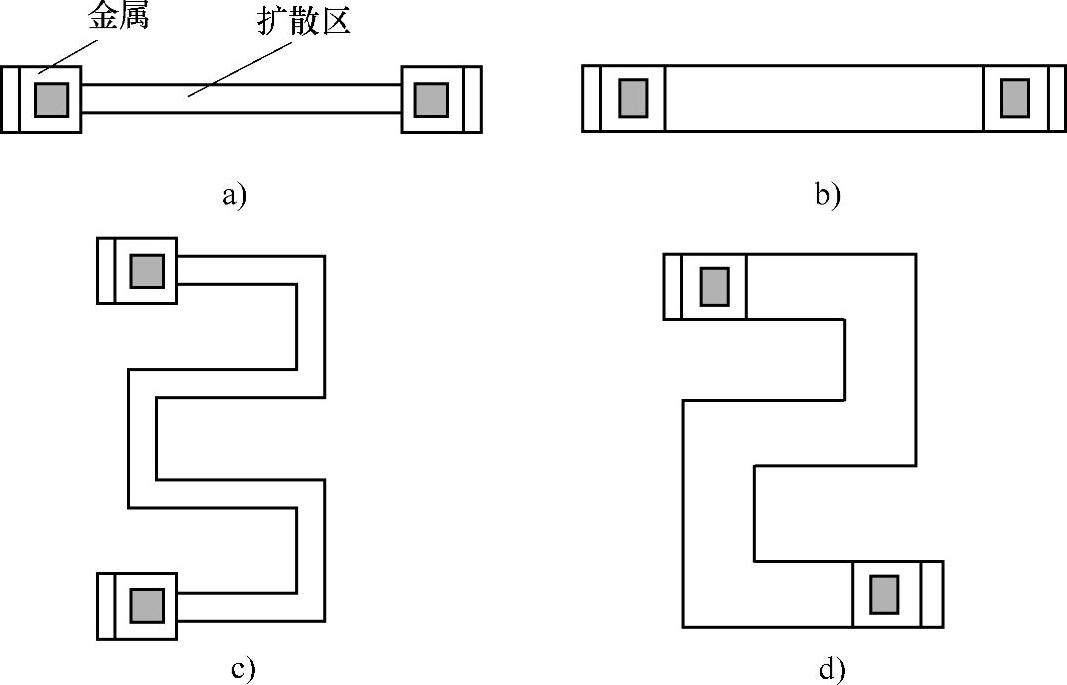

在电阻版图设计的过程中,电阻版图的布局依据是一般电阻采用窄条结构,高精度电阻采用宽条结构,小电阻采用直条结构,大电阻采用弯折结构。不同要求下的电阻版图示意图如图3-6所示。

图3-6 不同要求下的电阻版图示意图

在电阻匹配要求比较高的电路中,比如差分放大器、带隙基准电路等电路中,要求两个电阻的阻值要精确匹配,不但包括电阻值,还要包括其他参数对电阻的影响也要一致,例如,温度对两个电阻的影响也要一致。此时就要考虑用特殊的方式来实现电阻版图。比较常用的方式主要包括增加伪器件、采用标准电阻和交叉结构等。所谓伪器件即是没有电学连接,只是为了保证所用电阻的周围有相同的环境,而刻意添加上去的区域。

(3)电容 电容是集成电路中最基本的无源元件之一,在电源滤波电路、信号滤波电路和开关电路中经常用到。集成电路中的电容一般都是平板电容,但电容一般用在高速集成电路中,普通集成电路考虑到成本问题,一般不会集成电容在芯片中。在高速集成电路中,实现电容的方法也有很多种,比较常见的包括:①利用二极管和晶体管的结电容。②利用插指金属结构。③利用金属-绝缘体-金属结构。④利用多晶硅/金属-绝缘体-多晶硅结构。

1)MOS栅电容。在CMOS工艺中,用来制造MOS晶体管的栅氧化层也可以用于制造电容。电容的上极板由掺杂的多晶硅组成。电容的下极板由扩散区组成,对于NMOS晶体管为轻掺杂的衬底,对于PMOS晶体管为N阱。这种元件的电容率一般为0.5~1.5fF/μm2,典型的电容容差可达±20%。如果不能对电容的两极板保持足够的偏置,则电容值将会显著下降,所以一般使用时将使该晶体管工作在积累区,即将NMOS的源漏作为一极接在电源处,同样将PMOS的源漏作为一极接在GND处。

2)双层多晶硅电容。双层多晶硅电容是指使用双层多晶硅作为电极(也可以用金属作为其中一极),中间以氧化物作介质的电容,通常是多晶硅-二氧化硅-多晶硅结构,由于做这种电容需要两次多晶硅工艺,所以比单次多晶硅工艺要多几道工序。要注意,双多晶硅电容是做在场氧层上的,电容的上下极通过场氧层与其他器件及衬底隔开,是个寄生参数很小的固定电容。只要能精确控制所生长的氧化层介质的质量和厚度,就可以得到精确的电容值,其单位电容的典型值为0.3~0.4fF/μm2。此数值较小是因为其二氧化硅的厚度比栅氧层要大些。

3)多晶硅+掺杂区电容。这是一种以金属或重掺杂的多晶硅作为上极板,栅氧化层为介质,重掺杂区为下极板形成的电容,这是单层多晶硅工艺中常用的电容制作方法。先在下极板区域进行掺杂,这是为做电容专门增加的一次工艺,然后用常规工艺生长栅氧化层和淀积作为上电极的多晶硅,以重掺杂区为下极板。另外,这类电容的下极板与衬底之间会有比较大(约20%)的寄生电容,所以电容精度不高,用在要求不高的电路中。

(4)电感 在集成电路开始出现以后很长的一段时间内,人们一直认为电感不能集成在芯片上,由于当时的集成电路工作最高频率在兆赫数量级,所以芯片上金属线的电感效应非常小。现在芯片的工作频率越来越大,工作速度越来越高,芯片上金属结构的电感效应越来越明显,使得芯片电感的实现成为可能。

比较常见的实现电感的方式是以集总电感和传输线元件的形式来实现的。

1)集总电感。集总电感一般有两种形式:单匝线圈和圆形、方形或其他螺旋形多匝线圈。假定衬底足够厚(大于200μm),由空气桥组成的单匝线圈的电感值为

L=1.26a[ln(8πa/w)-2] (3-2)

式中,L是电感值,单位为pH;a是线圈半径,单位为μm;w是导线宽度,单位为μm。

螺旋形多匝线圈可以做到更高的电感值,由空气桥组成的多匝线圈的电感值为

式中,L是电感值,单位为pH;ro为螺旋的外半径,单位为μm;ri为螺旋的内半径,单位为μm;N为匝数。

电感的电阻可以采用与互连线电阻相同的计算方法进行计算,但在电路的工作频率超过2GHz时必须要考虑趋肤效应。所谓趋肤效应即是对于导体中的交流电流,靠近导体表面处的电流密度大于导体内部电流密度的现象。随着电流频率的提高,趋肤效应使导体的电阻增大,电感减小。

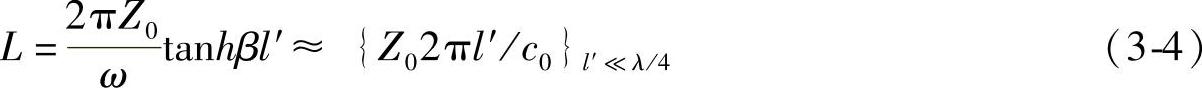

2)传输线元件。还有一种方法可以实现电感,即采用长度l<λ/4(λ为波长)的短传输线或使用长度在λ/4<l<λ/2范围内的开路传输线。采用这种方式的电感其电感值可以精确地进行计算,基本的电感计算公式为

式中,Z0为传输线的特征阻抗;l′为传输线元件长度;c0为光速;β为波的传播相位。

此外,还可以用一小段高阻抗金属线实现很小的电感值的双端口电感。

通常键合线的电感是无用的寄生参数,有时也可以用它们来提高高频电路的性能。

上海某公司的技术文件说明了制作集成电路中电感的一种方法,其基本步骤如下:

1)在介质层上淀积一层金属。

2)采用光刻工艺定义出电感的图形。

3)进行金属层刻蚀,去除光刻胶,形成金属线圈。

4)接着淀积介质层,并在介质层上形成通孔。

5)填充通孔的填充金属。

6)重复步骤1)至步骤5)以增加电感的层数,直到形成最后一层金属线圈。

集成电路中的电感,包含多层相互平行的金属线圈,相邻金属线圈通过连接接触孔相连接。利用上述制作步骤制作的集成电路电感包括多层金属线圈,增强了电感的磁场强度。

2.有源器件

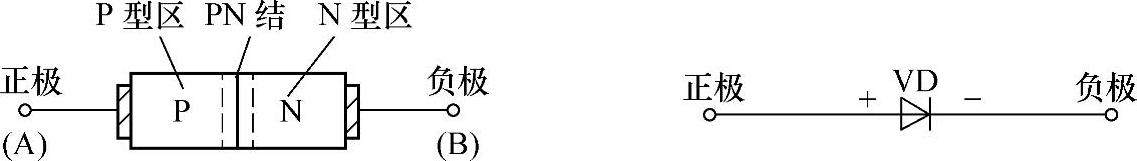

(1)二极管 二极管是集成电路中比较常用的一种器件,特别是在双极型集成电路中。二极管的基本结构是一个PN结,在PN结结构的左右两面加上欧姆接触(欧姆接触是指电极之间形成线性电阻的接触)的电极就得到一个普通的二极管(注意,在有些书中,二极管归于无源器件)。普通PN结二极管的基本结构和符号如图3-7所示。

图3-7 普通PN结二极管的基本结构和符号

根据半导体物理的知识,可以得到结型半导体二极管的电流方程为

式中,ID为二极管的电流;IS为二极管的反相饱和电流;q为电子电荷数;VD为二极管外加的电压。电流方向定义:P电极为正端,N电极为负端。

除了普通的半导体PN结二极管之外,还有一种肖特基结二极管,肖特基结二极管是由金属与掺杂半导体接触形成的二极管。金属与半导体在交界处形成阻挡层,处于平衡态的阻挡层对外电路成电中性。以N型半导体与金属形成的肖特基二极管为例,当在金属端外加正电压时,从半导体到金属的电子数超过从金属到半导体的电子数,平衡被打破,形成一股从金属到半导体的正向电流,该电流由半导体的多数载流子构成。当加反向电压时,从半导体到金属的电子数目减少,金属到半导体的电子数目增加,形成从半导体到金属的反向电流。由于从金属到半导体的电子数目基本是恒定的,因此当反向电压增加时,半导体到金属的电子流可以忽略不计,反向电流将趋于饱和。

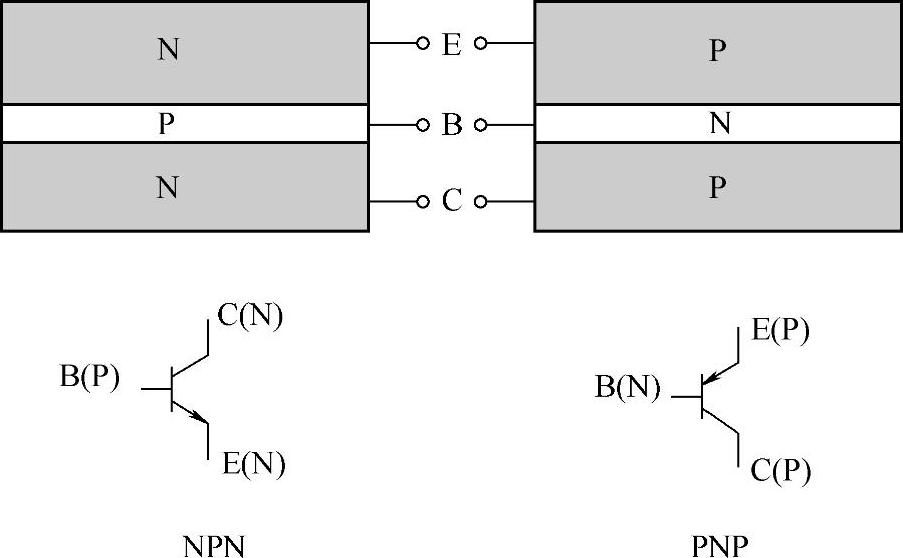

(2)双极型晶体管 在半导体中形成两个很近的PN结即可构成最基本的双极型晶体管。这两个PN结将半导体分成三个区域,它们的排列顺序可以是N-P-N或P-N-P,分别对应着NPN型晶体管和PNP型晶体管。双极型晶体管的结构与符号图如图3-8所示。

结构图中的三个区域从上往下分别为发射区、基区和集电区,对应引出的电极分别为发射极E、基极B和集电极C。E-B之间的PN结称为发射结,C-B之间的PN结称为集电结。

由于双极型晶体管有两个PN结,所以对应不同的工作电压有4种不同的工作状态:

1)发射结正偏,集电结反偏,为放大工作状态。

2)发射结正偏,集电结正偏,为饱和工作状态。

3)发射结反偏,集电结反偏,为截止工作状态。

4)发射结反偏,集电结正偏,为反向工作状态。

在由双极型晶体管组成的集成电路(简称双极型集成电路)中,由于元器件之间需要相互隔离及连接,因此其结构和单个双极型晶体管的结构有所不同。一般情况下,双极型集成电路的集电极是从管芯的上表面引出的,并且在N型集电区的下面专门制作一个n+隐埋层,以减小集电极的串联电阻。

图3-8 双极型晶体管的结构与符号图

在双极型集成电路中双极型晶体管的基本功能是对电流、电压或功率进行放大,因此主要应用其放大工作状态。而在脉冲与数字电路中主要应用其饱和工作状态和截止工作状态,可以看做一个开关电路。

在放大工作状态下,发射结外加正偏电压VBE,集电结外加反偏电压VBC,由于发射结正偏,使发射结宽度变窄,扩散运动占优势。重掺杂发射区的大量电子注入到基区,形成电子电流IE。注入到基区的电子成为基区的非平衡少数载流子,将继续向集电结方向扩散。在扩散的过程中,有少数的电子与基区中的多子空穴复合,形成基极复合电流IB,大部分电子到达集电结的边界,并在集电结的电场作用下,漂移到集电区形成集电极电流IC。双极型晶体管的放大作用就用正向电流放大倍数βF来描述,其基本定义为

βF=IC/IB (3-6)

注意:当双极型晶体管处于反向工作状态时,从原理上来讲与工作于放大状态没有本质上的不同,但由于双极型晶体管的实际结构不对称,特别是在集成电路中,其发射区嵌套在基区内,基区又嵌套在集电区内,发射结比集电结小很多,因此反向电流放大倍数也要小很多,故反向工作状态基本不会出现在集成电路中。

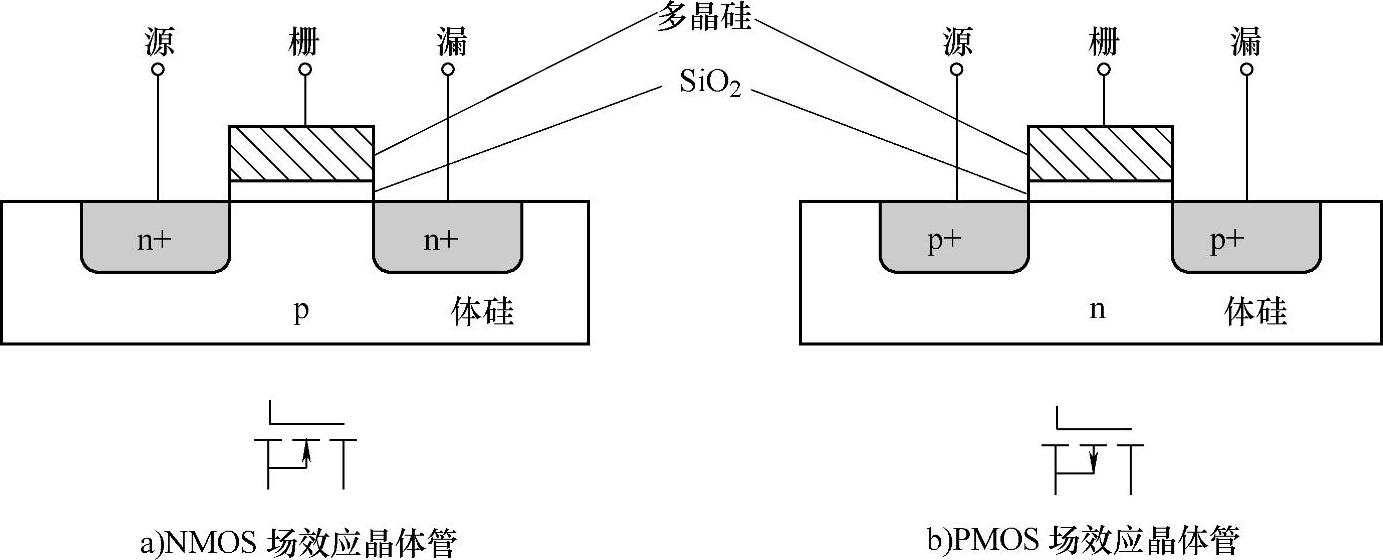

(3)MOS晶体管 MOS(Metal-Oxide-Semiconductor,MOS)晶体管是一种将金属、氧化物和半导体叠加在一起形成的器件。MOS晶体管根据导电沟道的不同又可以分为NMOS晶体管和PMOS晶体管,根据沟道的有无可以分为增强型MOS晶体管和耗尽型MOS晶体管,本书中的晶体管,如果没有特殊说明,都是指增强型晶体管。MOS晶体管是基于电场工作的,因此又称为金属氧化物半导体场效应晶体管(Mteal Oxide Semiconductor Field Effect Transistor,MOSFET),NMOS晶体管和PMOS晶体管及其符号如图3-9所示。

每个MOSFET都由导电的金属、二氧化硅绝缘层和硅片组成,都包括栅极(Gate,导电的金属,一般是铝)、漏极(Drain,扩散区)、源极(Source,扩散区)和体极(Bulk),而且源极和漏极可以互换(当没有连接在电路中的时候,源极和漏极在结构上是互相等价的)。

栅极是输入控制端,因此说MOS晶体管是电压控制器件,栅极能够影响源极和漏极之间的电流流动。对于NMOS晶体管来说,其衬底一般接地,所以源极和漏极对衬底之间的PN结是反偏的。

如果N沟MOS晶体管的栅极接地,即接低电平,那么两个反偏的PN结之间没有电流流过,这时MOS晶体管是不工作的,称该MOS晶体管关断(OFF)。如果升高栅极电压,那么就可以形成电场,开始吸引准自由电子聚积到Si-SiO2的界面下方。如果栅极电压增大到一定程度,那么在栅极下方的硅片表面的位置,电子数量就会超过空穴的数量并达到一定的数值,就会形成一个反型的区域,称为沟道(Channel),这样在源极和漏极的扩散区之间就形成一个由电子载流子形成的导电通道,电流可以从其中流过,这时MOS晶体管是正常工作的,称该MOS晶体管导通(ON)。

1)MOS晶体管的基本工作原理。MOS晶体管是电压控制器件,可以看成是一个“理想”的开关。MOS晶体管是一种多数载流子起作用的器件,其中源极和漏极之间的导电沟道中的电流由加载在栅极上的电压所控制。在NMOS晶体管中,多数载流子是电子,在PMOS晶体管中,多数载流子是空穴。

图3-9 NMOS和PMOS晶体管及其符号

图3-10 简单的NMOS晶体管沟道形成示意图

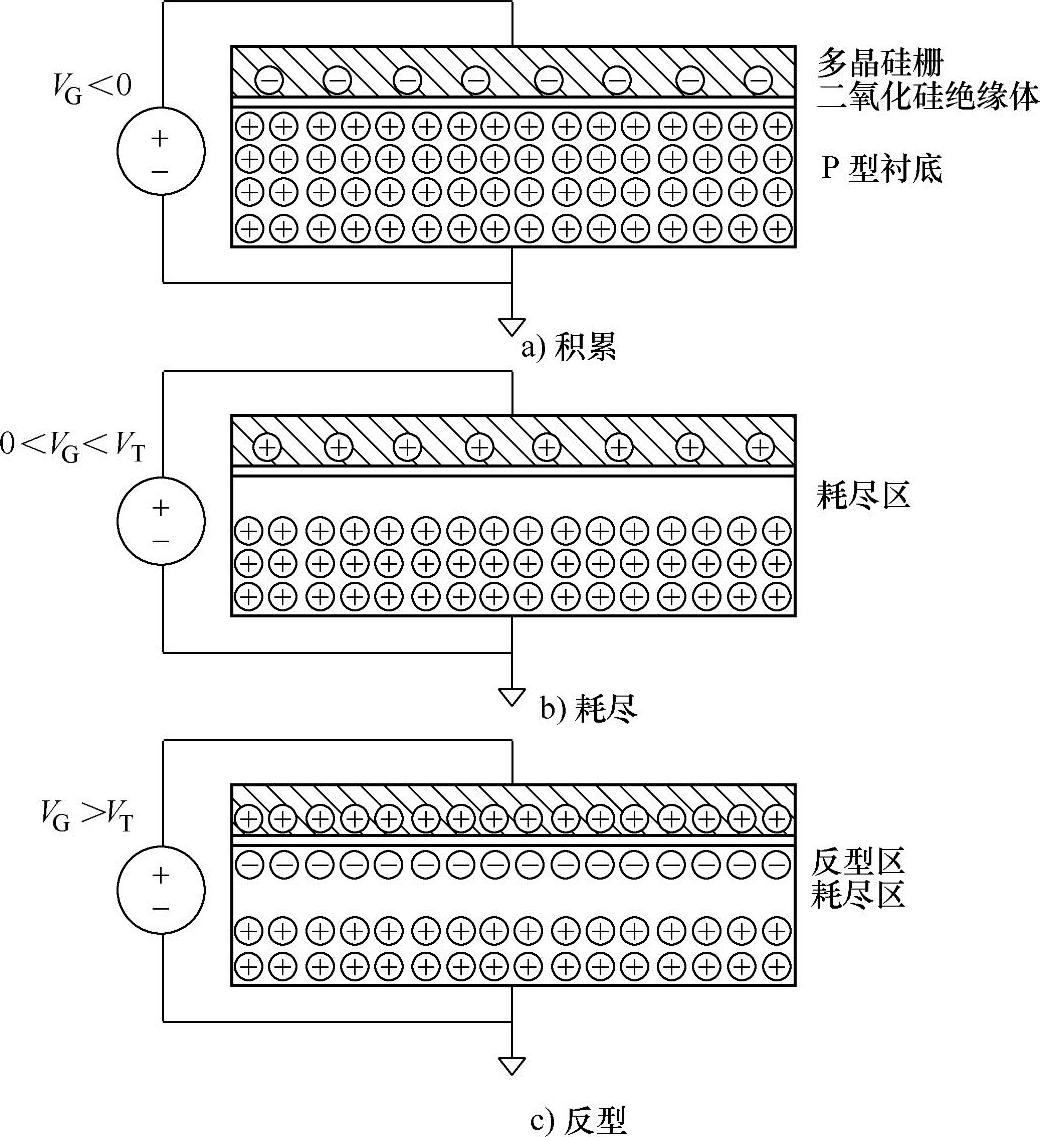

① N沟道形成过程。图3-10所示为简单的NMOS晶体管沟道形成示意图。

当在栅极上加载负电压时,栅极上充入的是负电荷,因此硅中运动的正电荷(带正电的空穴)被吸引到栅极下方的区域中,如图3-10a所示,这个过程称为积累(Accumulation);当在栅极上加载一个较低的正电压时,导致在栅极上充入一些正电荷,因此硅中的带正电荷的空穴被排斥出栅极的正下方硅体表面,从而在栅极下方形成一个耗尽区(Depletion Region),如图3-10b所示,这个过程称为耗尽(Depletion);当在栅极加载一个大于阈值电压VTN的正电压时,栅极正下方硅体表面的空穴被排斥到更远的位置,同时硅体中少量的准自由电子被吸引到栅极下方的区域中,在栅极下方形成一个导电薄层,这个导电层称为反型层(Inversion Layer),图3-10c所示这个过程称为反型(Inversion)。

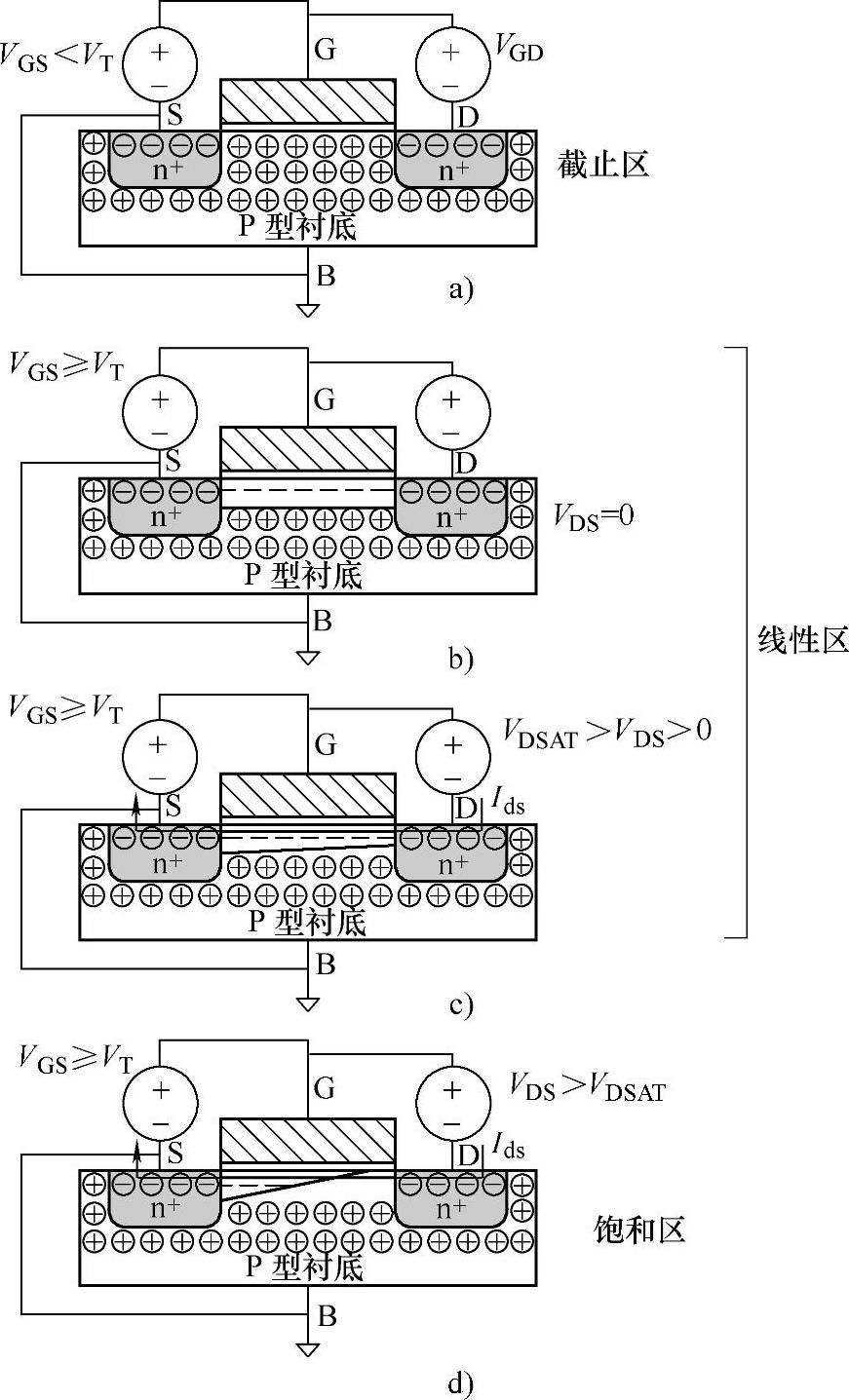

② NMOS晶体管的基本工作状态。NMOS晶体管工作的截止、线性和饱和区示意图如图3-11所示,其中源极接地。

当栅源电压VGS小于阈值电压VTN时,如图3-11a所示,在栅极下方没有形成导电沟道,漏极和源极之间没有电流流过,这个工作状态称为截止态(Cutoff)。

当栅源电压VGS大于等于阈值电压时,如图3-11b所示,在栅极下方形成导电反型层,称为沟道(Channel),使源极和漏极之间形成导电通路,载流子的数量和导电性随栅极所加电压的增大而增强,漏极和源极之间的电位差为VDS=VGS-VGD。

如果VDS=0,则漏极到源极之间没有推动电流流动的电场,如图3-10b所示。

如果增大VDS,使VDS为一个较小的正电压,则在漏极和源极之间会产生电流,这个工作状态称为线性工作区,或称为非饱和工作区,如图3-11c所示。

如果VDS增大到使靠近漏极的沟道临界夹断,对应的电压称为临界饱和电压VDsat,VDsat=VGS-VTN。

如果VDS足够大,使得VGD<VTN,那么漏极附近的沟道会消失,产生夹断(Pinched Off),如图3-11d所示。但是正的漏极电压引起的电子漂移仍然会具备导电性。当电子到达沟道末端时,它们被注入漏极附近的耗尽区中,并加速流向漏极。当漏极所加电压超过临界饱和电压时,电流IDS仅受栅电压的控制,并且不再受漏极的影响,这个状态称为饱和态(Saturation)。(https://www.xing528.com)

总而言之,NMOS晶体管有三个工作状态。如果VGS<VTN,晶体管截止,没有电流流过。如果VGS≥VTN,且VDS较小,晶体管的工作状态就像一个线性电阻,其漏极和源极之间的电流IDS与VDS成正比。如果VGS≥VTN,且VDS较大,那么晶体管就像一个电流源,其漏极和源极之间的电流IDS与VDS无关。

图3-11 NMOS晶体管工作的截止、线性和饱和区示意图

尽管MOS晶体管的结构是对称的,但是我们一般说多数载流子是从源极流向漏极的,由于电子是带负电的,所以NMOS晶体管的源极是两极中电平偏低的一极。空穴是带正电的,因此PMOS晶体管的源极是两极中电平偏高的一级。在互补CMOS门中,源极更靠近电源导线,而漏极更靠近输出端。

2)MOS晶体管的直流特性。在分析MOS晶体管的直流特性之前,考虑器件内部的多种不确定因素,先做以下几种假设:

① 源极电极与沟道之间、漏极电极与沟道之间的压降忽略。

② 沟道电流为漂移电流。

③ 在反型层中电子迁移率为常数。

④ 沟道与衬底之间的PN结反向截止。

⑤ 沟道中任意一点y处的横向电场Ey远小于该处的纵向电场。

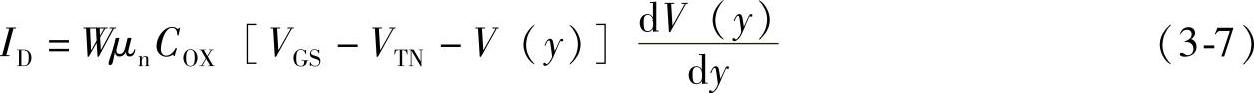

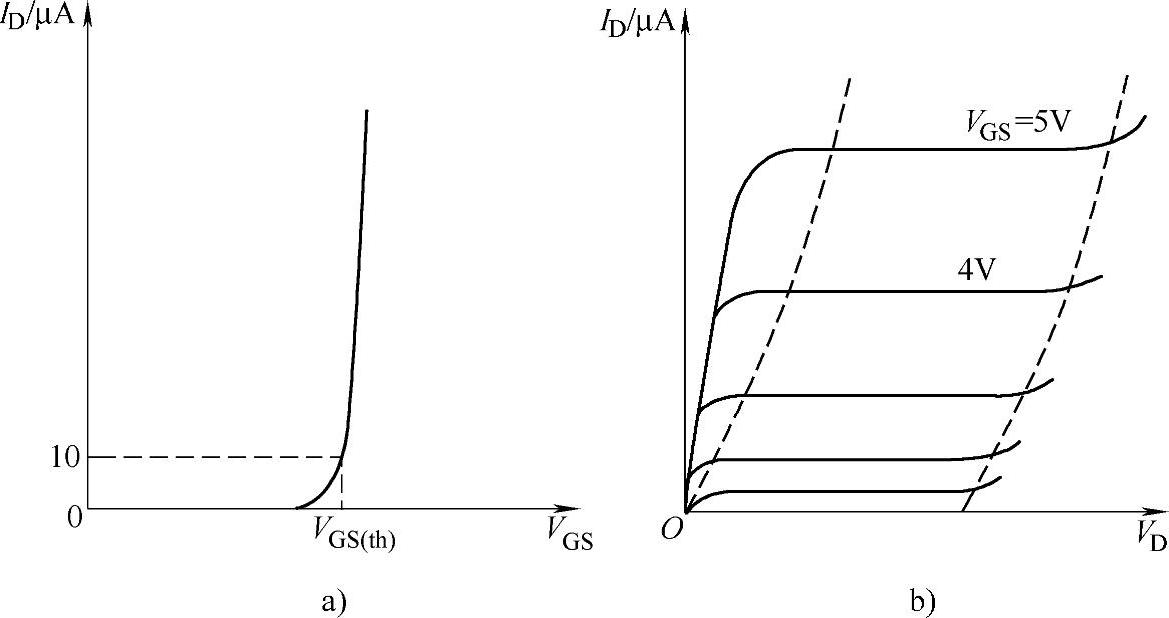

现在以NMOS晶体管为例,来分析MOS晶体管的基本直流特性,NMOS晶体管的转移特性和输出特性曲线如图3-12所示。根据半导体物理学的相关知识,在沟道中任一处的电流为

式中,ID为沟道电流;W为沟道宽度;μn为电子迁移率;COX为栅氧单位面积电容;VGS为栅端电压;VTN为阈值电压;V(y)为y点处电压。

图3-12 NMOS晶体管的转移特性和输出特性曲线

根据图3-12所示曲线可以将NMOS晶体管的工作特性分为以下三个区间:

① 截止区。当VGS小于管子的阈值电压VTN时,NMOS晶体管处于不导通状态,此时源极和漏极之间的电流IDS为0。

② 线性区。当栅端电压VGS大于MOS晶体管开启电压VTN时,管子开启导通。如果源极和漏极之间的电压VDS比较小,随着VDS的逐渐增大,V(y)也逐渐上升,此时有

式中, ;COX为栅氧单位面积电容。

;COX为栅氧单位面积电容。

当 ,此时沟道中的压降比较小,式(3-7)中的V(y)可以忽略掉,此时有

,此时沟道中的压降比较小,式(3-7)中的V(y)可以忽略掉,此时有

③ 饱和区。当VDS≥VGS-VT时,处于饱和状态,得到饱和电流为

VDS=VGS-VT时对应的电压称为临界饱和电压,记为VDsat。随VDS的增大,夹断区开始变大,此时沟道的有效长度为

如果忽略沟道长度的变化,夹断后的电流基本保持不变。

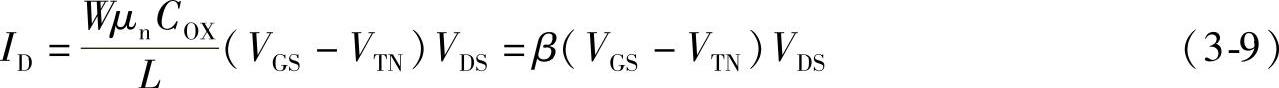

对于PMOS晶体管,其特性和NMOS晶体管是十分相似的,只不过特性曲线出现在第三象限。PMOS晶体管的直流特性曲线如图3-13所示。

读者自己根据这三个分区的划分情况,可以在PMOS晶体管的直流特性曲线上分别标注这三个分区的位置。

图3-13 PMOS晶体管的直流特性曲线

3.有源器件模型

在集成电路设计的过程中,为了在流片以前了解电路的基本工作特性,需要预先分析电路的工作特性,此时需要进一步了解电路中各个元器件的基本工作特性。可以采用预先模拟的方式,在模拟的时候,就需要知道元器件的基本特性参数,即元器件所对应的模型。

(1)二极管 一般的二极管就是一个PN结,在实际电路中,一个实际的二极管不仅包含一个单向导电性的PN结,还包含一个寄生电阻和至少两个不同性能的寄生电容。

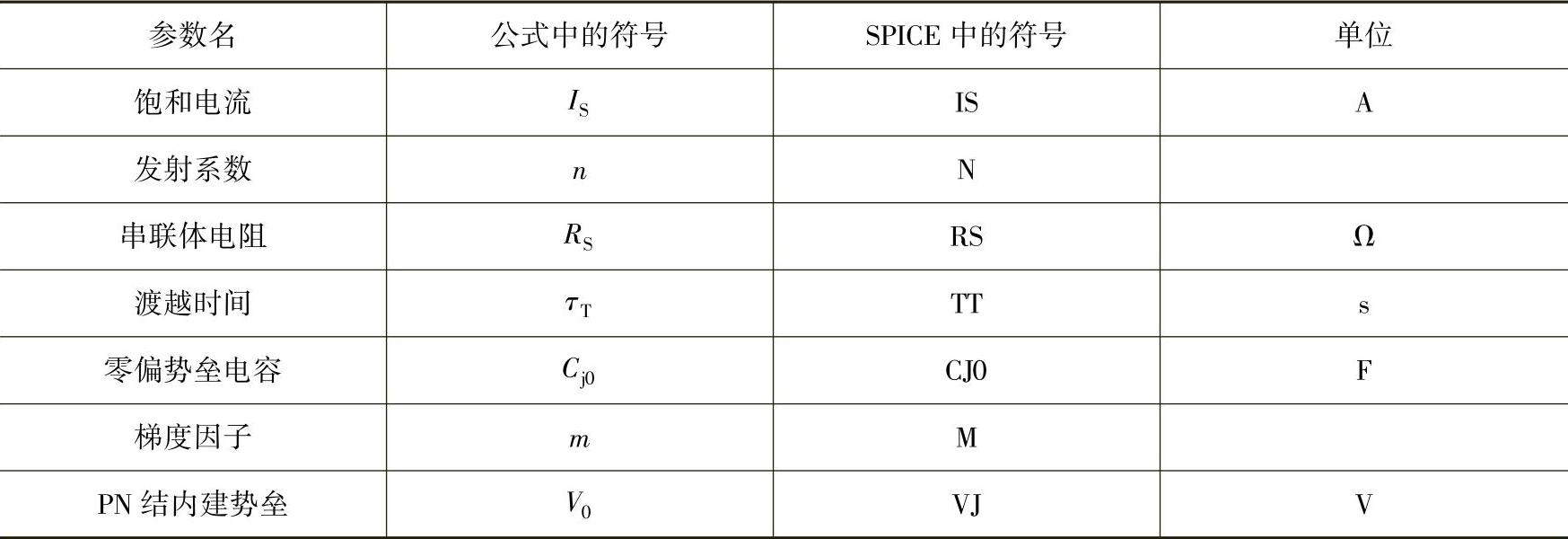

工艺厂家提供的二极管模型参数对照表见表3-1。

表3-1 二极管模型参数对照表

下面给出一个普通二极管的工艺模型数据,如下所示:

.MODEL DIODE D(IS=5.3253E-12 N=3.4748 RS=1.0000E-3 CJ0=1.0000E-12 M=.3333

+VJ=.75 ISR=100.00E-12 BV=120 IBV=1.00E-6 TT=5.0000E-9)

(2)双极型晶体管 双极型晶体管在模拟集成电路和数字集成电路中都广泛存在。一般情况下SPICE中的双极型晶体管采用Ebers-Moll(EM)模型和Gummel-Poon(GP)模型。这两种模型均属于物理模型,其模型参数能较好地反映物理本质且易于测量。

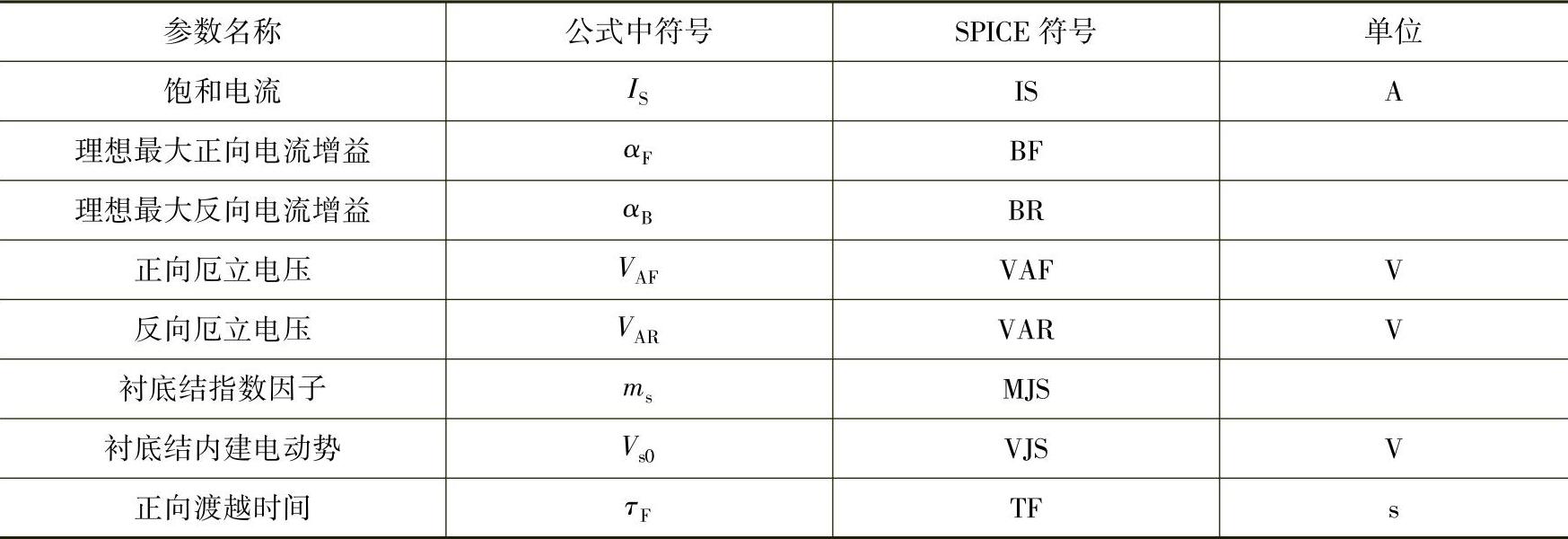

工艺厂家提供的双极型晶体管模型参数对照表见表3-2。

表3-2 双极型晶体管模型参数对照表

下面给出一个普通双极型晶体管的工艺模型数据。

NPN型晶体管模型数据:

.MODEL NPNNPN

+IS=1.501E-12BF=772.1 NF=1 VAF=100

+IKF=.1298ISE=163.8E-12 NE=1.998 BR=499.5

+NR=1 VAR=100 IKR=19.98 ISC=1.536E-12

+NC=2.997 RB=1.101 NK=.5077

+RE=0RC=.1498 EG=1.110

+CJE=316.6E-12 VJE=.436 MJE=.2878 TF=16.416E-9

+XTF=1 VTF=10 ITF=10.00E-3 CJC=189.3E-12

+VJC=.6244 MJC=.1866 XCJC=.9FC=.5

+TR=13.837E-9

PNP型晶体管模型数据:

.MODELPNPPNP

+IS=1.500E-12 BF=2.997E3 NF=1 VAF=100

+IKF=.263 ISE=6.747E-12 NE=1.413 BR=499.5

+NR=1 VAR=100 IKR=19.98 ISC=19.59E-12

+NC=2.997 RB=1.0845 NK=.5779

+RE=0 RC=0.196311 EG=1.110

+CJE=316.6E-12 VJE=.436MJE=.2878TF=9.781E-9

+XTF=1VTF=10 ITF=10.00E-3 CJC=372.5E-12

+VJC=1.177 MJC=.2738 XCJC=.9FC=.5

+TR=7.561E-9

(3)MOS晶体管 美国加州伯克利分校在20世纪70年代曾推出了包含在SPICE软件包中的MOS场效应晶体管模型:1级模型通过电流电压的平方律特性描述,2级模型是一个详尽解析的MOS场效应晶体管模型,3级模型是一个半经验型模型。2级和3级模型都考虑了短沟道阈值电压、亚阈值电导、速度饱和分散限幅、电荷控制电容等二阶效应的影响。到了20世纪90年代,又出现了BISM3版本,即伯克利短沟道IGFET模型。在商业版的SPICE中包含有更多的、更精确的器件模型。

在模型文件中一般用LEVEL变量标明不同的MOS晶体管模型。LEVEL=1对应Shich-man-Hodges,LEVEL=2对应Grove-Forhman,LEVEL=3对应半经验短沟道模型,LEVEL=49对应BSIM3V3模型。

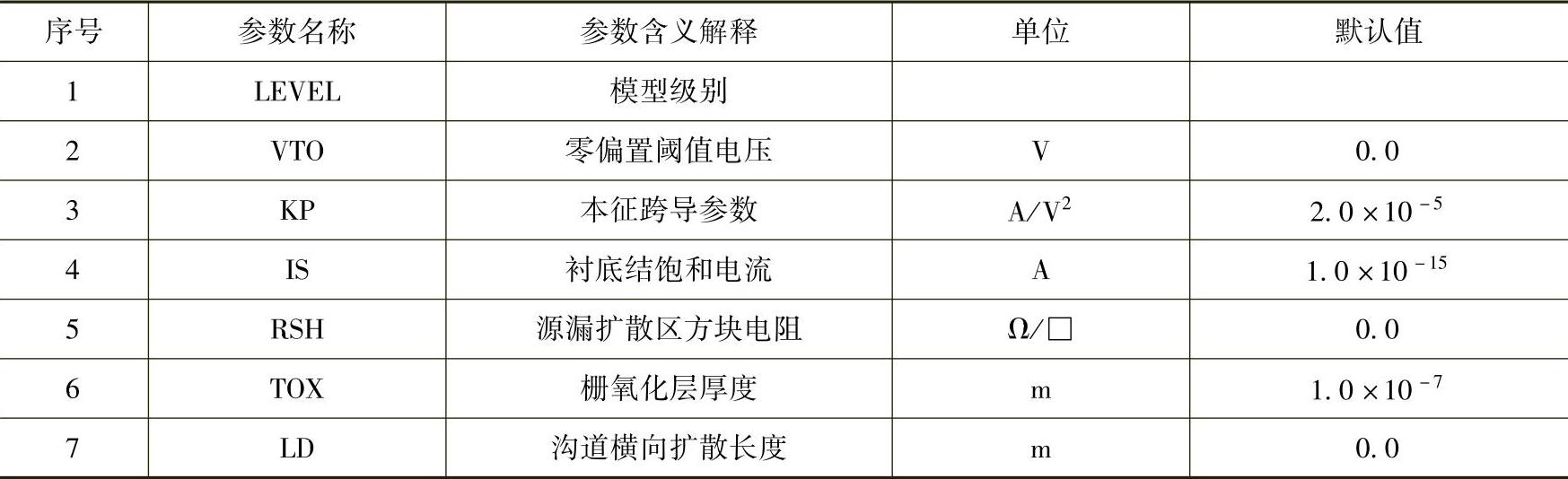

下面给出MOS晶体管LEVEL为1、2、3时包含的部分模型参数,MOS晶体管模型参数见表3-3。

表3-3 MOS晶体管模型参数

下面给出普通MOS晶体管的工艺模型数据。

NMOS晶体管模型数据:

.model nmos nmos

+Level=2Ld=0.0uTox=225.00E-10

+Nsub=1.066E+16Vto=0.622490 Kp=6.326640E-05

+Gamma=.639243 Phi=0.31 Uo=1215.74

+Uexp=4.612355E-2 Ucrit=174667 Delta=0.0

+Vmax=177269Xj=.9u Lambda=0.0

+Nfs=4.55168E+12 Neff=4.68830 Nss=3.00E+10

+Tpg=1.000 Rsh=60 Cgso=2.89E-10

+Cgdo=2.89E-10 Cj=3.27E-04 Mj=1.067

+Cjsw=1.74E-10 Mjsw=0.195

PMOS晶体管模型数据:

.model pmos pmos

+Level=2 Ld=.03000u Tox=225.000E-10

+Nsub=6.575441E+16 Vto=-0.63025 Kp=2.635440E-05

+Gamma=0.618101 Phi=.541111 Uo=361.941

+Uexp=8.886957E-02 Ucrit=637449 Delta=0.0

+Vmax=63253.3 Xj=0.112799u Lambda=0.0

+Nfs=1.668437E+11 Neff=0.64354 Nss=3.00E+10

+Tpg=-1.00 Rsh=150 Cgso=3.35E-10

+Cgdo=3.35E-10 Cj=4.75E-04 Mj=.341

+Cjsw=2.23E-10 Mjsw=0.307

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。