每个通用定时器都有一个比较寄存器TxCMPR和一个PWM输出引脚TxPWM。通用定时器计数器的值一直与相关比较寄存器的值比较,当计数器的值与比较寄存器的值相等时,产生比较匹配。可通过TECMPR(TxCON.1)位使能比较操作。如果比较操作被使能,则比较匹配时将发生下列事件:

●匹配一个时钟周期后,定时器的比较中断标志位置位。

●匹配一个CPU时钟周期后,根据GPTCONA/B寄存器的相应位的配置情况,PWM的输出将产生跳变。

●如果比较中断标志位已通过设置GPTCONA/B寄存器中的相应位启动A-D转换器,则比较中断位置位的同时将产生A-D转换启动信号。如果比较中断未被屏蔽,则将产生一个外设中断请求。

PWM输出的转换由非对称或对称的波形发生器和相关的输出逻辑控制,并与下面的设置有关:

●GPTCONA/B寄存器的设置。

●定时器的计数模式。

●采用连续增/减模式时的计数方向。

根据通用定时器使用的计数模式,非对称/对称波形发生器会产生一个非对称或对称的PWM波形。

(1)非对称波形的产生

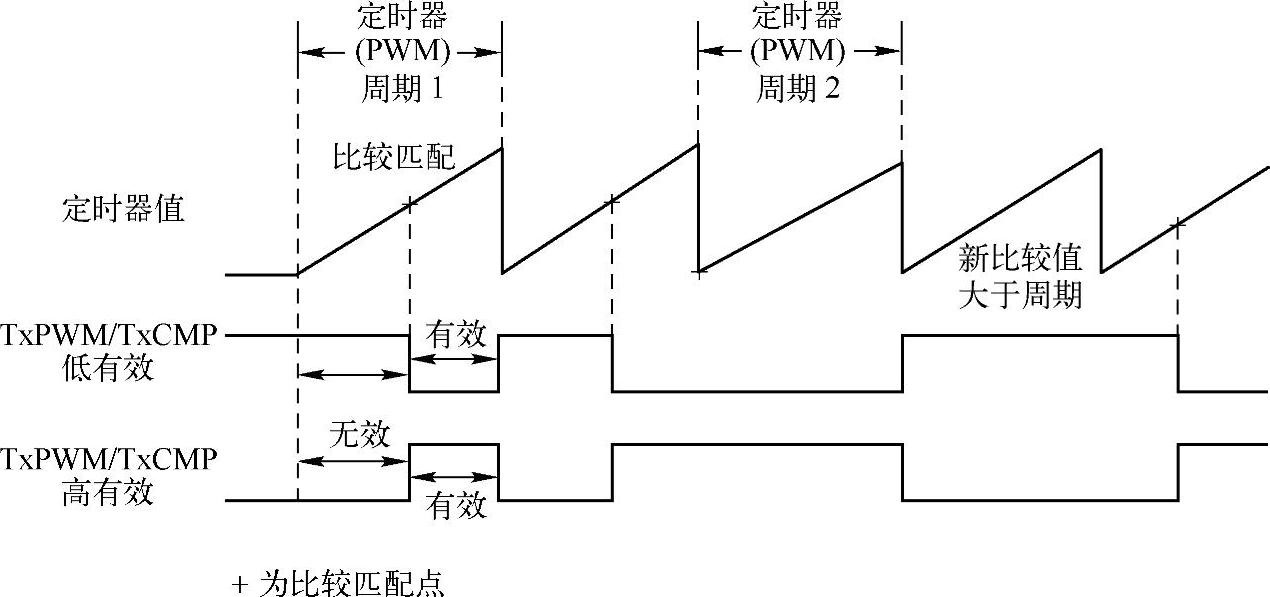

当通用定时器处于连续增计数模式时,产生非对称波形,如图6-6所示。在这种模式下,波形发生器的输出将根据下面的顺序变化:

●计数操作开始前为0。

●在匹配发生前一直保持不变。

●在比较匹配时产生翻转。

●保持不变直到周期结束。

如果下一周期新的比较寄存器的值不是0,则在周期结束时复位到0。

图6-6 通用定时器连续增计数模式下的比较/PWM输出

在周期开始时,如果比较值是0,则整个计数周期内输出保持为1不变。如果下一周期的比较值还是0,则输出也不会被复位为0。这一点很重要,因为它允许产生占空比为0%~100%的PWM无毛刺脉冲。如果比较值大于周期寄存器中的值,则整个周期内输出为0。如果比较值等于周期寄存器的值,则输出是1并只保持一个定标的时钟输入周期。

对于非对称PWM波形,改变比较寄存器的值仅影响PWM脉冲的一侧。

(2)对称波形的产生

当通用定时器处于连续增/减计数模式时,产生对称波形,如图6-7所示。在这种计数模式下,波形发生器的输出状态由下述情况决定:

●计数操作开始前为0。

●保持不变直到第一次比较匹配。

●第一次比较匹配时产生翻转。

●保持不变直到第二次比较匹配。

●第二次比较匹配时产生翻转。

●保持不变直到周期结束。

●如果没有第二次匹配且下一个周期的新比较值不为0,则在周期结束时复位到0。

(https://www.xing528.com)

(https://www.xing528.com)

图6-7 通用定时器连续增/减计数模式下的比较/PWM输出

如果比较值为0,则周期开始时输出为1,并一直保持不变直到第二次比较匹配发生。如果此时比较值仍是0,则输出保持为1。在这种情况下,如果下一周期新的比较值仍然为0,则输出不会复位为0。这将保证能够产生占空比为0%~100%的无毛刺PWM脉冲。如果在前半周期,比较值大于或等于周期寄存器的值,则不会产生第一次跳变。然而在后半周期发生比较匹配时,输出仍将翻转。这种错误的输出跳变经常是由应用程序计算不正确引起的,它将会在周期结束时被纠正过来,因为此时输出将复位到0。但如果此时下一周期的比较值为0,那么输出将保持为1,这将把波形发生器的输出重新设置为正确的状态。

(3)输出逻辑

输出逻辑进一步调整波形发生器的输出,以形成最后的PWM输出去控制不同的电源设备。适当地设置GPTCONA/B寄存器,可以规定PWM的输出为高电平有效、低电平有效、强制低或强制高。

当PWM输出为高电平有效时,它的极性与相关的非对称/对称波形发生器的极性相同。当PWM输出为低电平有效时,它的极性与相关的非对称/对称波形发生器的极性相反。

如果GPTCONA/B寄存器相应的控制位规定PWM输出为强制高(低)后,PWM输出才会立即置1(或0)。

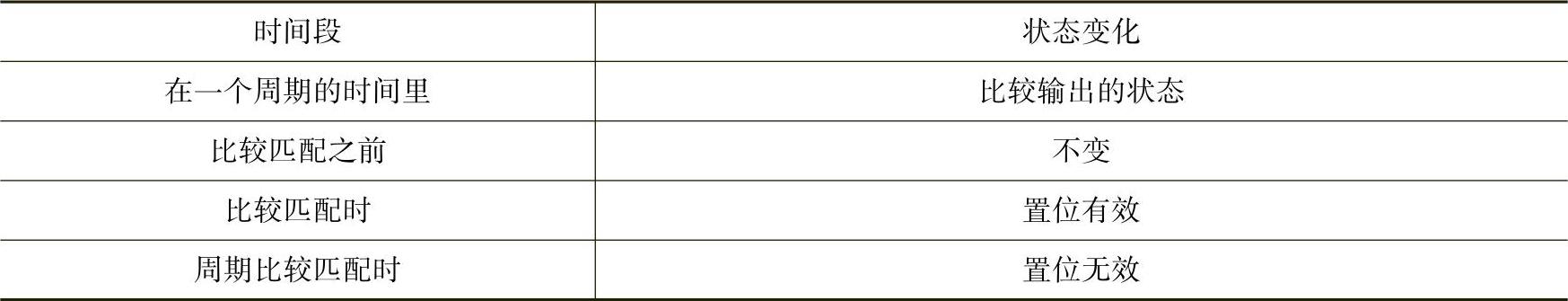

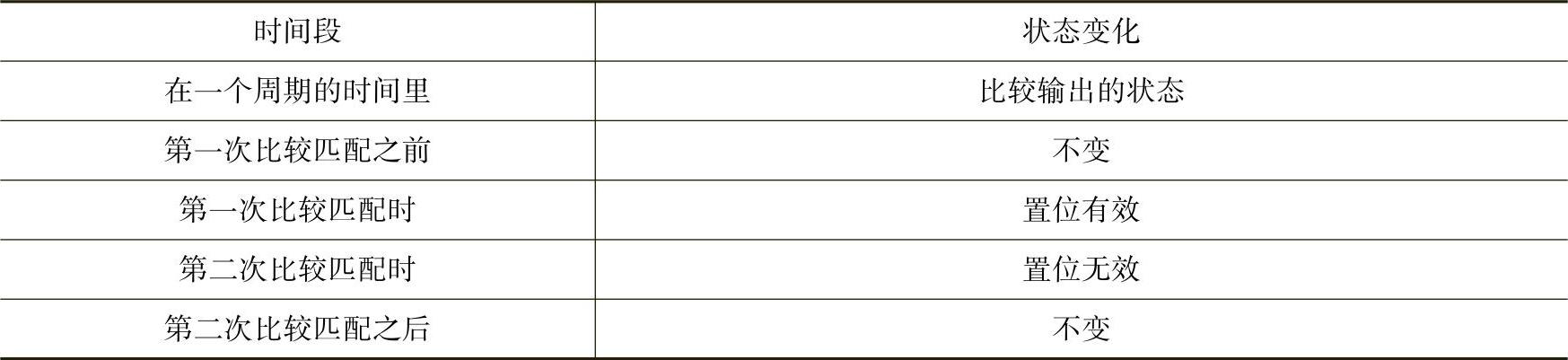

总之,在正常的计数模式下,如果比较已经被使能,则通用定时器的PWM输出会按表6-2、表6-3所示情况发生变化。

表6-2 连续增计数模式下的定时器比较输出

表6-3 连续增/减计数模式下的定时器比较输出

置位有效指高有效时置高,低有效时置低。置位无效则相反。

基于定时器计数模式和输出逻辑的非对称/对称波形发生器同样适用于比较单元。当出现下列情况之一时,所有通用定时器的PWM输出都被置成高阻状态。

●软件将比较输出使能位TCMPOE(GPTCONA/B.6)清零。

●PDPINTx引脚被拉低而且未屏蔽。

●任何一个复位信号产生。

●软件将比较使能位TECMPR(TxCON.1)清零。

1)有效/无效时间计算。对于连续增计数模式,比较寄存器中的值代表了从计数周期开始到第一次匹配发生之间花费的时间(即无效相位的长度)。这段时间等于定标的输入时钟周期乘以寄存器TxCMPR的值。因此有效相位的长度等于TxPR-TxCMPR+1个定标的输入时钟周期,也就是输出脉冲的宽度。

对于连续增/减计数模式,比较寄存器在减计数和增计数状态下可以有不同的值。连续增/减计数模式下的有效相位长度,等于(TxPR)-(TxCMPR)up+(TxPR)-(TxCM⁃PR)dn个定标输入时钟周期,也就是输出脉冲宽度。这里(TxCMPR)up指增计数模式下的比较值,(TxCMPR)dn指减计数模式下的比较值。

如果定时器处于连续增计数模式,当TxCMPR中的值为0时,通用定时器比较输出在整个周期有效。对于连续增/减计数模式,如果(TxCMPR)up的值为0,则比较输出在周期开始时就有效。如果(TxCMPR)up和(Tx CMPR)dn的值都是0,则比较输出在整个周期有效。

对于连续增计数模式,如果TxCMPR的值大于TxPR的值,则有效相位长度(输出脉冲宽度)为0。对于连续增/减计数模式,如果(TxCMPR)up大于或等于TxPR,则将不会产生第一次跳变。同样,如果(TxCMPR)dn的值大于或等于TxPR的值,则也不会产生第二次跳变。

如果(TxCMPR)up和(Tx CMPR)dn的值都大于TxPR的值,则通用定时器的比较输出在整个周期内都无效。

2)使用通用定时器产生PWM信号。每个通用定时器都可以独立提供一路PWM输出通道,因此事件管理器的4路个通用定时器可提供4路通道的PWM输出。

用通用定时器产生PWM输出,可以采用连续增或连续增/减计数模式。当选用连续增计数模式时,可以产生边沿触发或非对称PWM波形。当选用连续增/减计数模式时,可产生对称PWM波形。可以通过下列操作产生PWM信号:

●根据所需的PWM(载波)周期设置周期寄存器TxPR。

●设置控制寄存器TxCON,确定计数器模式和时钟源,并启动PWM输出操作。

●将软件计算出来的PWM脉冲宽度(占空比)装载到比较寄存器TxCMPR中。

如果选用连续增计数模式来产生非对称PWM波形,则把所需要的PWM周期除以通用定时器输入时钟的周期,然后减1,便得到定时器的周期数。如果选用连续增/减计数模式产生对称PWM波形,则把所需要的PWM周期除以2倍的通用定时器输入时钟周期,就得到定时器的周期数。在程序运行的过程中,软件可以计算PWM的占空比,并实时刷新比较寄存器的值。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。