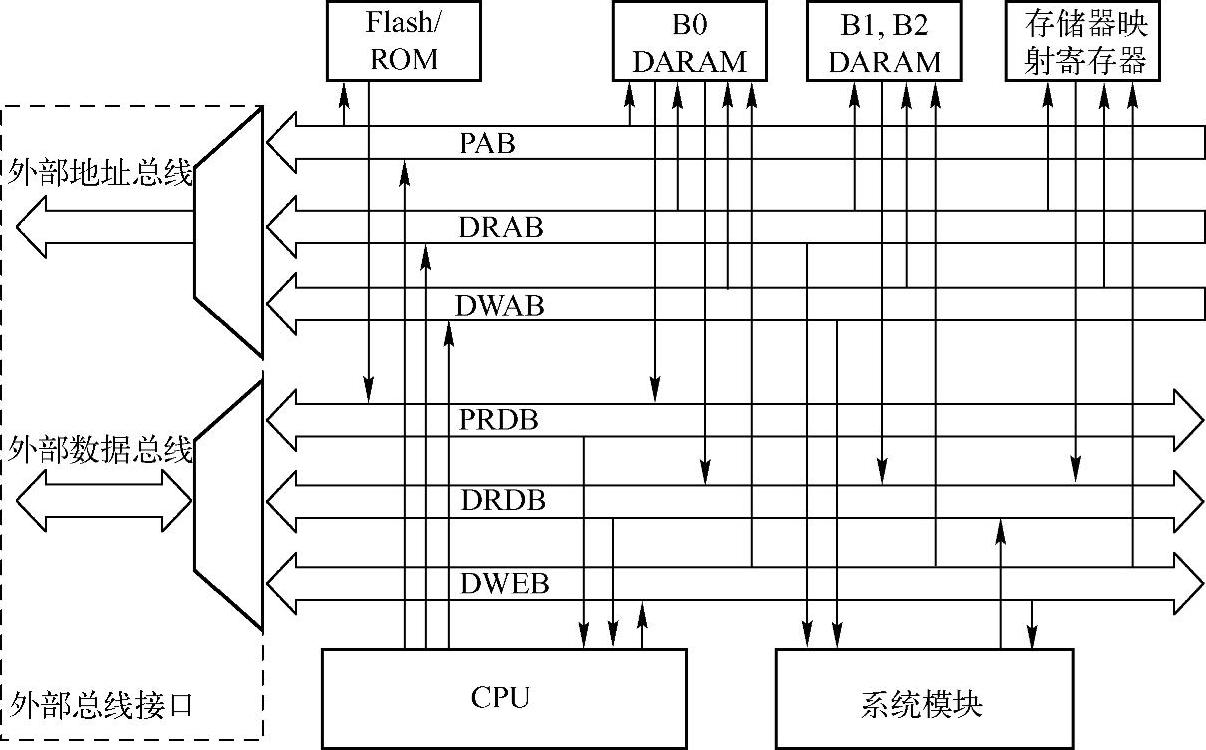

C24x DSP的总线结构如图3-2所示。CPU与存储器的接口地址和数据总线共有6组,包括3组地址总线和3组数据总线。CPU通过这6组独立的地址和数据总线来完成指令和数据的并行读写及处理。

图3-2 C24x DSP总线结构

3组独立的地址总线(Addre ss Bus)包括:

1)程序地址总线(Program Addre ss Bus,PAB)。PAB用于传送来自程序空间的读写地址。

2)数据读地址总线(Data⁃Read Address Bus,DRAB)。DRAB用于传送数据空间的读地址。

3)数据写地址总线(Data⁃Write Addre ss Bus,DWAB)。DWAB用于传送数据空间的写地址。

3组独立的数据总线(Data Bus)包括:(https://www.xing528.com)

1)程序读数据总线(Program⁃Read Data Bus,PRDB)。PRDB在读取程序空间时用于传送指令或数据。

通常CPU自动产生指令的地址并将其通过PAB送往程序存储器,程序存储器中被读取的指令则通过PRDB总线进入CPU的指令队列,这个工作是由CPU硬件自动进行的。对程序空间的访问,被访问的存储器地址通过PAB传递,而被读取的数据通过PRDB来传递。

2)数据读数据总线(Data⁃Read Data Bus,DRDB)。DRDB在读数据空间时用于传送数据。

3)数据/程序写数据总线(Data/Program Write Data Bus,DWEB)。DWEB在对数据空间或程序空间进行写数据时用于传送数据。

通常数据存储器内存放用户定义的变量,由用户通过指令来访问。C24x的CPU内部对数据存储器的读写地址总线是分开的,读写数据总线也是分开的。另外向程序空间和数据空间写操作均通过DWEB传递数据。需要指出的是程序空间的读和写不能同时发生,因为它们都要使用PAB。程序空间的写和数据空间的写也不能同时发生,因为两者都要使用DWEB。运用不同总线的传输是可以同时发生的,如CPU可以在程序空间完成读操作(使用PAB和PRDB),而同时在数据空间完成读或写操作;或者在数据空间完成读操作(使用DRAB和DRDB),同时在数据空间进行写操作(使用DWAB和DWDB)。

DSP芯片外部为16位数据总线和16位地址总线的单一形式。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。