1.CPU中断控制寄存器

CPU中断控制寄存器包括CPU中断标志寄存器(IFR)和CPU中断屏蔽寄存器(IMR)。

(1)CPU中断标志寄存器(IFR)

CPU中断标志寄存器(Interrupt Fla g Register,IFR)是16位的CPU寄存器,地址为0006H,它用于识别和清除挂起的中断。IFR包含CPU级的所有可屏蔽中断(INT1~INT6)的标志位。

当请求一个可屏蔽中断时,对应的外设模块控制寄存器的标志位置1。如果对应的屏蔽位也为1,则向CPU发出中断请求,设置IFR中的相应标志。这表示中断正被挂起或等待应答。

为了识别正挂起的中断,可用PUSH IFR指令,然后测试堆栈值。用OR IFR指令可以置位IFR。用AND IFR指令用户程序可以清除挂起的中断。把IFR寄存器的内容写回IFR或通过硬件复位可以清除所有正挂起的中断。

CPU应答中断或器件复位也可以清除IFR标志。

注:1)为了清除IFR位,必须向其写入1,而不是0。

2)当应答一个可屏蔽中断时,CPU自动清零IFR位。对应的外设模块控制寄存器中的标志位不清零。如果需要清零外设控制寄存器中的标志位,则必须通过软件实现。

3)当中断是通过INTR指令请求且相应的IFR位置1时,CPU不会自动清零该位。如果需要清零IFR位,则必须通过软件实现。

4)IFR和IMR寄存器适用于CPU内核级中断。所有外设模块在其各自的控制/配置寄存器中都有自己的中断屏蔽和标志位。

5)一个内核级中断对应一组外设中断。

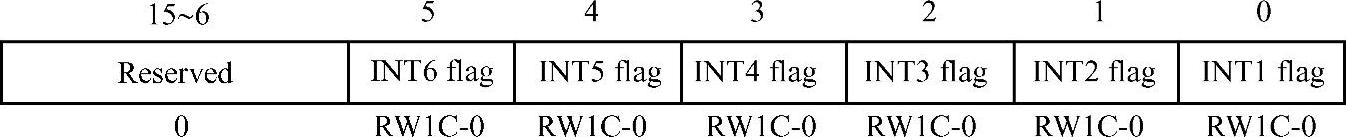

CPU中断标志寄存器(IFR)的格式如下:

位15~6 保留位。

位5~0 INT6 flag~INT1 flag:INT6~INT1中断的申请标志。某位为0时,该位无中断挂起。该位为1时,该位有中断挂起。向其写入1将清零该位和清除中断请求。

(2)CPU中断屏蔽寄存器(IMR)

IMR(Inte rrupt Ma sk Register)是一个16位的CPU寄存器,地址为0004H。IMR包含所有可屏蔽的CPU中断(INT1~INT6)的使能位,该寄存器也被称为中断使能寄存器。NMI(非屏蔽中断)和RS(复位中断)都不包括在IMR中,因此IMR对它们无效。用户可以读IMR去识别已使能或禁止的中断,也可以写IMR来使能或禁止中断。为了使能一个中断,可以用OR IMR指令把对应的IMR位置1。为了禁止一个中断,可以用AND IMR指令把对应的IMR位清零。当禁止一个中断时,不论INTM位的值是什么,都不响应它。当使能一个中断时,如果对应的IFR位为1和INTM位为0,则中断会得到应答。

复位时,IMR=0,禁止所有可屏蔽的CPU级中断。

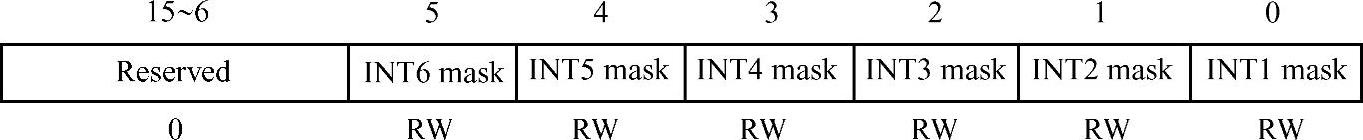

CPU中断屏蔽寄存器IMR的格式如下:

位15~6 保留位。

位5~0 INT6 mask~INT1 mask:中断的使能位,可以使能或禁止相应的中断。某位设置为0时,禁止对应的中断;为1时,使能该中断。

2.外设中断扩展模块寄存器

外设中断扩展模块寄存器包括外设中断向量寄存器(PIVR)、外设中断请求寄存器(PIRQR0、PIRQR1、PIRQR2)、外设中断应答寄存器(PIACKR0、PIACKR1、PIACKQR2)。

外设中断请求寄存器和外设中断应答寄存器都属于外设中断扩展模块用来向CPU产生INT1~INT6中断请求的内部寄存器。这些寄存器主要用于测试,而不用于用户应用程序。

(1)中断向量寄存器(PIVR)

外设中断向量寄存器(Periphera l Inte rrupt Vector Register,PIVR)映射在数据存储器空间中的地址为701Eh,该寄存器的16位V15~V0,为最近一次被应答的外设中断的地址向量。用户可以读取该向量值,以确定是哪一个中断。

(2)外设中断请求寄存器(PIRQR0)

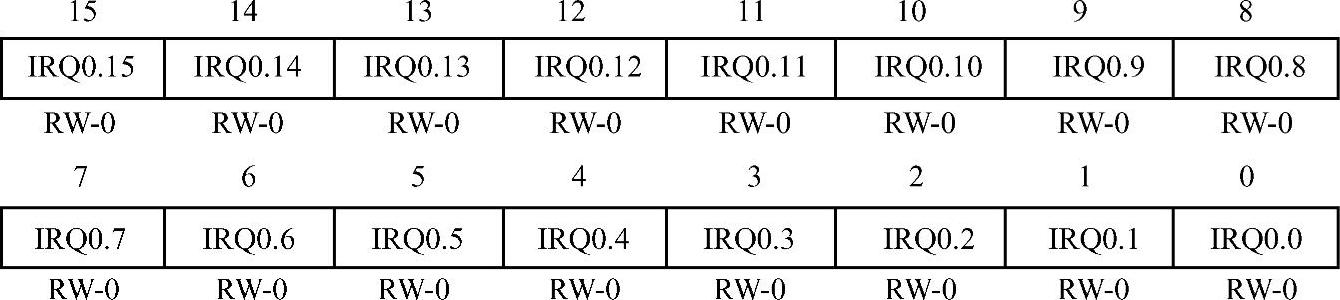

外设中断请求寄存器0(Periphera l Interrupt Re quest Register0,PIRQR0)映射在数据存储器空间中的地址为7010h,寄存器的格式如下:

位15~0外设请求标志位IRQ0.15~IRQ0.0。

●0:无相应外设的中断请求。

●1:相应外设的中断请求被挂起。

注:写入1会发出一个中断请求到DSP核,写入0无影响。该寄存器16个位所对应的外设见表2-13。

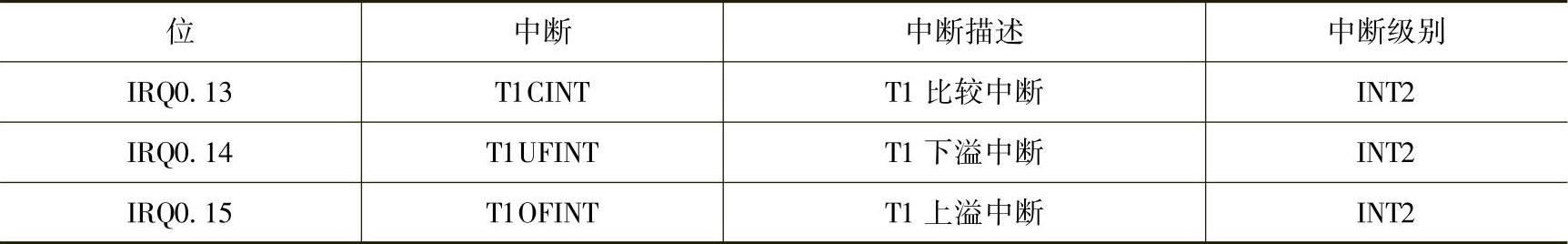

表2-13 外设中断请求寄存器0(PIRQR0)各位的定义

(https://www.xing528.com)

(https://www.xing528.com)

(续)

(3)外设中断请求寄存器(PIRQR1和PIRQR2)

二者与外设中断请求寄存器(PIRQR0)类似,不再详述。

(4)外设中断应答寄存器(PIACKR0)

其格式如下:

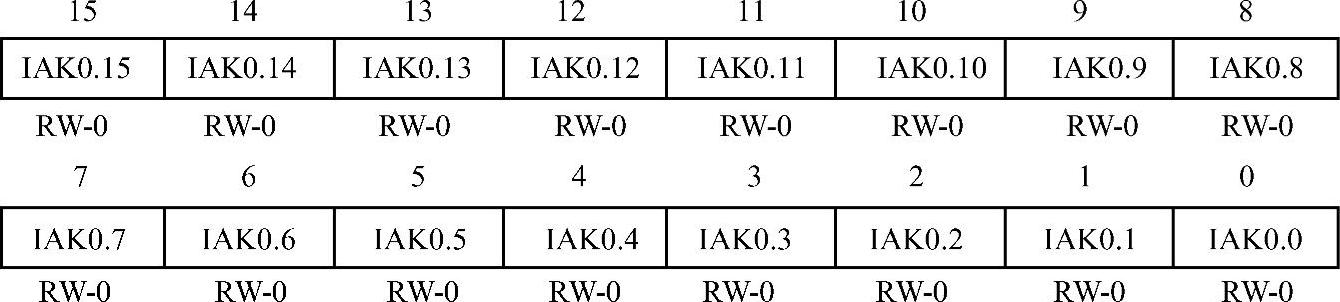

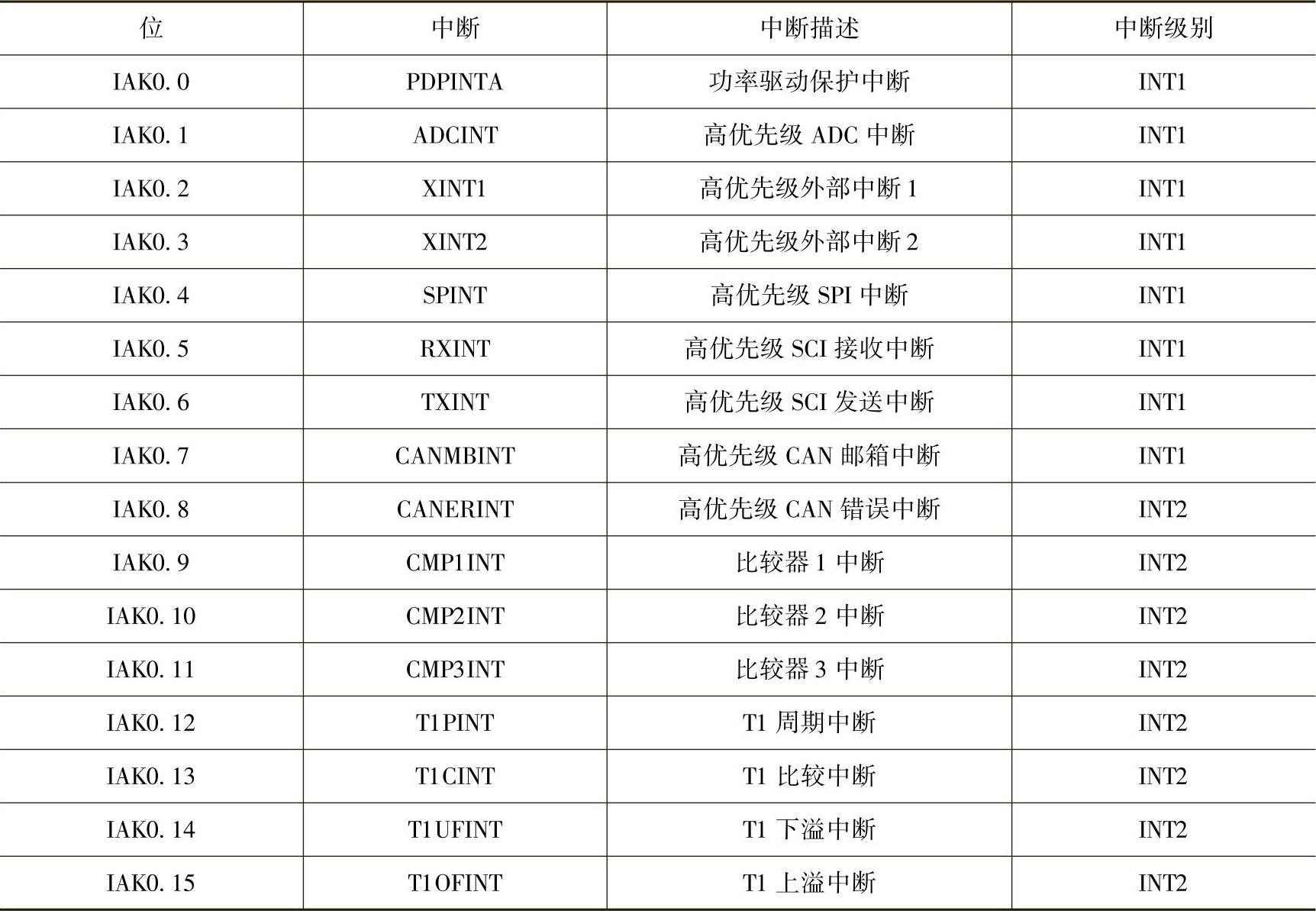

外设中断应答寄存器0(Periphera l Inte rrupt Acknowledge Register 0,PIACKR0)映射在数据存储器空间中的地址为7014h。该寄存器16个位(IAK0.15~0位)为中断应答位,对应的中断见表2-14。写1引起相应的中断应答被插入,从而将相应的中断请求位清零。

表2-14 外设中断应答寄存器0(PIACKR0)各位的定义

(5)外设中断应答寄存器(PIACKR1和PIACKR2)

二者与外设中断应答寄存器(PIACKR0)类似,不再详述。

3.外部中断控制寄存器

240x支持两个外部可屏蔽中断XINT1、XINT2。这两个外部中断引脚都可以选择上升沿或下降沿触发,也可以被使能或禁止。外部中断控制寄存器包括:外部中断1控制寄存器XINT1CR、外部中断2控制寄存器(XINT2CR)。

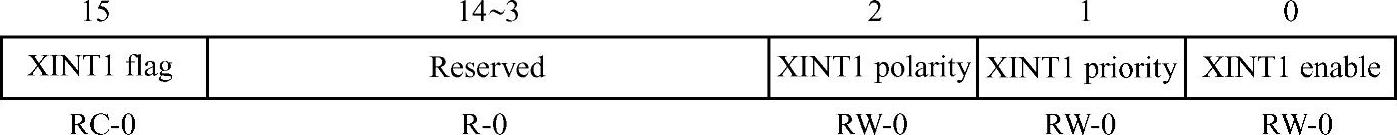

(1)外部中断1控制寄存器(XINT1CR)

其格式如下:

位15 XINT1 flag:XINT1标志位。在XINT1引脚上是否检测到一个所选择的中断跳变,无论中断是否使能,该位都可被置1。

●0:没有检测到跳变。

●1:检测到跳变。

位14~3保留位。

位2 XINT1 Polarity:极性位。写该位可决定引脚信号的上升沿或下降沿产生中断。

●0:下降沿(高到低跳变)产生中断。

●1:上升沿(低到高跳变)产生中断。

位1 XINT1 prio rity:XINT1优先级。读/写该位决定哪一个中断优先级被请求。

●0:高优先级。

●1:低优先级。

位0 XINT1 enable,使能位。

●0:禁止该中断。

●1:允许INT1中断。

(2)外部中断2控制寄存器XINT2CR

用法同外部中断1控制寄存器XINT1CR。

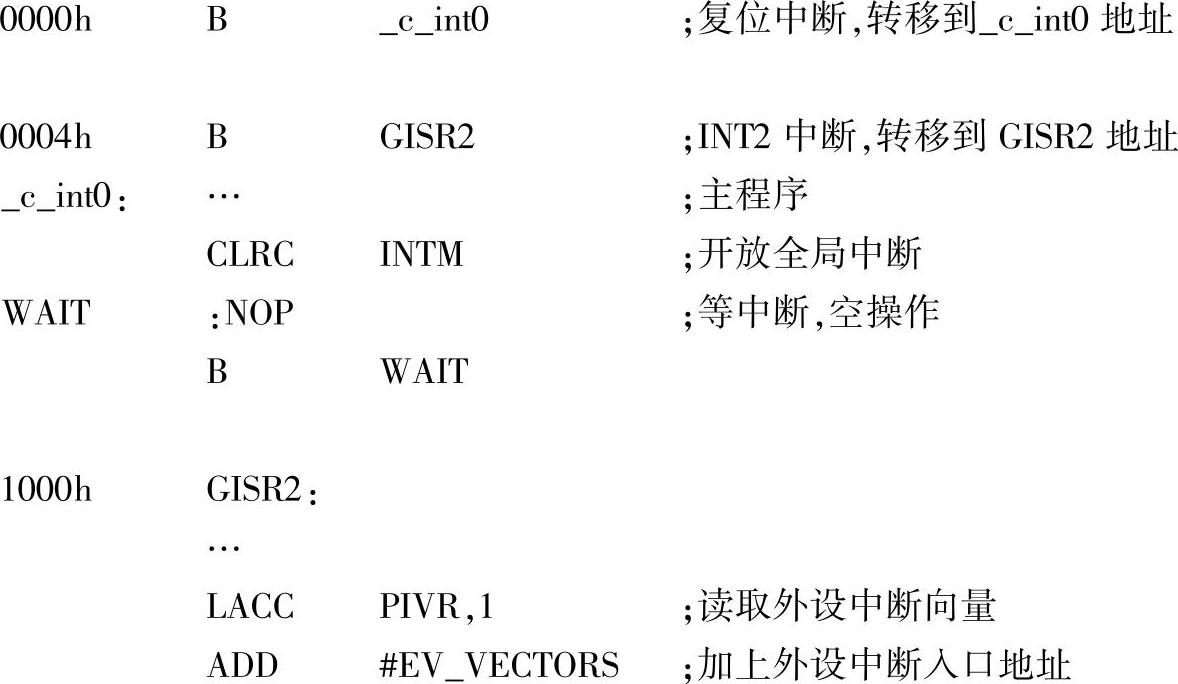

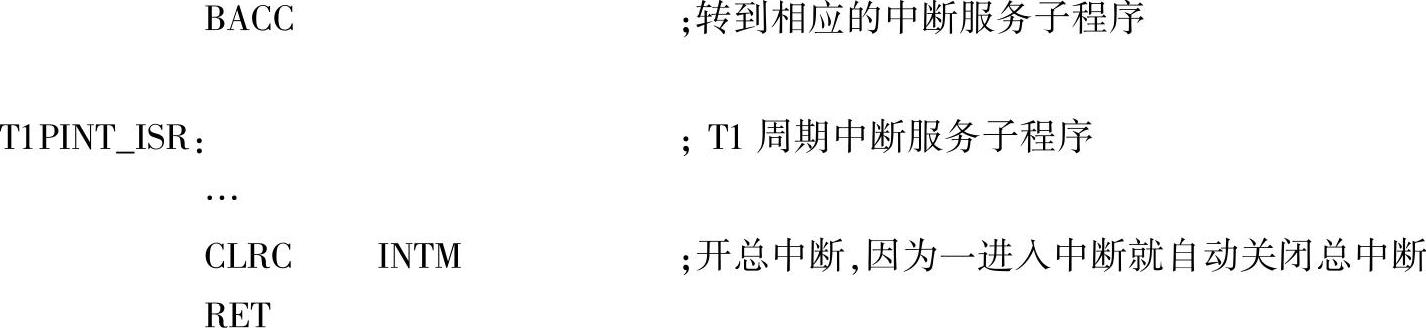

【例2-5】定时器T1周期中断汇编语言程序实例。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。