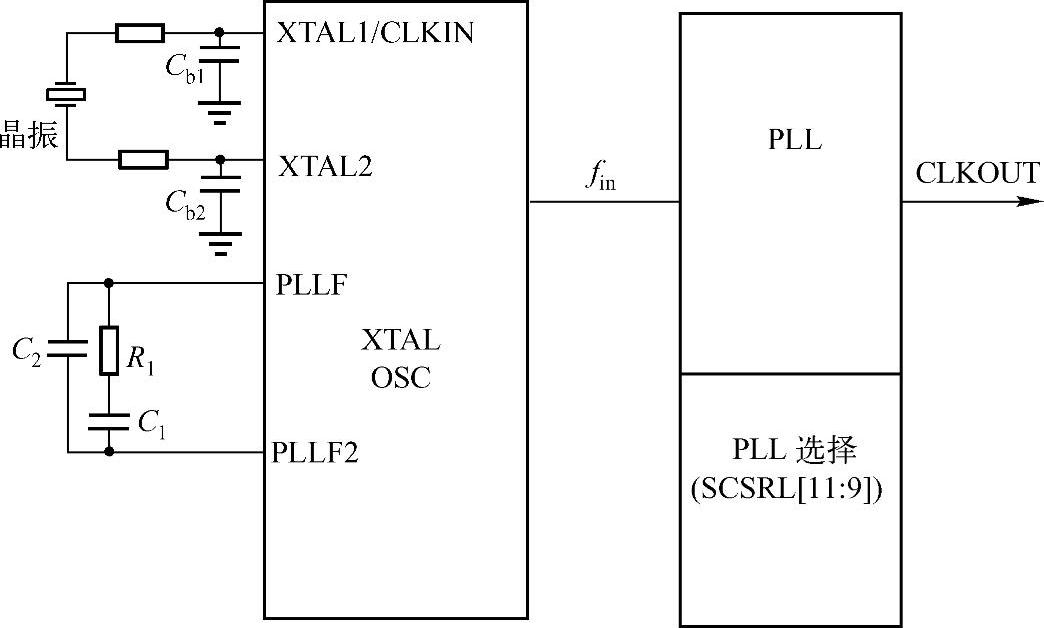

240x DSP片内集成有锁相环(Phase⁃lo cked Loop,PLL)电路。可从一个较低频率的外部时钟合成片内较高工作频率的时钟。

240x DSP有3个引脚与时钟模块有关:

1)XTAL1/CLKIN:外接基准晶体(Crystal)到片内振荡器的输入引脚。如使用外部振荡器,外部振荡器的输出必须接到该引脚。

2)XTAL2:片内PLL振荡器驱动外部晶振的时钟输出引脚。

3)CLKOUT/IOPE0:时钟输出或通用I/O引脚。CLKOUT可用来输出CPU时钟或看门狗定时器时钟,这由系统控制和状态寄存器1(SCS R1)中的位14(CLKSRC)决定。当该引脚不用于时钟输出时,可以作为通用输入/输出引脚IOPE0。复位时,该引脚的功能配置为时钟输出CLKOUT。

片内的锁相环(PLL)模块为片内所有功能模块提供必要的时钟信号,而且PLL还可以控制低功耗操作。

PLL支持对输入时钟频率的0.5~4倍频,以得到CPU工作频率,倍率值由系统控制和状态寄存器1(SCSR1)的位11~9来决定。

1.锁相环的时钟模块电路

锁相环的时钟模块电路如图2-8所示。

图2-8 锁相环的时钟模块电路

240x有两种时钟工作模式:

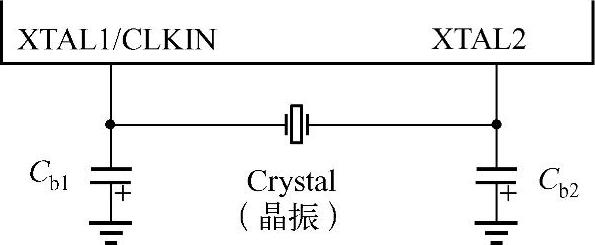

1)内部振荡电路外部晶振的工作方式。该模式下,外部无源晶振连接到DSP的XTAL1/CLKIN和XTAL2引脚,如图2-9所示。DSP的振荡电路和无源晶振一起运行产生时钟,提供给DSP作为时间基准。通常两个对地连接的电容可以取20~30 pF。

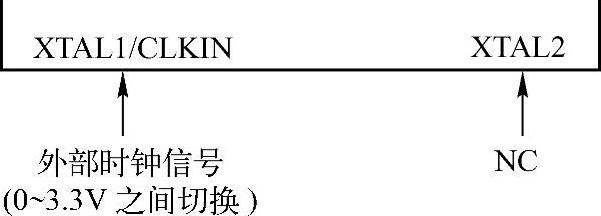

2)外部时钟工作方式。该模式下,不使用内部振荡器,即采用外部有源晶振,DSP的时钟来自XTAL1/CLKIN引脚的外部时钟信号,XTAL2引脚悬空(NC),如图2-10所示。

图2-9 内部振荡电路外部晶振的连接

图2-10 外部有源晶振的连接

2.外部滤波器电路(https://www.xing528.com)

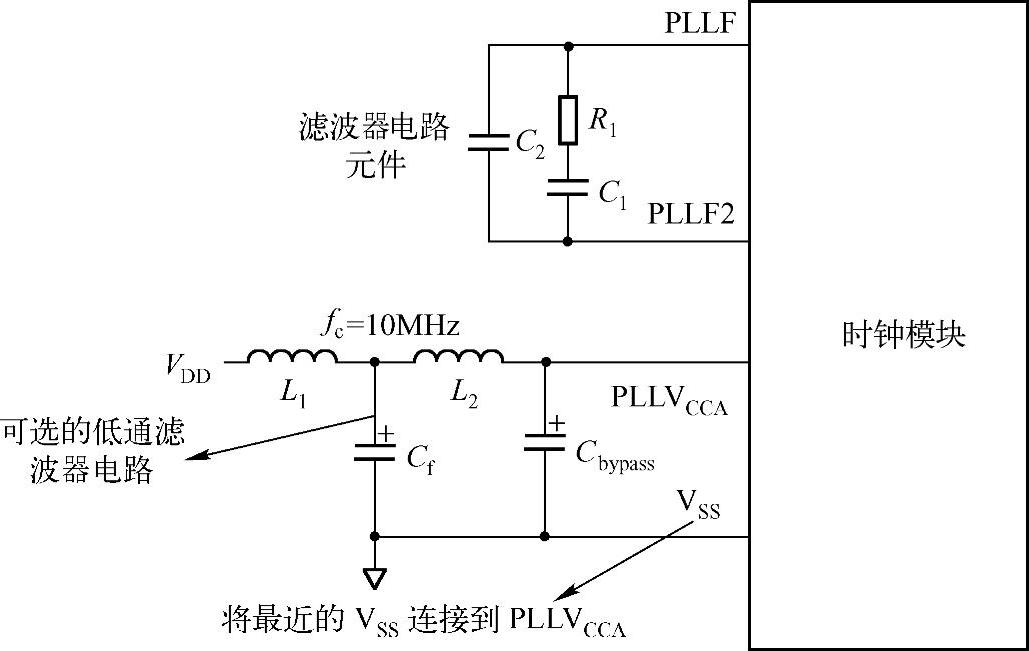

PLL模块使用外部滤波器电路来抑制信号抖动和电磁干扰,使信号抖动和干扰影响最小。通常电路中存在大量的噪声,在设计电路时,为提高滤波效果还需要通过实验来确定电路元件参数。滤波器电路的元件为R1、C1和C2,电容C1和C2必须是无极性的。滤波器电路连接到240x DSP芯片的PLLF和PLLF2引脚,如图2-11所示。

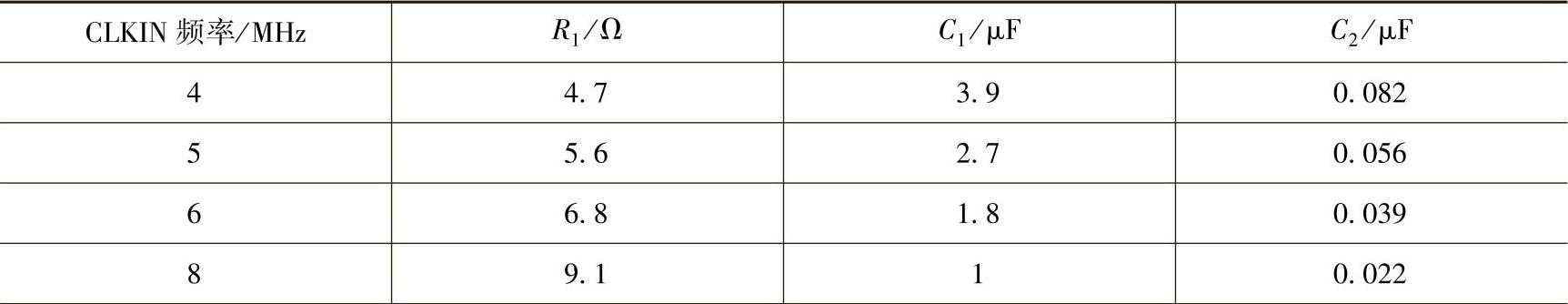

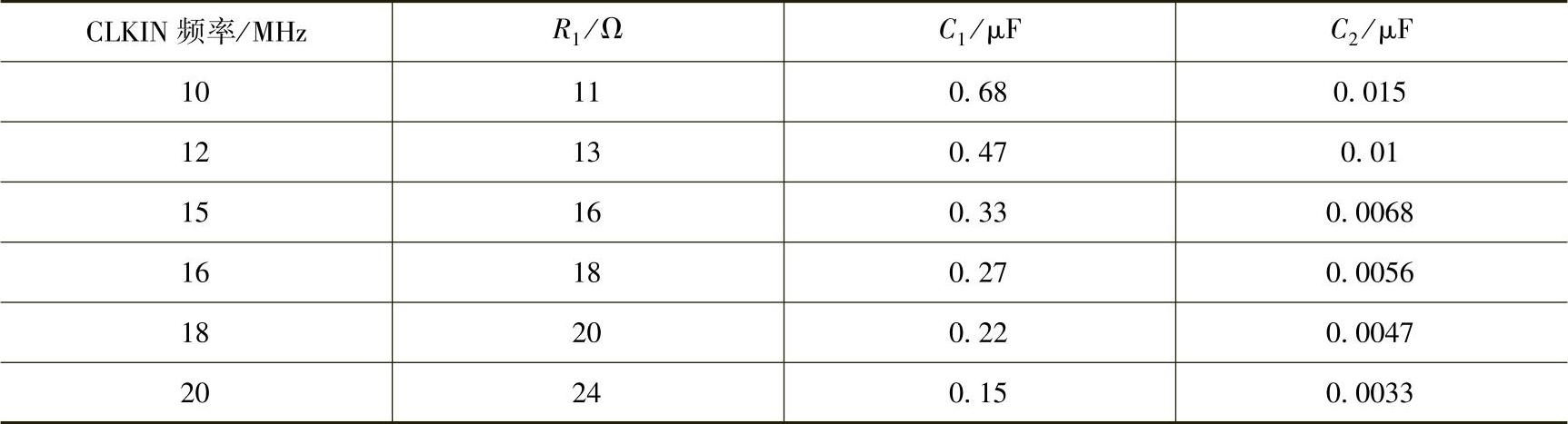

在不同振荡器(XTAL1)频率下具有阻尼系数2.0的R1、C1和C2推荐参数见表2-6。

表2-6 具有阻尼系数2.0的滤波元件推荐参数

(续)

图2-11 可选的滤波电路

所有连接PLL的印制电路板(PCB)导线必须尽可能短。一个旁路电容(0.01pF~0.1μF的陶瓷电容)应该连接在PLLVCCA和VSS引脚之间,如图2-11所示在PLLVCCA和VSS引脚之间增加了一个可选的低通滤波电路。

当连接PLL引脚时,应注意以下几个方面:

1)使用短引线连接PLLVCCA引脚到低通滤波器。10MHz的截断滤波器不是必需的,但是可以消弱信号的抖动,并减少电磁干扰。

2)使导线尽可能短,保证Cbypass(0.01 pF~0.1 μF的陶瓷电容)最近连接于PLLVCCA和VSS之间。

3)使导线、芯片和旁路电容形成的环路面积最小。面积越大,则电磁干扰越大。要避免附近具有噪声的导线连接到时钟模块的引脚上。

3.PLL旁路方式

通过复位时拉低TRST、TMS和TMS2引脚,可以实现将240x设置为对片内PLL旁路的工作方式。在这种方式下,可以实现PLL旁路,改变系统控制和状态寄存器SCSR1的位11~9无效。此时改变系统时钟的唯一方法是改变输入时钟频率,系统的时钟与外输入时钟相同。例如,要获得一个30 MHz的CPU时钟速度,那么必须提供一个30 MHz输入时钟CLKIN。在这种方式下,外部的滤波器元件是不需要的。

PLL旁路方式下的时钟规范如下:

1)使用内部时钟方式,那么最小和最大的CLKIN频率分别为4 MHz和20 MHz。

2)使用外部时钟方式,那么最小和最大的CLKIN频率分别为4 MHz和40 MHz。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。