分析一个时序逻辑电路,就是根据已知的时序电路,找出其实现的逻辑功能。具体地说就是要求找出电路的状态Q和输出信号Y在输入信号X和时钟信号CP作用下的变化规律。分析时序电路的一般步骤如下。

(1)由逻辑图写出下列各逻辑方程式:

➢各触发器的时钟方程(N步时序电路可不写)。

➢时序电路的输出方程(没有输出信号时不写)。

➢各触发器的驱动方程(即触发器的输入信号表达式)。

(2)将驱动方程代入相应触发器的特性方程,求出触发器的状态方程(次态![]() 的方程)。

的方程)。

(3)列状态表。根据状态方程和输出方程,对应输入X及现态![]() 的所有取值组合求出对应每个CP脉冲有效时的次态

的所有取值组合求出对应每个CP脉冲有效时的次态![]() 及输出值Y,列出状态表。

及输出值Y,列出状态表。

(4)根据状态表画出状态图或时序图。

(5)根据状态表或状态图或时序图说明电路的逻辑功能。

这里通过如图5.2所示时序电路来进行逻辑功能的分析。

图5.2 JK触发器组成的时序电路逻辑图

分析电路组成:该电路由两个JK触发器构成存储电路部分,由一个与门和一个异或门构成组合电路部分,外加输入信号X,输出信号为Y,是一个同步时序电路。(https://www.xing528.com)

驱动方程:

![]()

输出方程:

![]()

求状态方程:将各触发器的驱动方程代入JK触发器的特性方程

![]()

得到各触发器的状态方程:

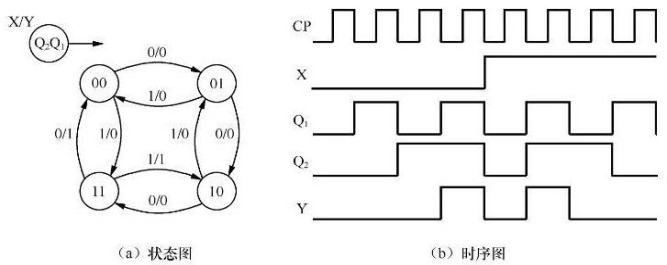

画出状态图和时序图如图5.3所示。

图5.3 状态图和时序图

状态转换图的画法:以圆圈表示电路的各个状态,以箭头表示状态转换的方向。同时,在箭头旁注明状态转换前的输入变量取值和输出值。通常将输入变量取值写在斜线上方,将输出值写在斜线下方。

在CP脉冲作用下,该电路在4个状态之间循环递增或递减变化,是一个同步四进制(二位二进制)可逆计数器,当X-0时进行加计数,当X=1时进行减计数,Y作为进位或借位输出。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。