【摘要】:在前面所介绍的用代数法和卡诺图法来化简逻辑函数,就是为了获得最简的形式,以便能用最少的门电路来组成逻辑电路。表3.2三人表决器真值表写出输出函数表达式并化简得:Y=AB+AC根据逻辑表达式可画出如图3.4所示的逻辑图。图3.4三人表决器逻辑图

1.组合逻辑电路设计的目的

组合逻辑电路的设计,通常以电路简单,所用器件最少为目标。在前面所介绍的用代数法和卡诺图法来化简逻辑函数,就是为了获得最简的形式,以便能用最少的门电路来组成逻辑电路。但是,由于在设计中普遍采用中、小规模集成电路(一片包括数个门至数十个门)产品,因此应根据具体情况,尽可能减少所用的器件数目和种类,这样可以使组装好的电路结构紧凑,达到工作可靠而且经济的目的。

2.设计组合逻辑电路的步骤

(1)根据设计题目要求,进行逻辑抽象,即将实际问题转化成逻辑问题。确定输入变量和输出变量及数目,明确输出变量和输入变量之间的逻辑关系,并对它们进行逻辑赋值即确定0和1代表的含义。

(2)根据功能要求将输出变量和输入变量之间的逻辑关系列成真值表。

(3)根据真值表写出逻辑函数,并将逻辑函数化简成最简表达式。

(4)根据最简表达式画逻辑图。

例:设计一个A、B、C三人表决电路。当表决某个提案时,多数人同意,提案通过,同时A具有否决权。用与非门实现。(https://www.xing528.com)

设计步骤:

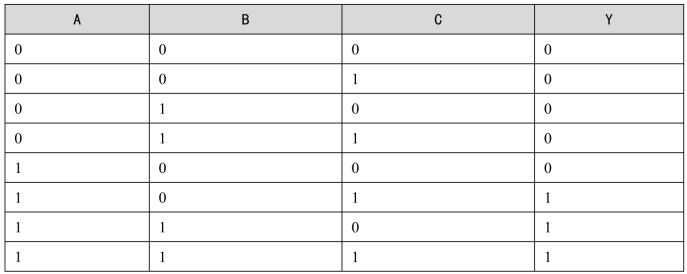

(1)列出真值表,如表3.2所示。设A、B、C三个人,表决同意用1表示,不同意时用0表示;Y为表决结果,提案通过用1表示,通不过用0表示;同时还应考虑A具有否决权。

表3.2 三人表决器真值表

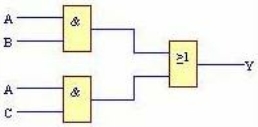

(2)写出输出函数表达式并化简得:Y=AB+AC

(3)根据逻辑表达式可画出如图3.4所示的逻辑图。

图3.4 三人表决器逻辑图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。