1.实验目的

1)数字时序逻辑电路综合应用。

2)学习扬声器的驱动方法。

3)学习CPLD/FPGA的层次化设计方法。

2.实验内容

设计一个小时、分钟可调并可在整点前报警的数字钟。

3.实验仪器

1)计算机(预装QuartusⅡ软件)。

2)EDA技术实验箱。

4.实验原理

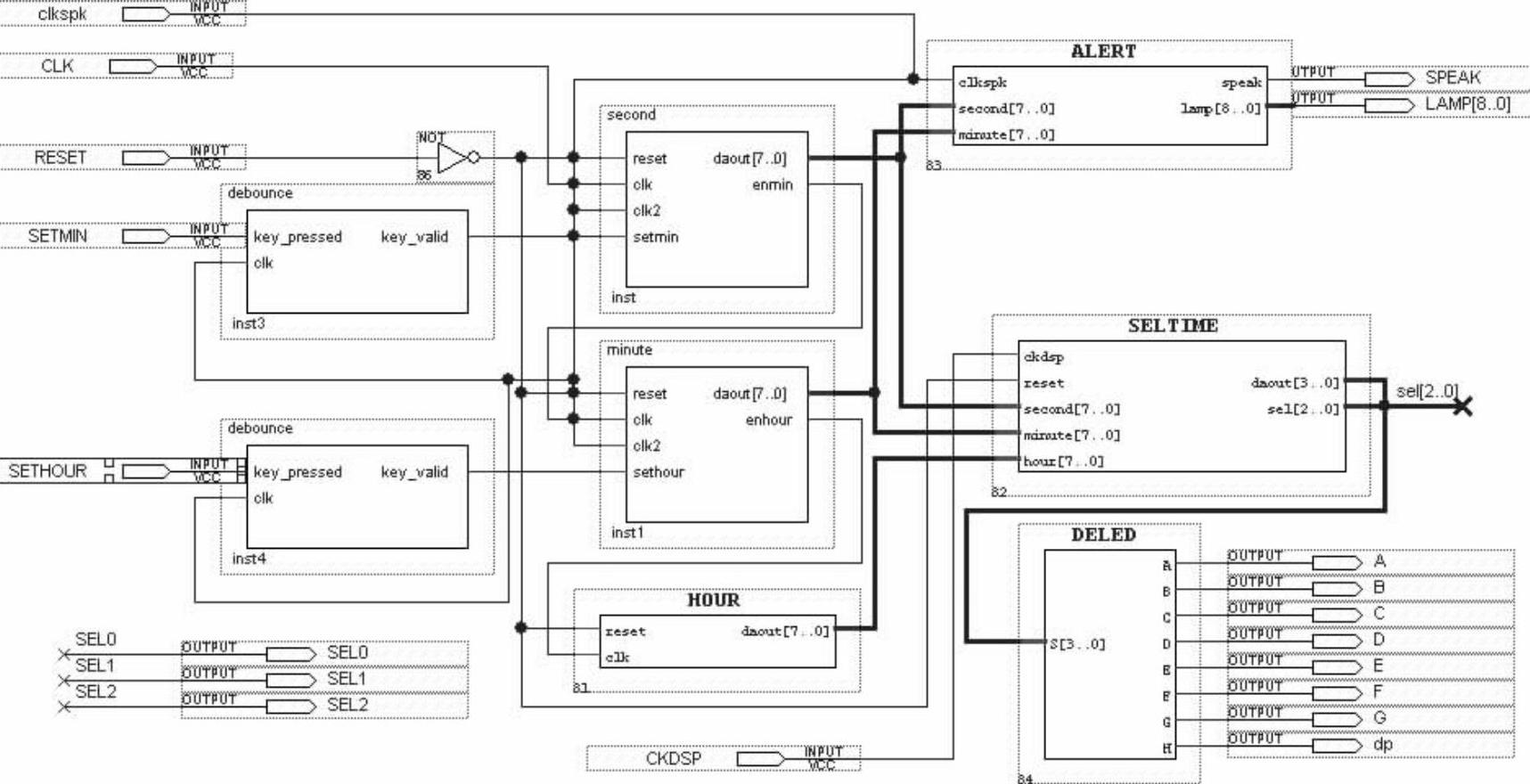

本实验的数字钟主要实现以下功能(该实验的顶层原理图见图6-60):

图6-60 数字钟电路顶层原理图

1)具有时、分、秒计数显示功能,以24h循环计时。其中,second模块为60进制BCD码计数电路,实现秒计时功能;minute模块为60进制BCD码计数电路,实现分计时功能;HOUR模块为24进制BCD码计数电路,实现小时计时功能。整个计数器具有清0、调分和调时的功能,而且在接近整点时间时能提供报时信号。其秒、分、时计数器的VHDL程序与元件符号分别如下:

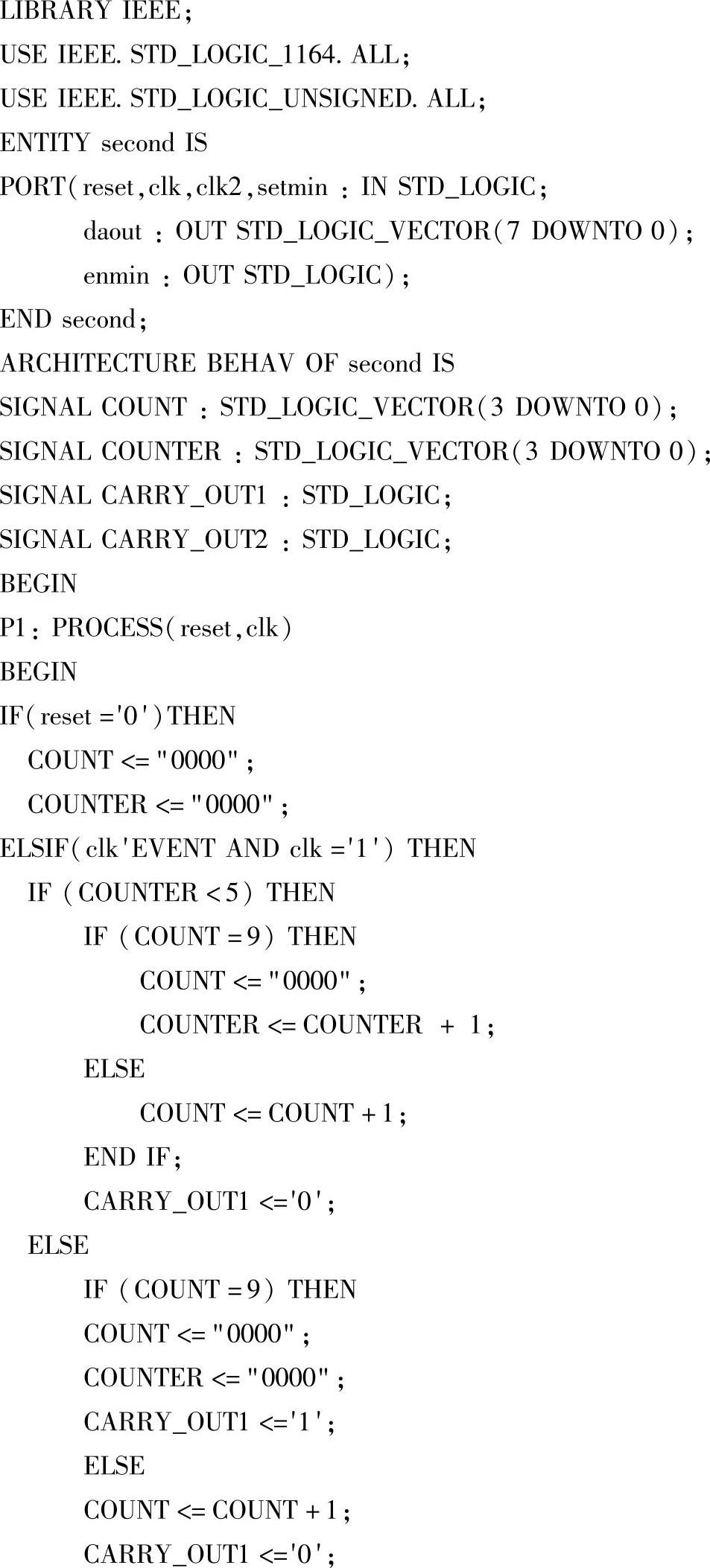

①秒计时器VHDL程序(如图6-61所示)。

图6-61 秒计时器元件符号

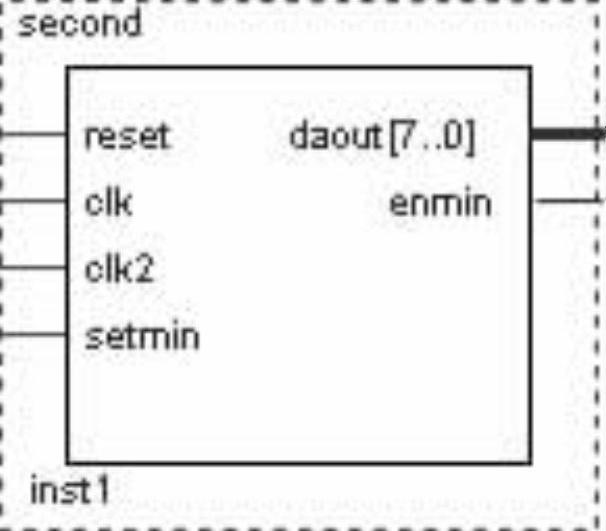

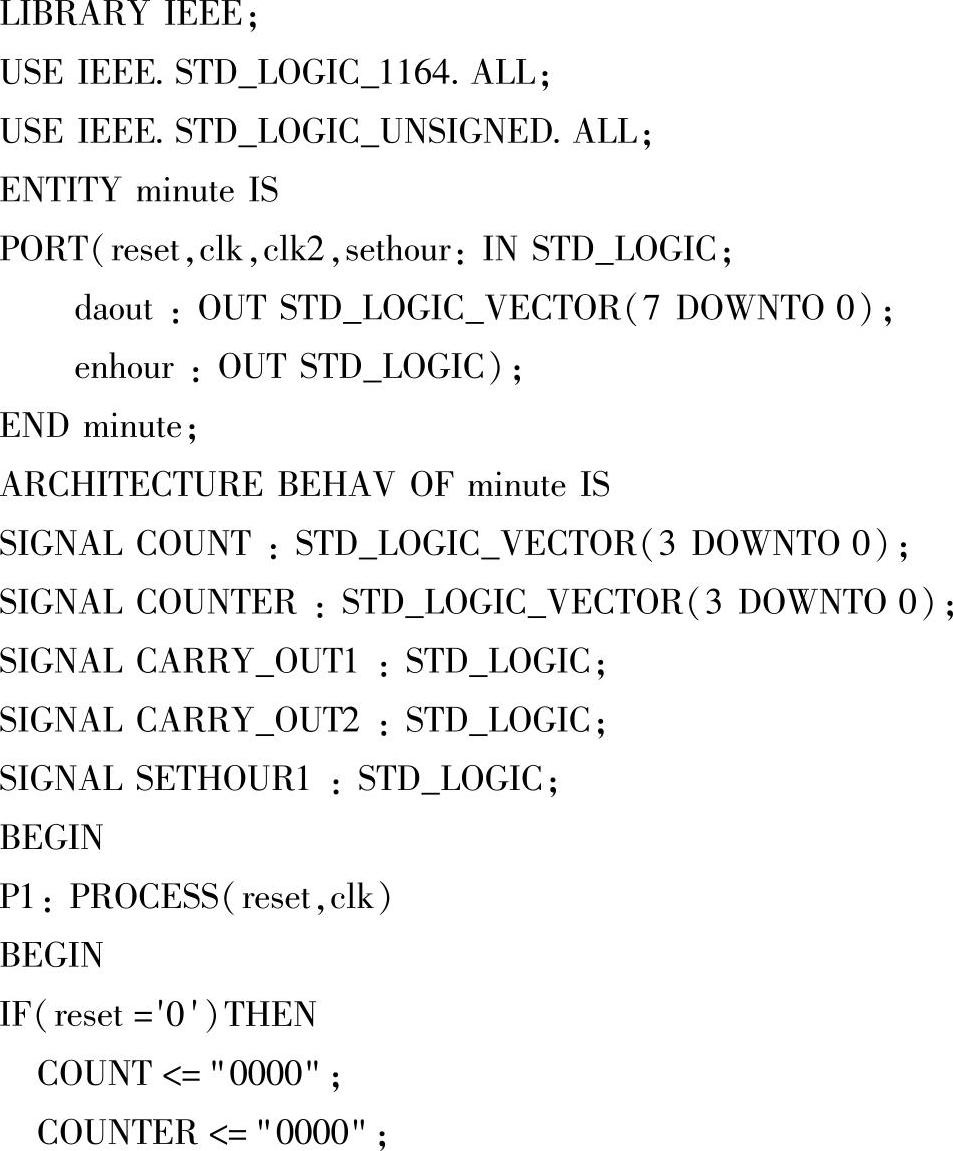

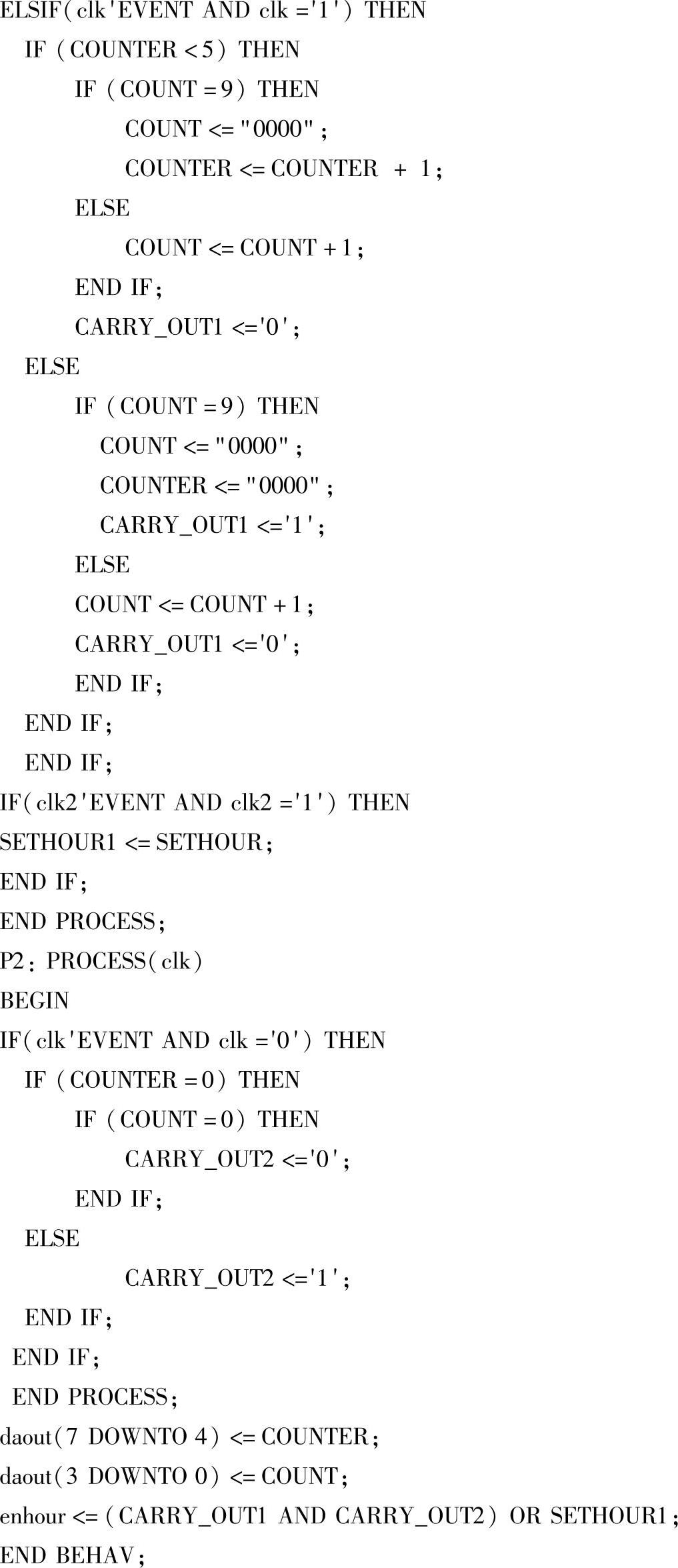

②分计时器VHDL程序(如图6-62所示)。

图6-62 分计时器元件符号

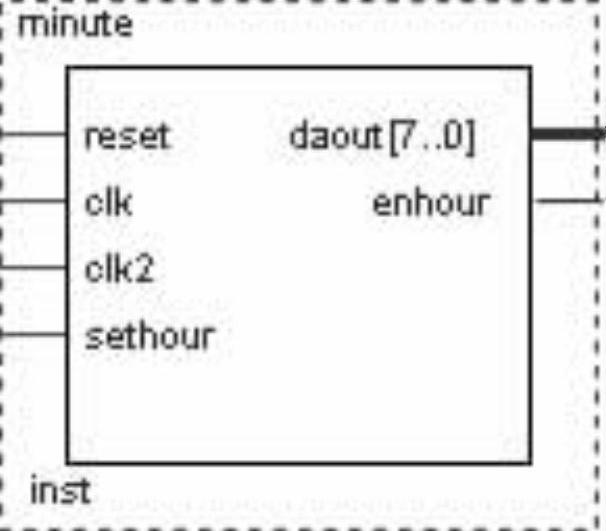

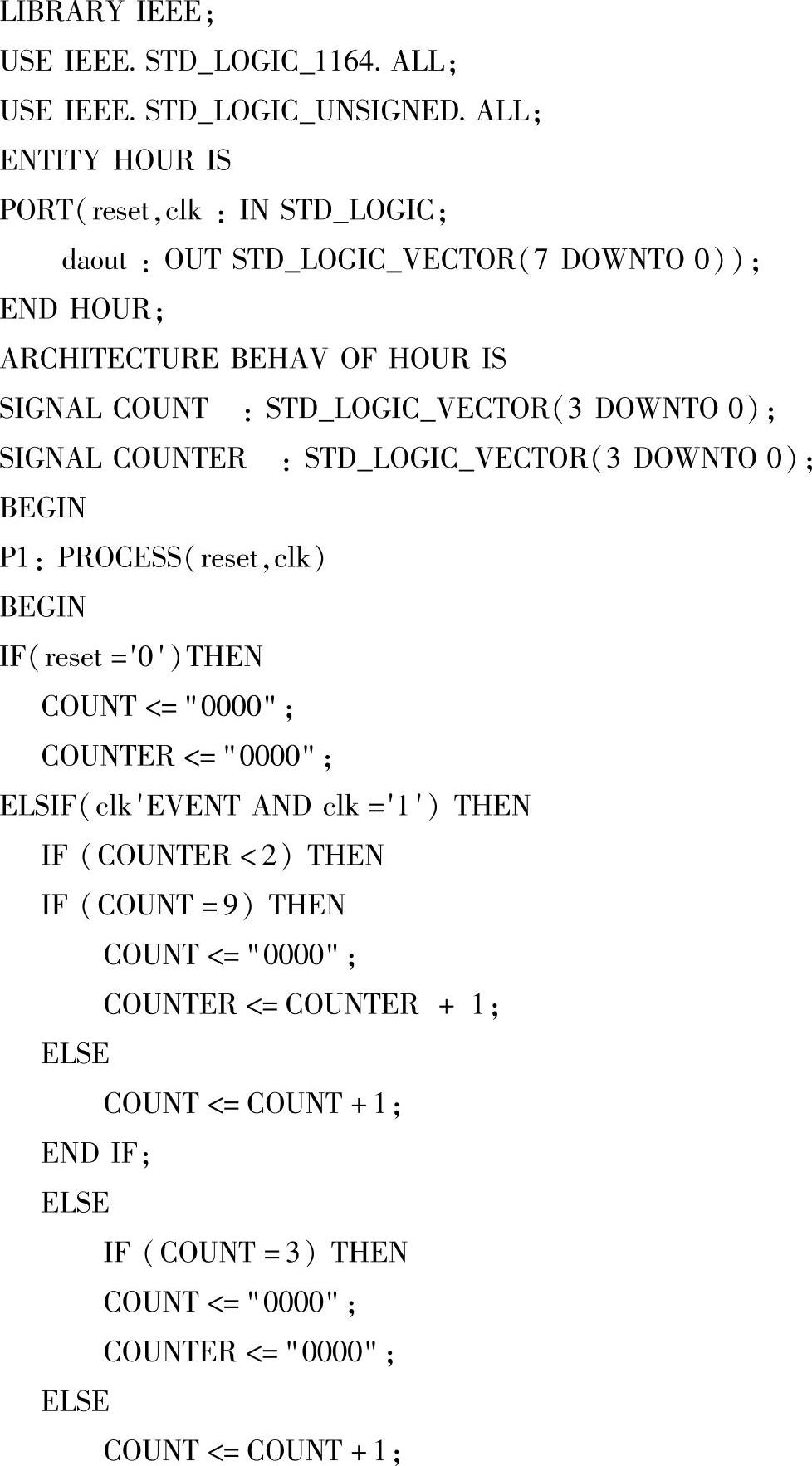

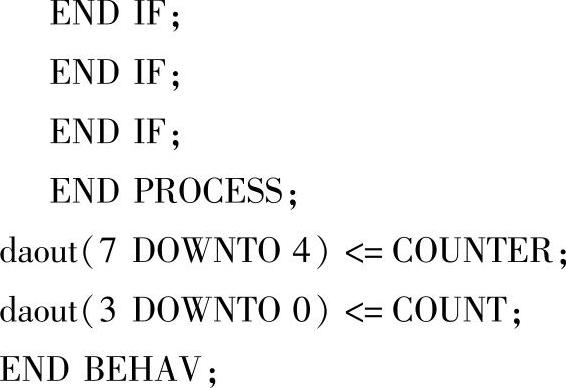

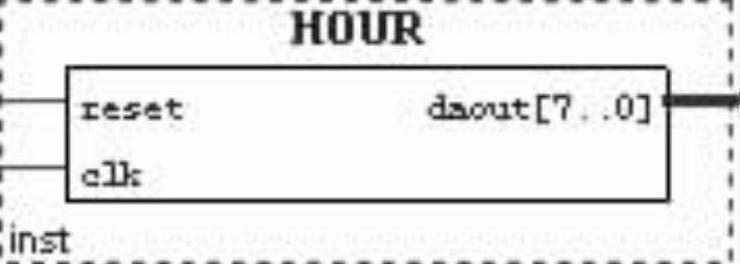

③时计时器VHDL程序(如图6-63所示)。

(https://www.xing528.com)

(https://www.xing528.com)

图6-63 时计时器元件符号

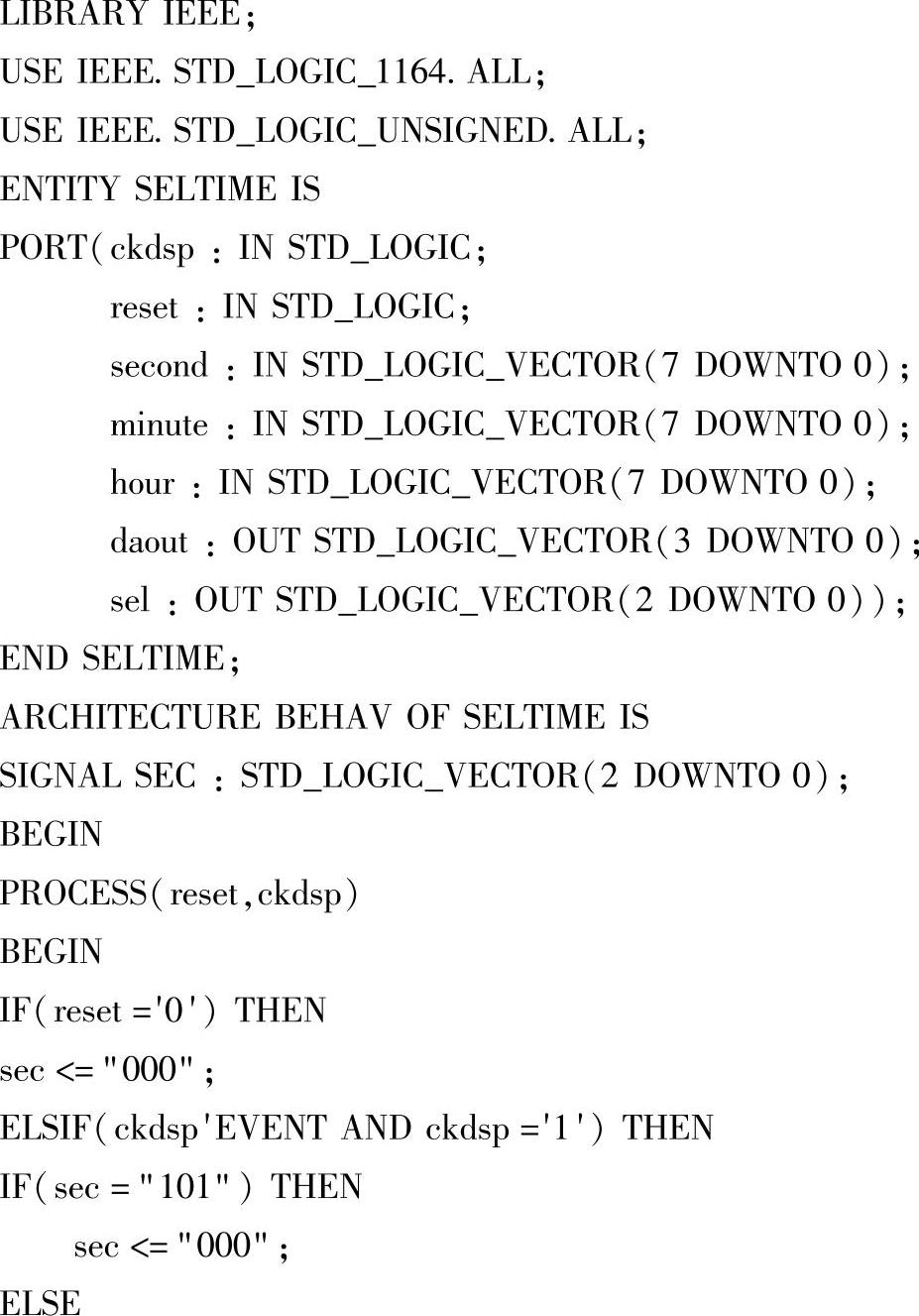

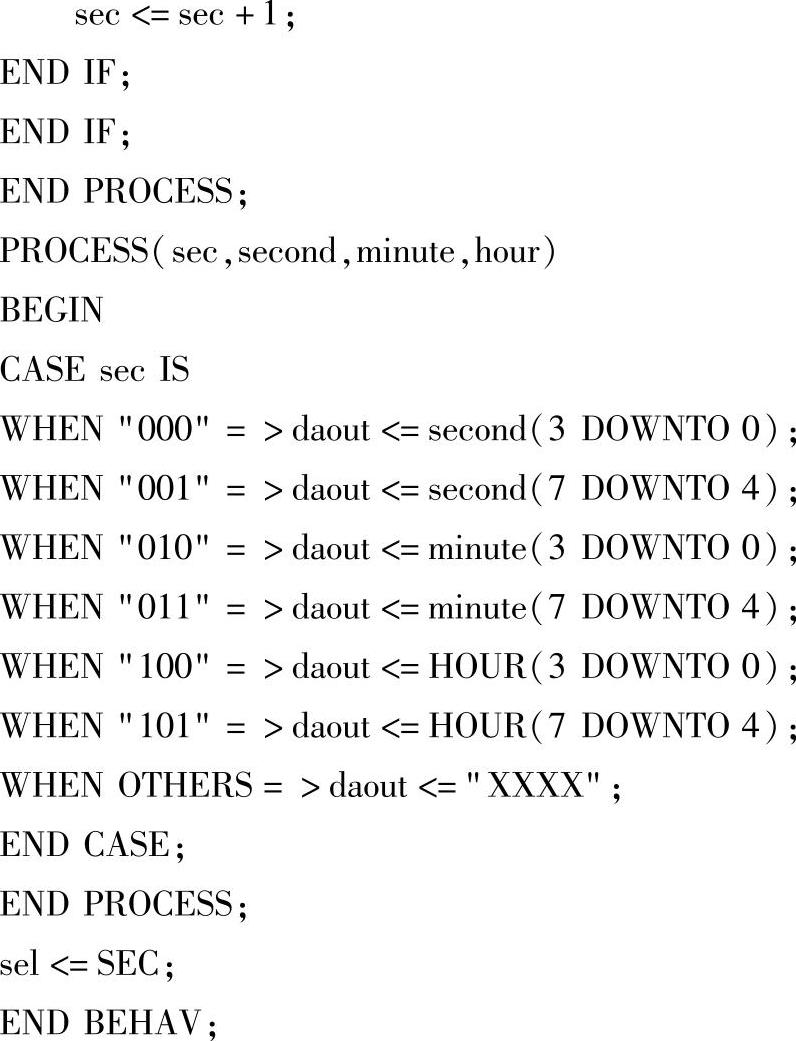

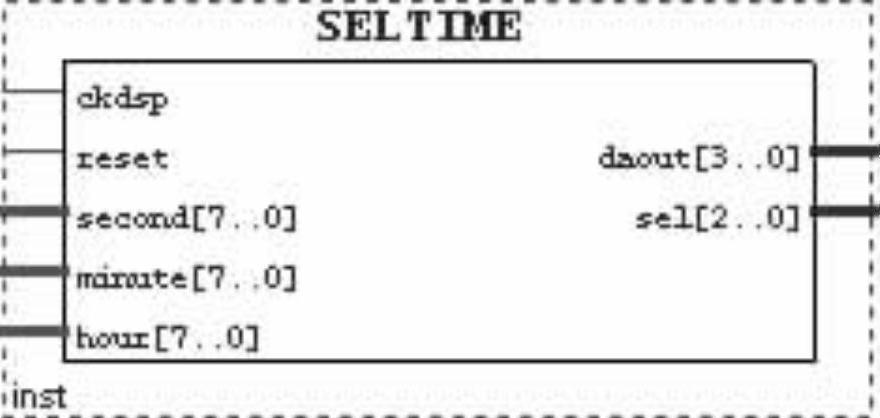

2)有驱动8位7段共阴极扫描数码管的片选驱动信号输出和7段码输出。在图6-60中,SELTIME模块产生8位数码管的扫描驱动信号sel[2..0]和时钟显示数据(动态显示)daout[3..0]。DELED模块则为数码管显示时钟数据的7段译码电路。其VHDL程序与元件符号分别如下:

①数码管扫描片选驱动VHDL程序(如图6-64所示)。

图6-64 数码管的扫描及片选驱动元件符号

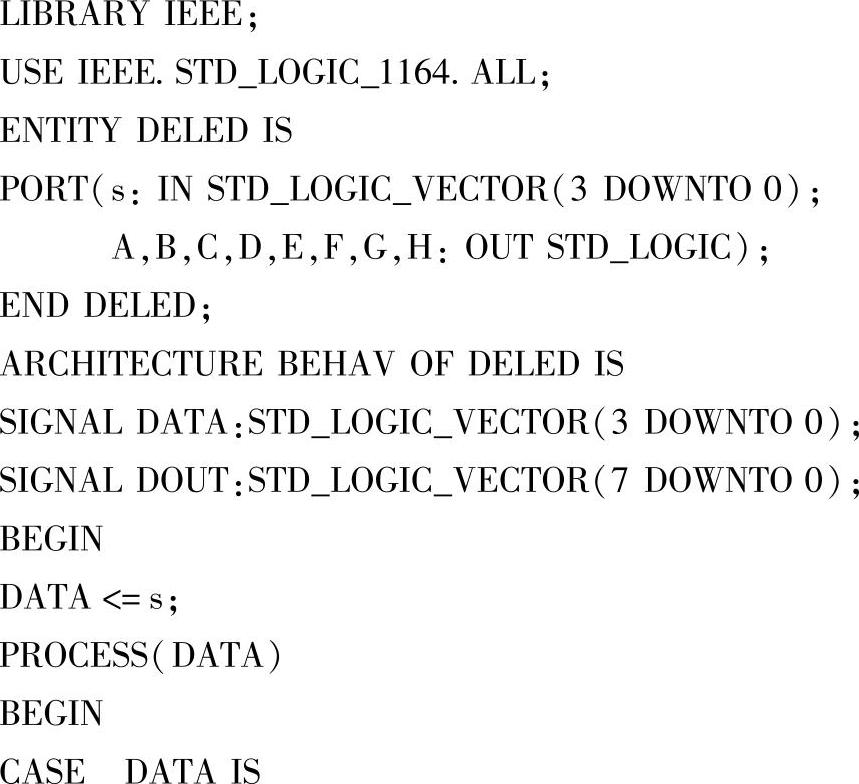

②7段译码电路VHDL程序(如图6-65所示)。

图6-65 7段译码电路元件符号

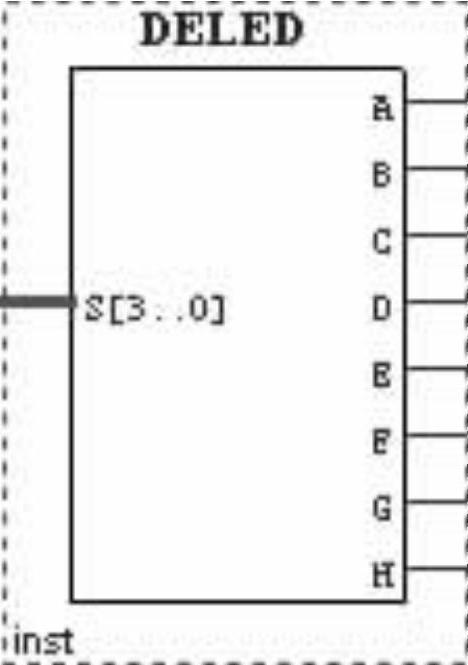

3)扬声器在整点时有报时驱动信号产生,以及LED灯根据设计的要求在整点时有花样显示信号产生。ALERT模块则产生整点报时的驱动信号speak和LED灯花样显示信号lamp[8..0]。在分位计数到59min时,秒位为51s、53s、55s、57s、59s时扬声器会发出1s左右的警告音,并且51s、53s、55s、57s为低音,59s为高音。其VHDL程序如下,元件符号如图6-66所示。

图6-66 整点报时驱动电路元件

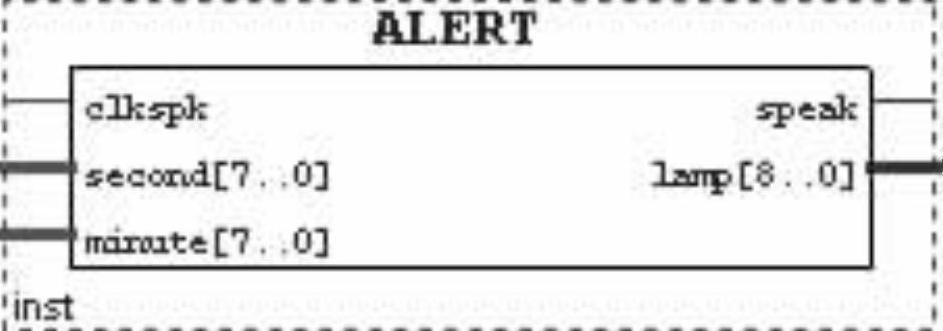

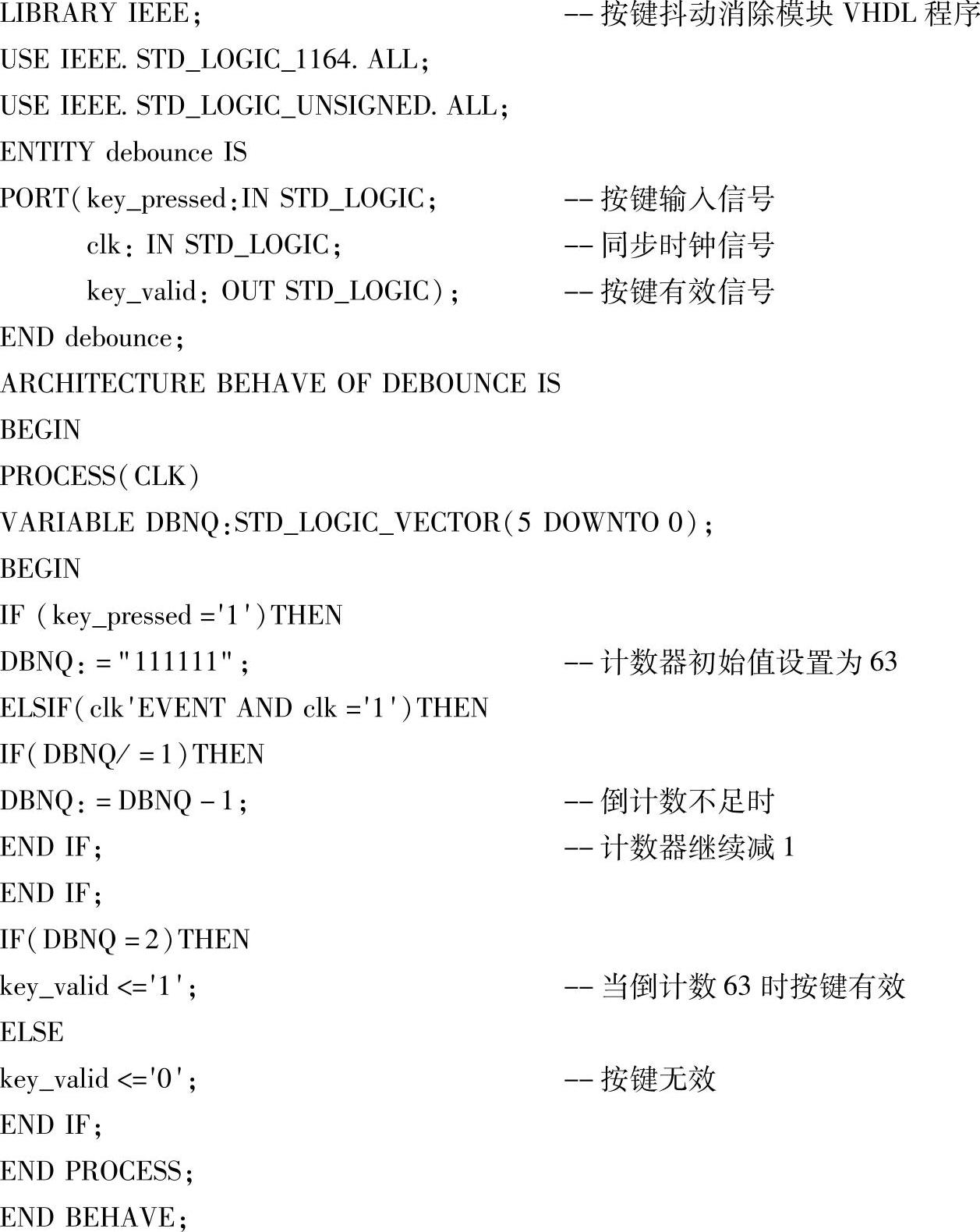

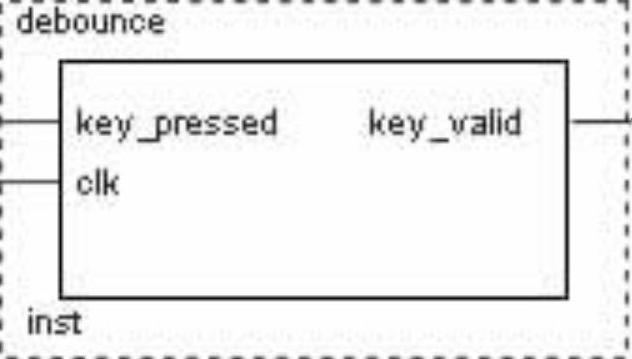

4)在second模块与minute模块之前加入了按键抖动消除模块debounce。抖动消除电路实际就是一个倒数计数器,主要目的是为了避免按键时键盘产生的按键抖动效应使按键输入信号(在程序中用key_pressed表示)产生不必要的抖动变化,而造成重复统计按键次数的结果。因此,只需将按键输入信号作为计数器的重置输入,使计数器只有在使用者按下按键时,且在输入信号等于‘0’时间足够长的一次使重置无动作,而计数器开始倒数计数,自然可将输入信号在短时间内变为‘0’的情况滤除掉。其VHDL程序如下,元件符号如图6-67所示。

图6-67 按键抖动消除模块元件符号

5.实验内容

1)在QuartusⅡ软件中新建原理图文件,输入自己设计的原理图,编译、仿真、锁定引脚并下载到目标芯片。

2)将第一全局时钟CLK1的跳线器接1Hz,第二全局时钟CLK2的跳线器接1024Hz,第三全局时钟CLK3的跳线器接32768Hz。拨位开关KD1为清0控制开关(高电平有效),KD2、KD3分别为小时调节、分钟调节允许端(低电平允许调节,高电平禁止调节/正常计时)。按键K2、K3分别为小时调节、分钟调节按键(仅当KD2、KD3为低电平允许调节时有效),只能加调节。数码管SM6~SM1分别显示小时,分钟,秒。当数字钟计时至××h59min51s时,扬声器开始鸣叫报时。其中,51s、53s、55s、57s为低音,59s为高音。LED1~LED9在51s~59s时依次闪烁。观察实验结果。

3)叙述所设计数字钟的工作原理,并画出整个电路的结构框图。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。