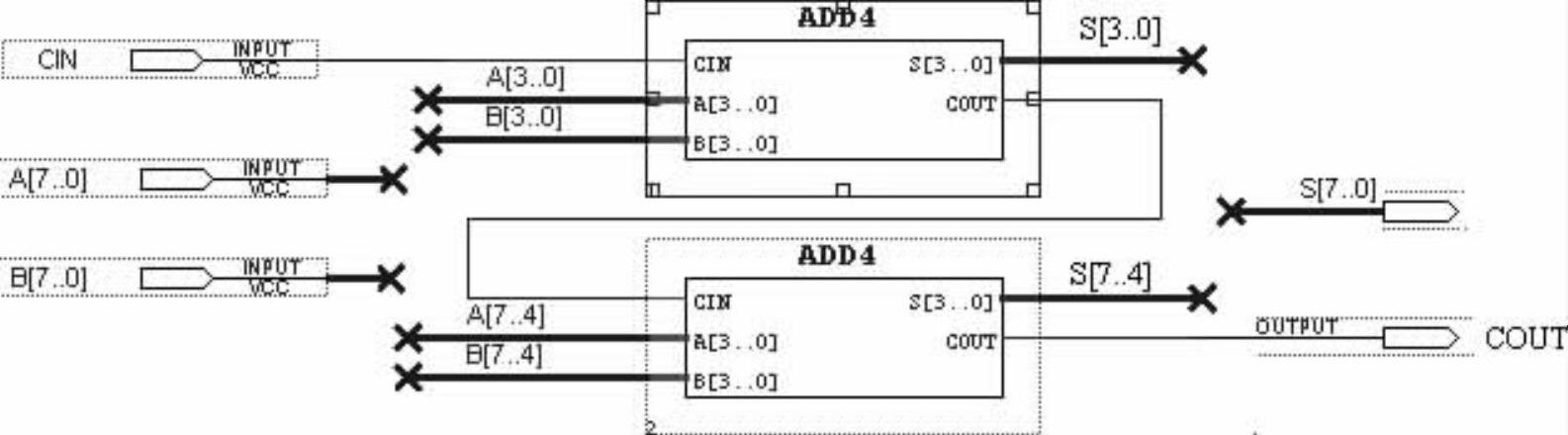

【摘要】:多位加法器的构成有两种方式:并行进位和串行进位方式。这样,多位数加法器由4位二进制并行加法器级联是较好的选择。图6-58 8位硬件加法器电路原理图4.实验内容1)在QuartusⅡ软件中,先建立8位硬件加法器的工程项目ADD8。

1.实验目的

1)学习硬件加法器的设计方法。

2)进一步熟悉层次化设计方法。

2.实验原理

加法器是数字系统中的基本逻辑器件。多位加法器的构成有两种方式:并行进位和串行进位方式。并行进位加法器设有并行进位产生逻辑,运算速度快;串行进位方式是将全加器级联构成多位加法器。并行进位加法器通常比串行进位加法器占用更多的资源,随着位数的增加,相同位数的并行加法器与串行加法器的资源占用差距快速增大。一般地,4位二进制并行加法器和串行级联加法器占用几乎相同的资源。这样,多位数加法器由4位二进制并行加法器级联是较好的选择。

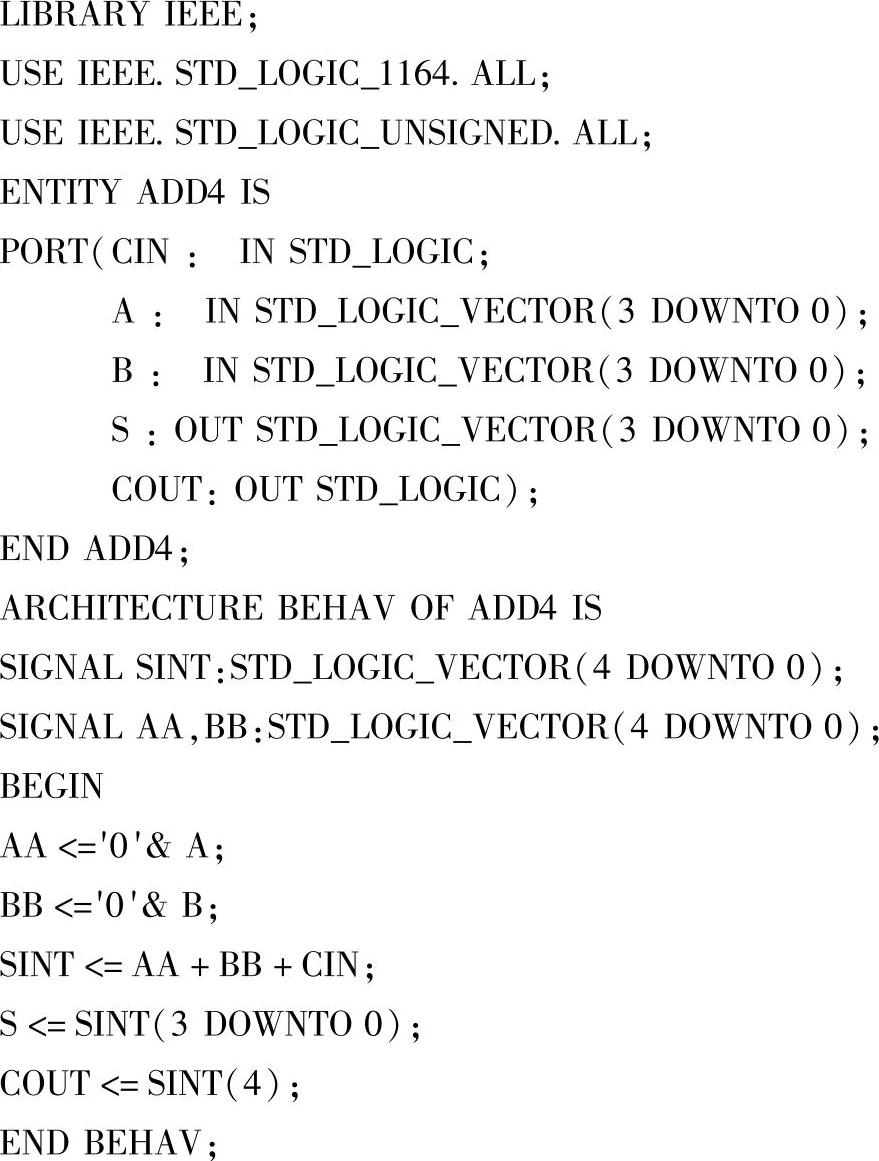

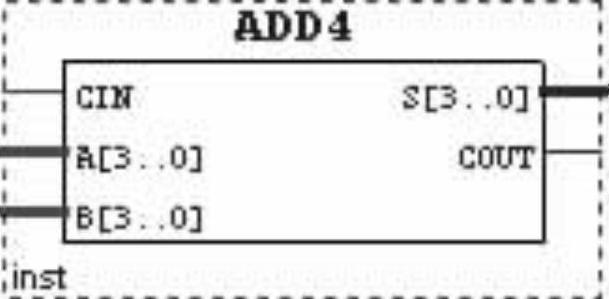

本实验的8位二进制加法器即是由两个4位二进制并行加法器级联而成,其元件符号如图6-57所示,顶层设计文件如图6-58所示,ADD4模块为4位二进制并行加法器,其VHDL程序如下:

图6-57 4位二进制并行加法器元件符号

3.实验仪器

1)计算机(预装QuartusⅡ软件)。

2)EDA技术实验箱。(https://www.xing528.com)

图6-58 8位硬件加法器电路原理图

4.实验内容

1)在QuartusⅡ软件中,先建立8位硬件加法器的工程项目ADD8。

2)利用文本输入方法设计4位二进制并行加法器ADD4.vhd,并生成元件符号。

3)利用层次化设计方法设计8位硬件加法器,如图6-58所示,并进行编译、仿真,然后根据实验箱的I/O分布进行引脚锁定、编程下载,最后进行硬件测试,验证设计电路的正确性。

5.实验报告

根据实验内容写出实验报告,包括VHDL程序设计、软件编译、仿真分析、引脚锁定情况、硬件测试和详细实验过程。

6.思考题

如何利用数码管显示输入的加数、被加数和输出的和?

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。