1.实验目的

时序逻辑电路的综合应用。

2.实验内容

根据实验原理,设计出2位十进制数字频率计。

3.实验仪器

1)计算机(预装QuartusⅡ软件)。

2)EDA技术实验箱。

4.实验原理

(1)功能划分

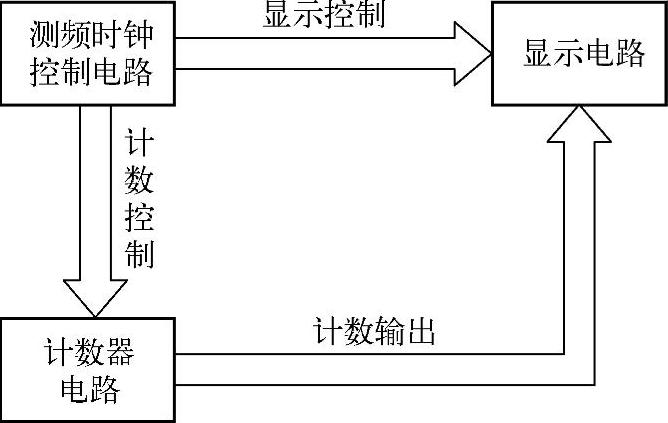

频率计的实现一般采用的方法是在1s的标准脉宽内对被测信号脉冲进行计数,计数结果即为所测频率。从原理上可将上述过程划分为3个功能模块,如图6-47所示。

测频控制电路负责产生测频控制时序,计数电路负责计数并锁存计数结果,显示电路负责将计数结果用静态或动态的方式在数码管上显示出来。

图6-47 频率计原理框图

(2)功能模块的实现

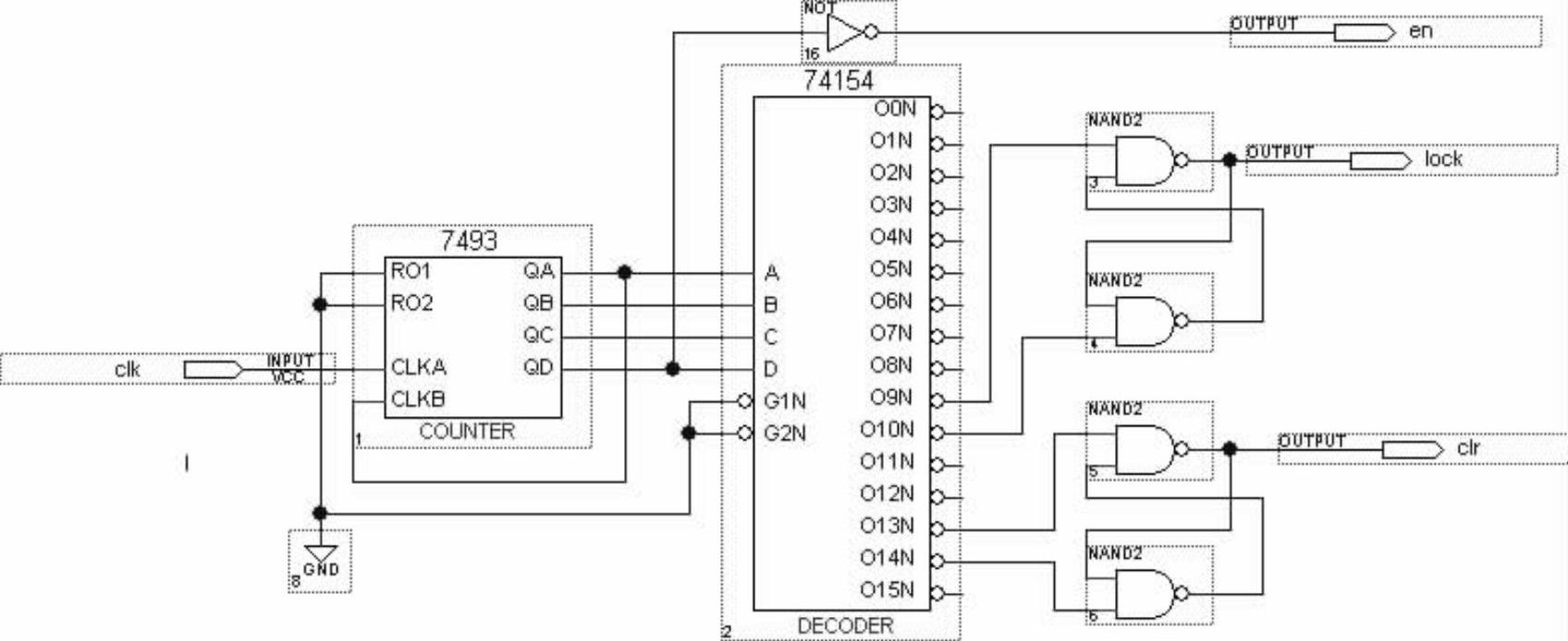

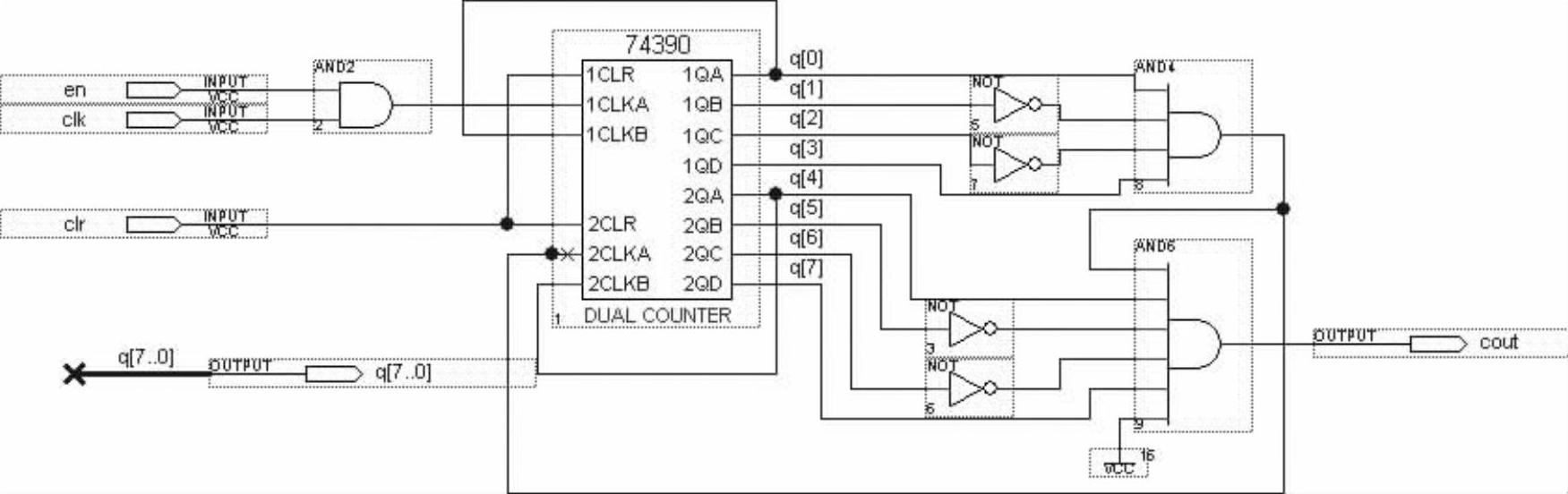

1)测频时序控制电路模块的实现。测频时序控制模块如图6-48所示,其顶层文件如图6-49所示。clk为8Hz基准输入时钟,en为计数器提供1s的标准脉宽,lock为锁存计数数据的控制信号,clr为计数器清0信号。图中采用了4位二进制计数器7493,4线-16线译码器74154和两个RS触发器。8Hz的基准时钟clk经过7493计数输出4位二进制数,QD为0.5Hz,刚好产生了1s的标准正负脉宽信号en。在1s的正脉宽时允许计数,在1s的负脉宽禁止计数。在允许计数期间进行计数。在禁止计数期间,进行计数结果的锁存,显示以及在下一个1s正脉冲到来之前计数器清0,准备新的计数测频等工作。这样就完成了自动测频的工作。

图6-48 测频时序控制模块图

图6-49 测频时序控制顶层图

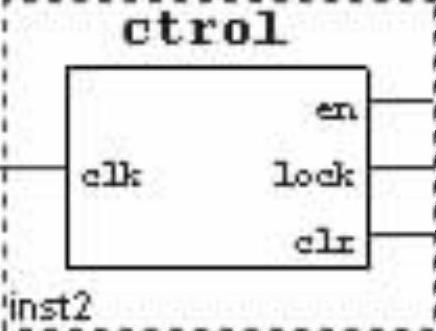

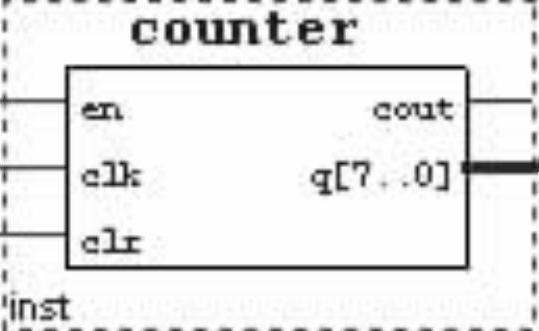

2)计数器电路模块的实现。将en和clk相与便可实现允许计数与禁止计数的控制。计数器功能模块如图6-50所示,其顶层图如图6-51所示。en为计数有效信号即为1s的标准脉宽,clk为待测输入频率,clr为计数器清0信号,Q[7..0]为2位BCD输出,cout为2位计数器进位信号。(https://www.xing528.com)

图6-50 计数器功能模块图

图6-51 计数器功能模块顶层图

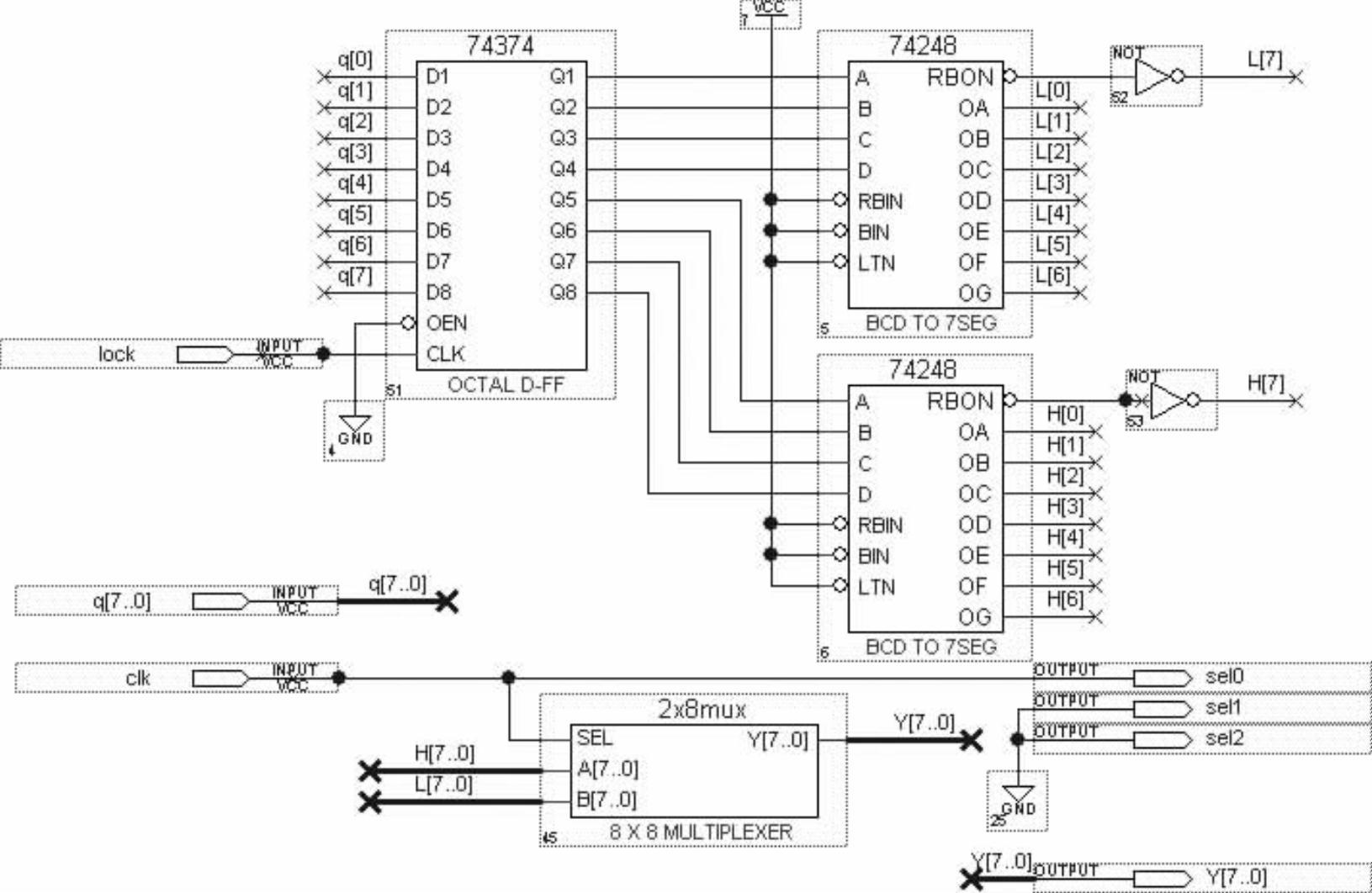

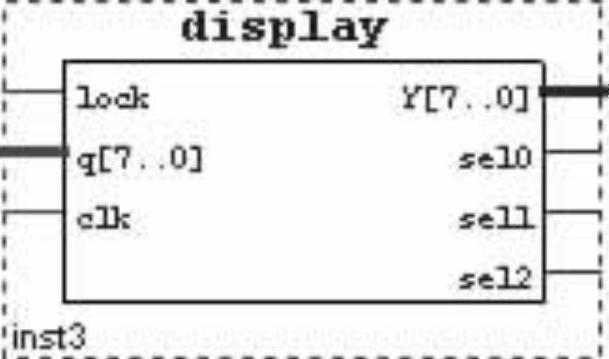

3)显示电路模块的实现。显示电路模块的设计可参考BCD-7段码译码器的设计。由于74248译码结果含有频率计中不应出现的0~9以外的字符,因此输入到显示模块的数据应为十进制的BCD码,这在计数器模块中完成。本模块的设计图如图6-52所示,其顶层文件实体如图6-53所示。

图6-52 显示电路模块图

8通道D触发器74374由lock控制锁存计数结果,输入计数结果为两个4位的BCD码,经过74248译为7段码送出,分为高位与低位共两位。在两路8位数据选择器选择后输出数码管位选信号(或称为数码管片选信号),位选输入时钟通常选用32768Hz。

图6-53 显示电路模块顶层图

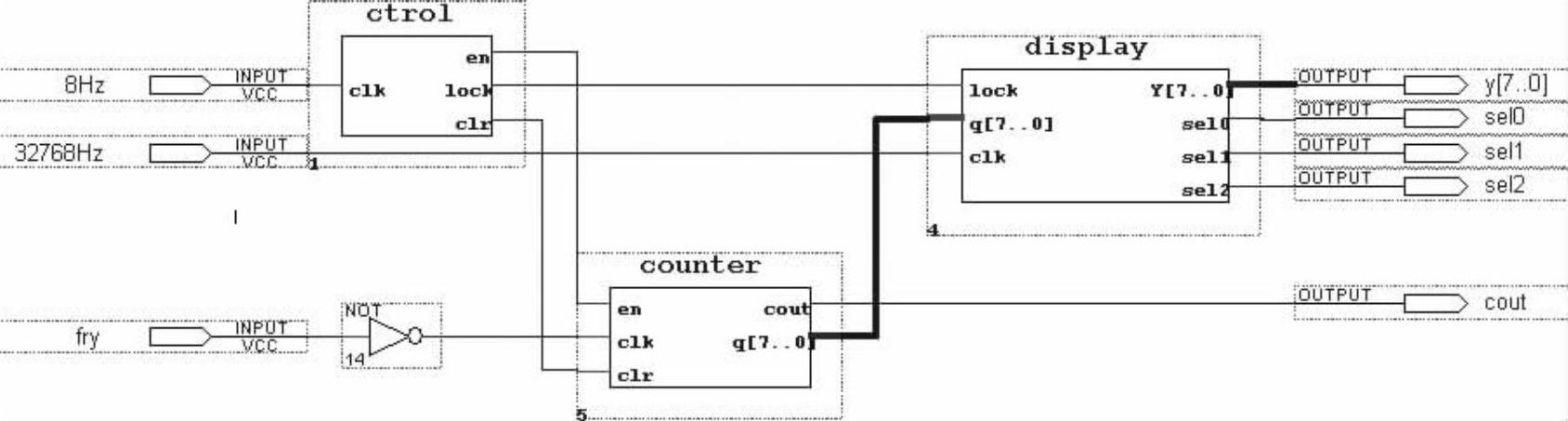

(3)总体实现

总体实现原理图如图6-54所示。8Hz是基准时钟,通过ctrol模块产生1Hz的en计数有效信号及计数锁存信号lock、计数清0信号clr。32768Hz是数码管显示扫描信号,可完成多位数码显示。fry是待测频率,cout满一百时的进位显示,可通过发光二极管显示,由于是自动测频,每隔1s测频一次,故进位显示是闪烁发光,当测量两位数以上的频率值时要认真观察。在2位频率范围(99Hz)内,输入不同的待测频率可以马上在数码管显示出测量值。有兴趣的读者不妨按上面的介绍设计出多位频率计。

图6-54 频率计总体实现原理图

5.实验步骤

1)在QuartusII软件中新建原理图文件,输入自己设计的原理图,编译、仿真、锁定引脚并下载到目标芯片。

2)将时钟源模块电源按钮TPW1按下。将第三全局时钟CLK3跳线器接8Hz,将第二全局时钟CLK2跳线器接32768Hz,第一全局时钟GCLK1作为待测频率,分别将跳线器接1Hz、2Hz、4Hz、8Hz、16Hz、32Hz、64Hz,观察数码管输出频率值。输入频率大于两位时,数码管只显示最低两位频率,如输入65536Hz时,显示36。进位信号LED1每秒闪烁1次。

注:ZY11EDA13BE型实验箱主板上的时钟源模块提供了丰富的时钟源,核心芯片的时钟分布情况如下表所示,以后各实验用到时钟源时,可按需要输入相应频率信号。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。