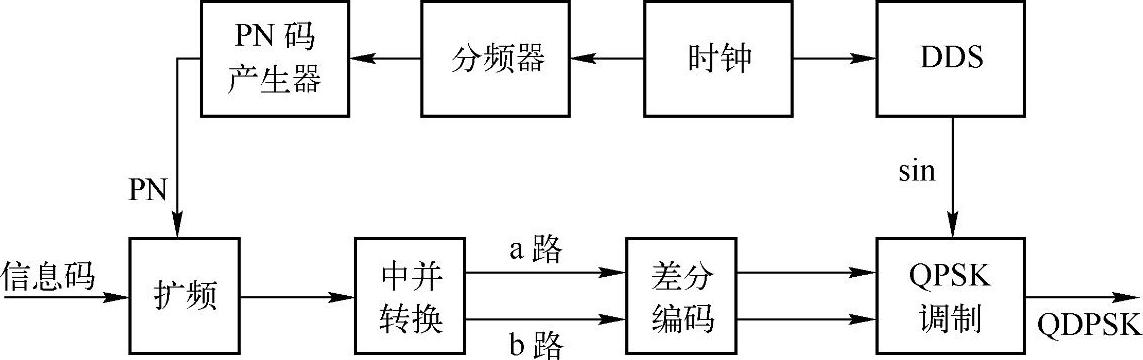

直接序列先利用伪随机码即PN码对信息码进行扩频处理,然后进行相应的QPSK数字调制。整个QPSK直接序列扩频组成如图5-44所示。

图5-44 QDPSK直扩调制器方框图

1.QPSK直接序列扩频调制器各模块的功能分析及主要参数

(1)系统的功能模块

①信息源:本文中的输入信号是5个硬件电路上的拨码开关,手工设置输入,循环发放速率为1kbit/s的信息码。

②PN码产生器:PN码产生器即m序列产生器,m序列的频率是31kHz。

③扩频:扩频是m序列与传输的1kbit/s二进制数据信息进行模2相加。

④并串转换:把串行的扩频后的31kHz信号转换为速率为15.5kHz的并行信号。

⑤差分编码:把经过串并转换后绝对码转换为相对码,用来防止产生相位模糊问题。

⑥分频器:该模块有3个分频器。第一个分频是系统时钟30.752MHz先进行32分频后输入给第二个分频,第二个分频是经过32分频后的信号接着进行31分频,分频后的信号作为m序列产生器的时钟信号,第三个分频是经32分频,31分频后的信号再次进行31分频后作为信息码元的速率。

⑦QPSK调制器:采用4种不同的载波相位来表示数字信息,每个载波相位代表2bit信息,4种不同的2bit信号选择DDS输出信号(载波信号)的初始相位,即实现了QPSK调。

⑧DDS:产生正弦信号用来调制。

⑨时钟:从外部引入的数字时钟信号30.752MHz。

(2)系统的主要参数

①整个系统的主时钟为30.752MHz。

②信息码的速率为1kbit/s,工作时钟为1kHz。

③PN码长为31位,速率为31kchips/s,工作频率为31kHz。

④DDS的工作时钟为30.752MHz,正弦载波频率为961kHz。

⑤QDPSK的输出频率为961kHz。

2.QPSK直接序列扩频调制器的设计与实现

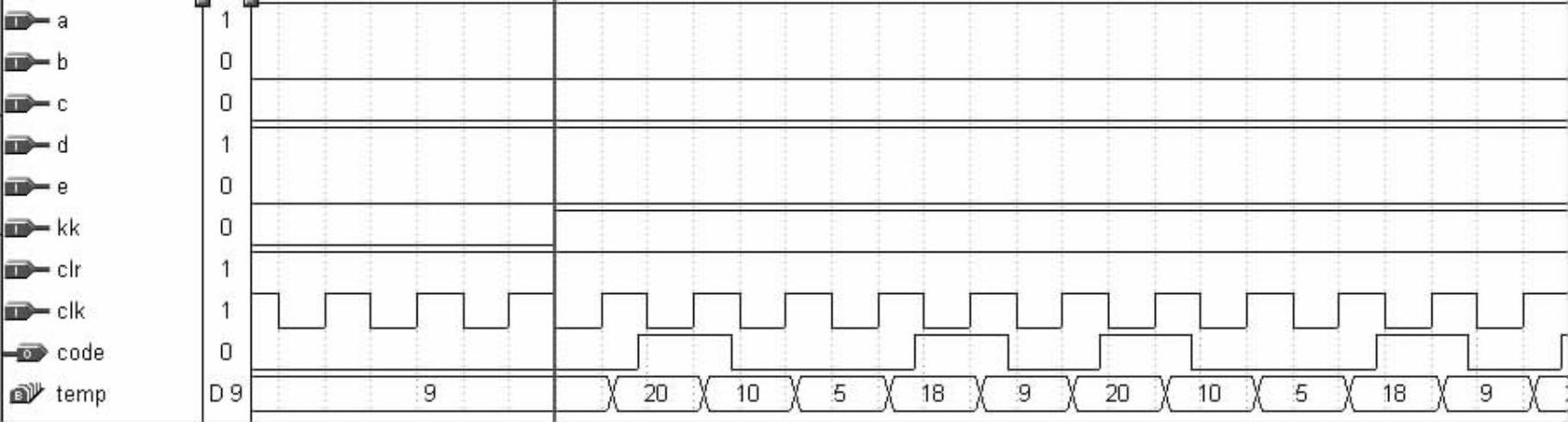

(1)分频

1)分析与设计。设计的m序列的频率是31kHz,因此要求在能提供一个31kHz的时钟信号用来产生m序列,该第二个分频器进行31分频产生,31分频器通过编程实现。本文中要实现信息源的数据速率1kbit/s时,对31kHz进行31分频即可,VHDL程序代码与以下的32分频代码类似,在此不做详细的描述。

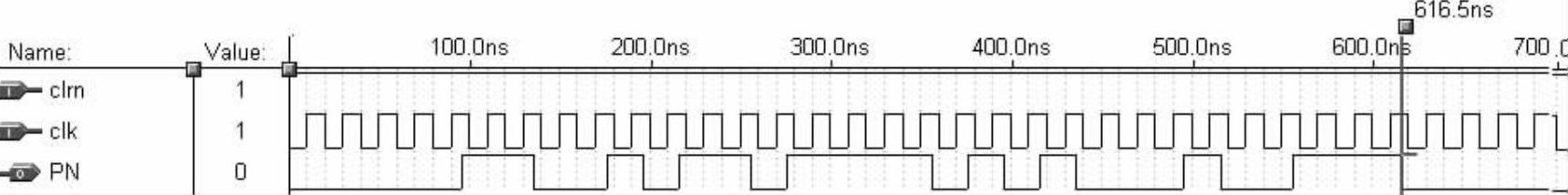

2)仿真结果。截取整31分频器的仿真结果局部波形如图5-45所示。由图可知,仿真结果是正确的。

图5-45 分频波形图

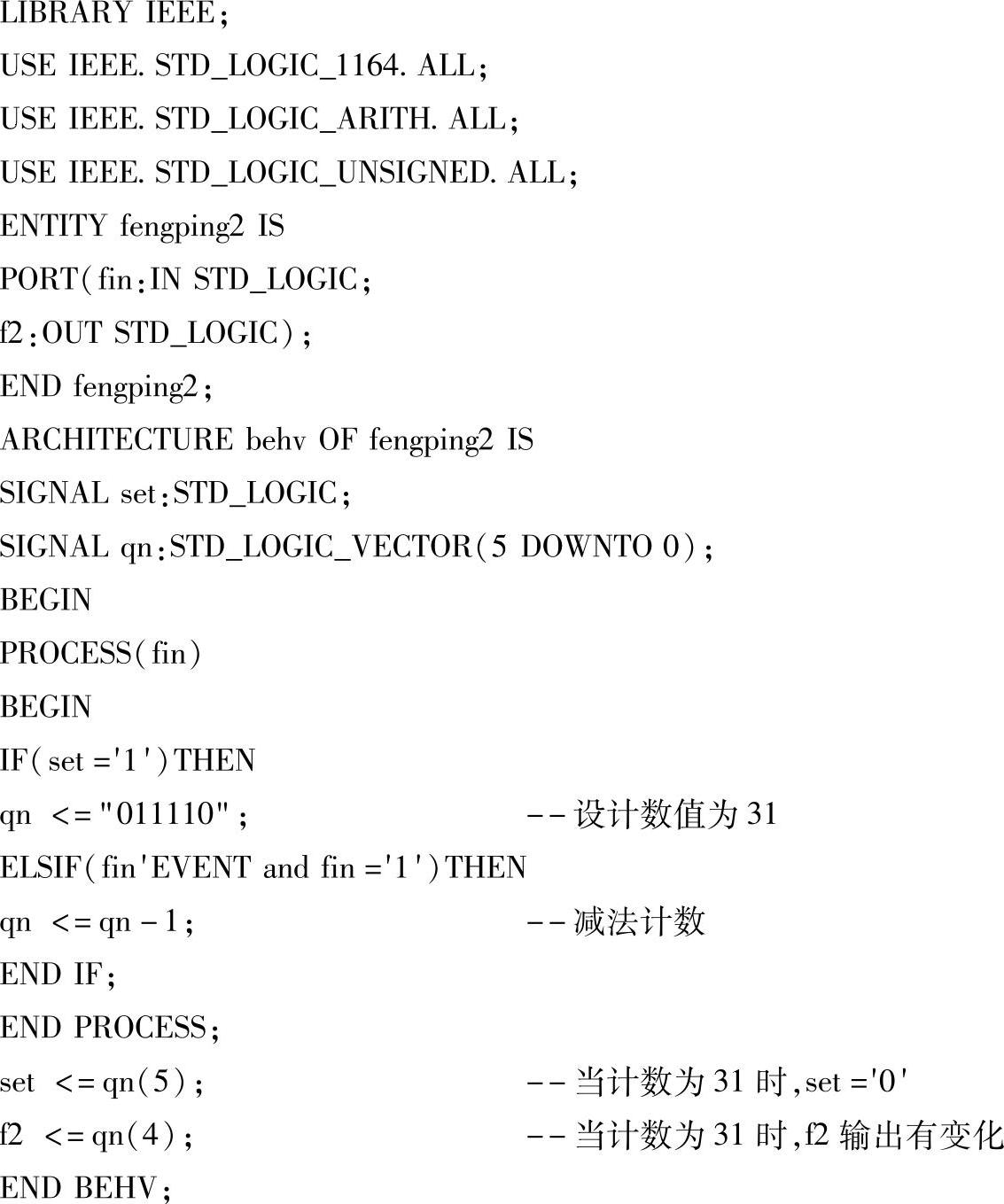

(2)信息码

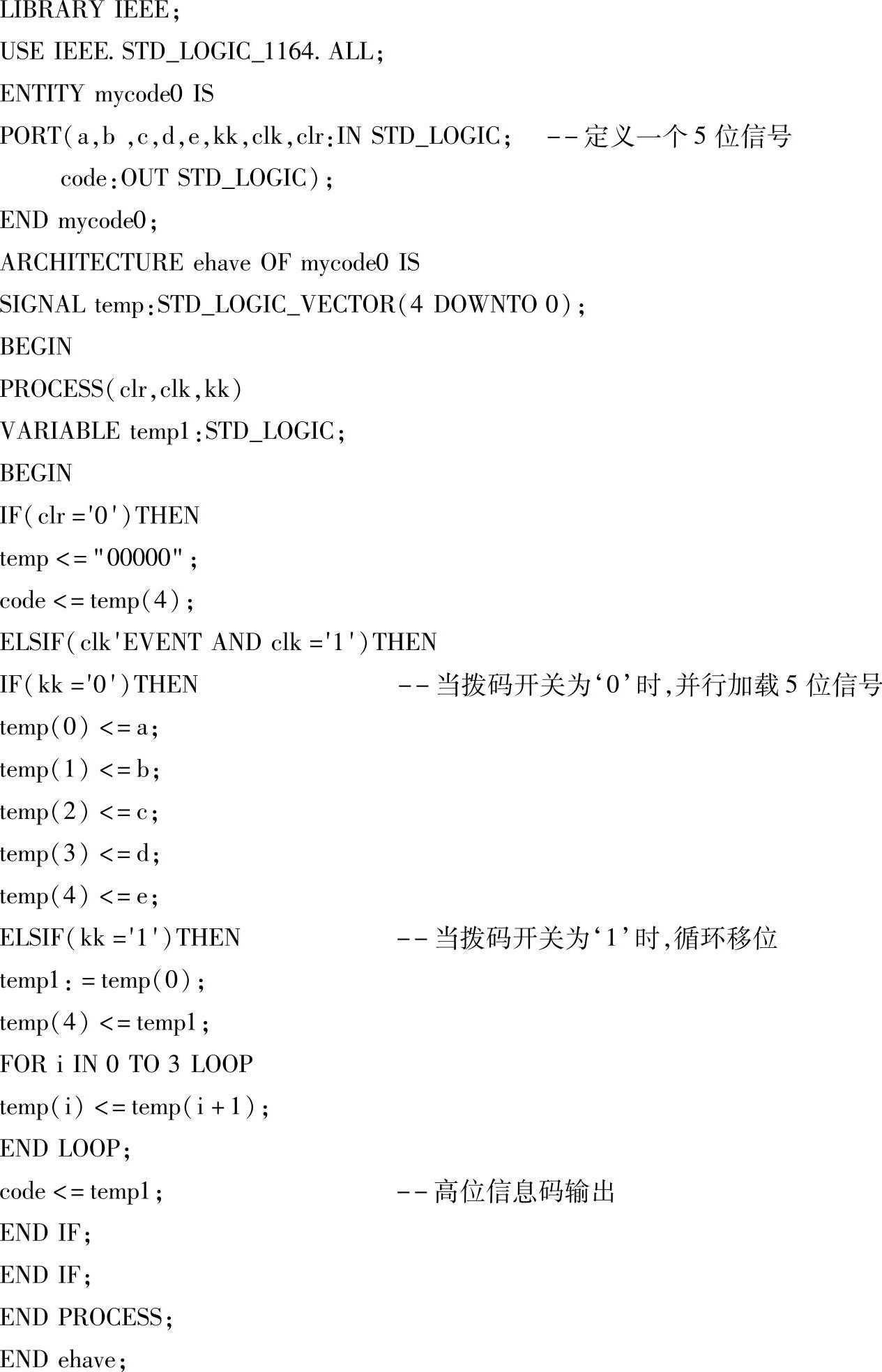

1)分析与设计。信号由5个拨码开关读入,并循环发送。用VHDL来实现。

2)仿真结果。截取信息码模块输出的仿真结果的局部波形如图5-46所示。

图5-46 信息码的波形图

e、d、c、b、a为输入信息码,kk为拨码开关,当kk为‘0’时,输入的信息码并行载入,从仿真结果图可知,当e、d、c、b、a为01001即9,clr是清0端,clk是输入时钟,code为高位信息码输出,temp为存储信息码循环发送的寄存器。当KK为‘0’时,temp保持,则输出的信息码code不变;当KK为‘1’时,信息码为01001即9时,当来一个脉冲时,信息码向右移一位,temp变为10100即20,则高位信息码即code输出为1,当信息码继续循环发送时,同样的原理,输出信息码code如图5-46所示,循环输出的信息码为10010。仿真结果是正确的。

(3)PN码产生器

1)分析与设计。采用的伪随机序列是码长为31的m序列。

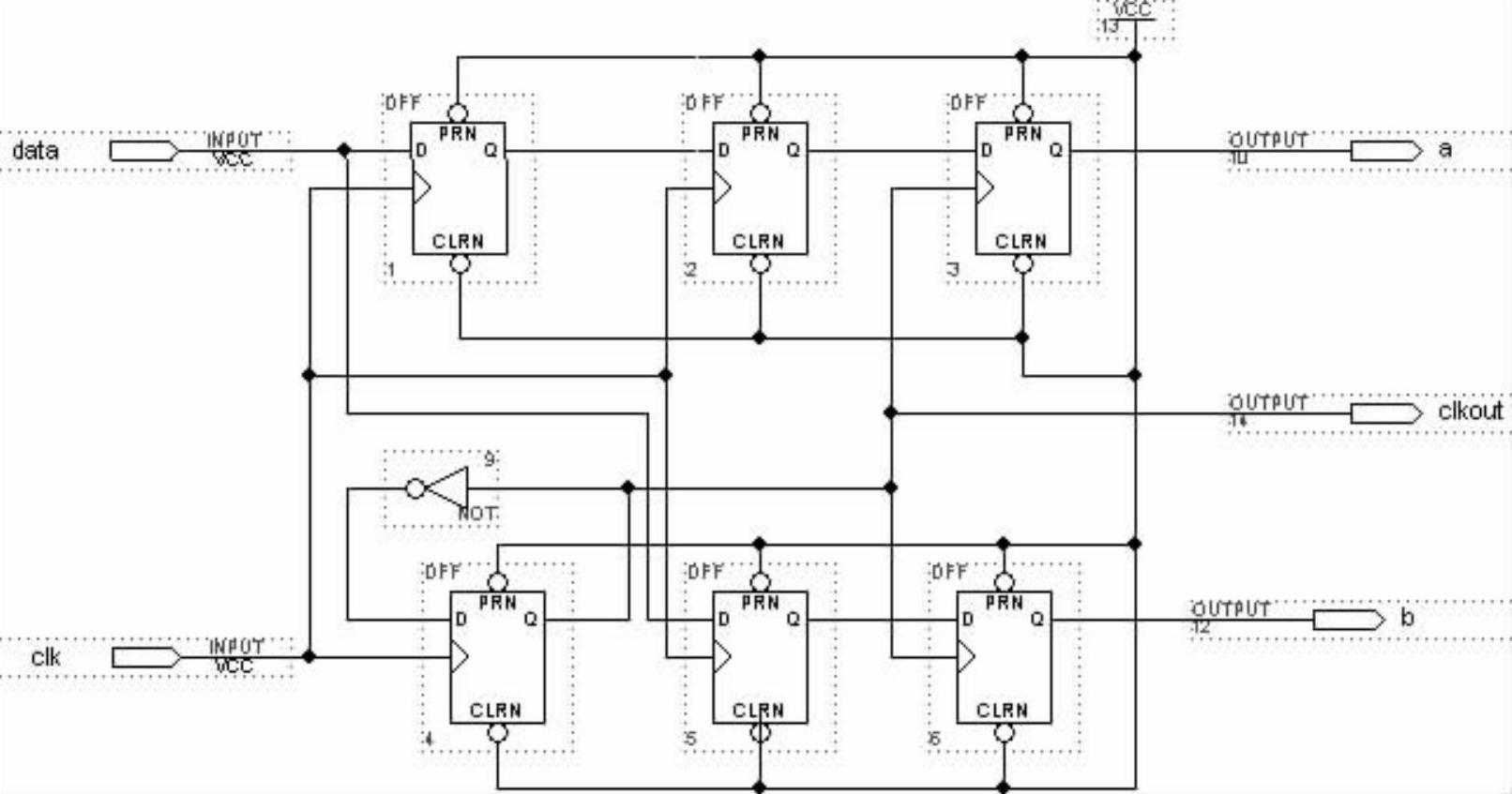

根据需要用5个D触发器来产生m序列,抽头位置为[25]时,其多项式是f(x)=x5+x2+1,其实现如图5-47所示。

图5-47 PN码原理图

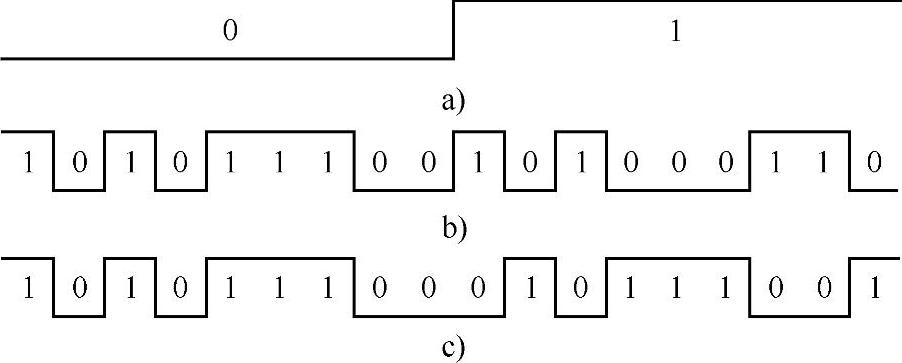

2)仿真结果。截取PN码产生器输出的一个周期(0~16.5ns)仿真结果局部波形,如图5-48所示。

其中,clrn是复位端,clk是输入的时钟信号,PN是所需的m序列。由图5-48所示的仿真结果可知,系统清0后,D触发器输出状态为00000,为了避免m序列产生器输出“全0”信号,图5-47在“模2相加”运算后添加了一个“非门”。最后仿真输出PN序列为0000011001011011110101000100111,仿真结果正确。

图5-48 PN码波形图

(4)扩频

1)分析与设计。实际应用中,为了达到将数据比特扩频的目的,通常的做法是用一扩频码序列与待发射的信息信号(数据比特)模2相加,并且扩频序列具有比数据比特窄得多的时宽,从而使扩频序列具有比数据序列高得多的频带。在设计中,扩频序列与基带数据单元工作在同步调制模式,也就是说,m序列与输入的数据比特电平变化沿对齐,如图5-49所示。

图5-49 扩频原理图

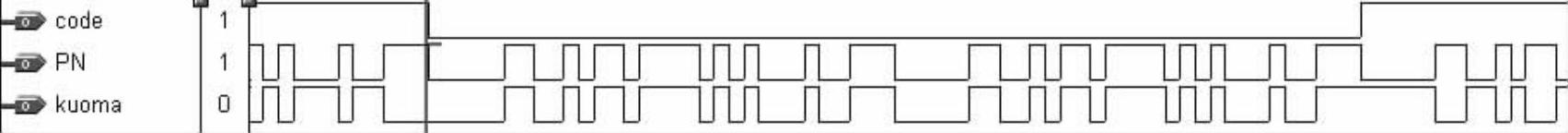

2)仿真结果。图5-50是扩频仿真结果的部分波形图,其中的code是信息信号,pn是扩频码,kuoma是信息信号扩频后的序列。当code为‘0’时,pn与kuoma相同,当code为‘1’时,pn与kuoma相反,仿真符合扩频原理,所以,仿真结果正确。

图5-50 扩频波形图

(5)串并转换

1)分析与设计。该模块完成的功能是:把串行输入数据转换成码速减半的并行a、b两路输出数据,a、b两路输出的数据在参考时钟下要同时有效。

在QuartusII开发环境下对该模块进行了设计。思路如下:采用寄存器作缓冲输出。首先,把串行输入数据的奇数序号码元存储起来,并延迟一个码元时间;在下一个码元(偶数序号)到来时刻,同时更新a路和b路输出寄存器。即把先前输入的码元分配给a路,此刻输入的码元分配给b路。其实现的原理图如图5-51所示。

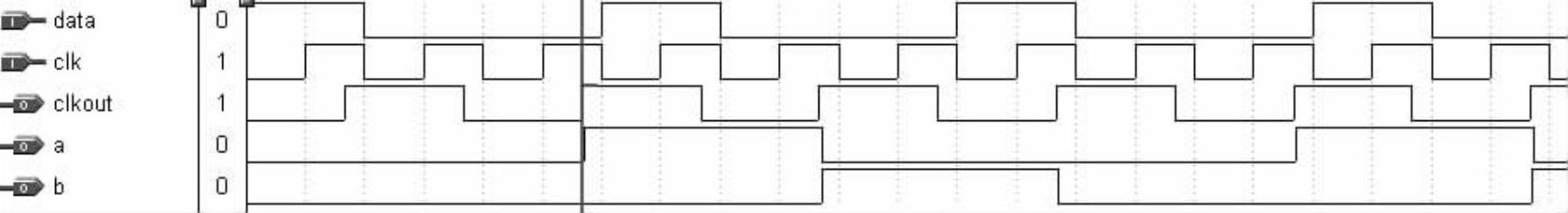

2)仿真结果。截取一部分仿真结果波形如图5-52所示,串行数据从data输入,clk为输入数据的参考时钟,即上升沿有效,clkout为输出数据的参考时钟,上升沿有效,a、b分路为a路和b路输出。假设在时钟信号clk作用,输入的信息序列data为1001001001,此时,输出数据的时钟信号clkout速率减半,由于电路实现二分频电路,a、b序列分别延迟一个clkout时钟才有输出,a路序列为10010,b路序列为01001,把a、b两路数据交错合并起来刚好是data信号,这表明输出的数据是符合要求的。

图5-51 串并转换原理图

图5-52 串并转换波形图

(6)差分编码

1)分析与设计。差分编码器的实现的功能是把绝对码变换成相对码。四进制差分编码把并行输入的双比特绝对码(AbsoluteCode)变换成双比特并行输入的相对码(Relative Code),其前后码元的相对码元(对应于相对相位)与绝对码元(对应于绝对相位)存在着下列关系:

Zir-Zi-1r=Zia(模4和) (5-1)(https://www.xing528.com)

或 Zir=Zia+Zi-1r(模4和) (5-2)

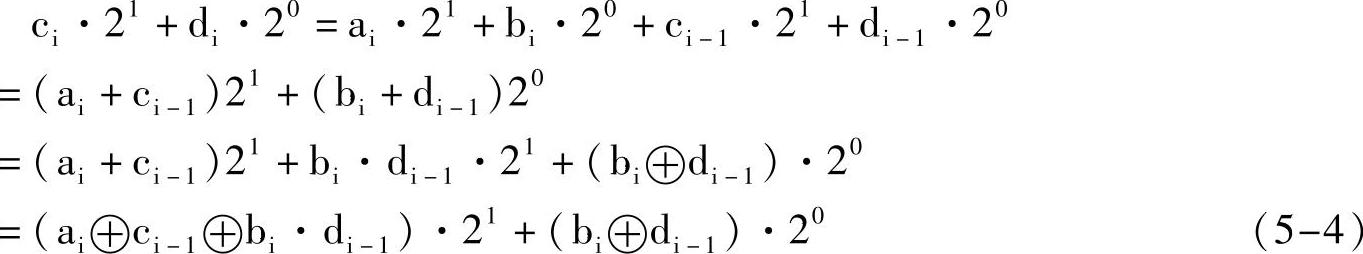

式中,下标a表示绝对码,下标r表示相对码,i是四进制码元的序号。若用二进制表示则

把式(5-3)代入式(5-2)可得

于是得到

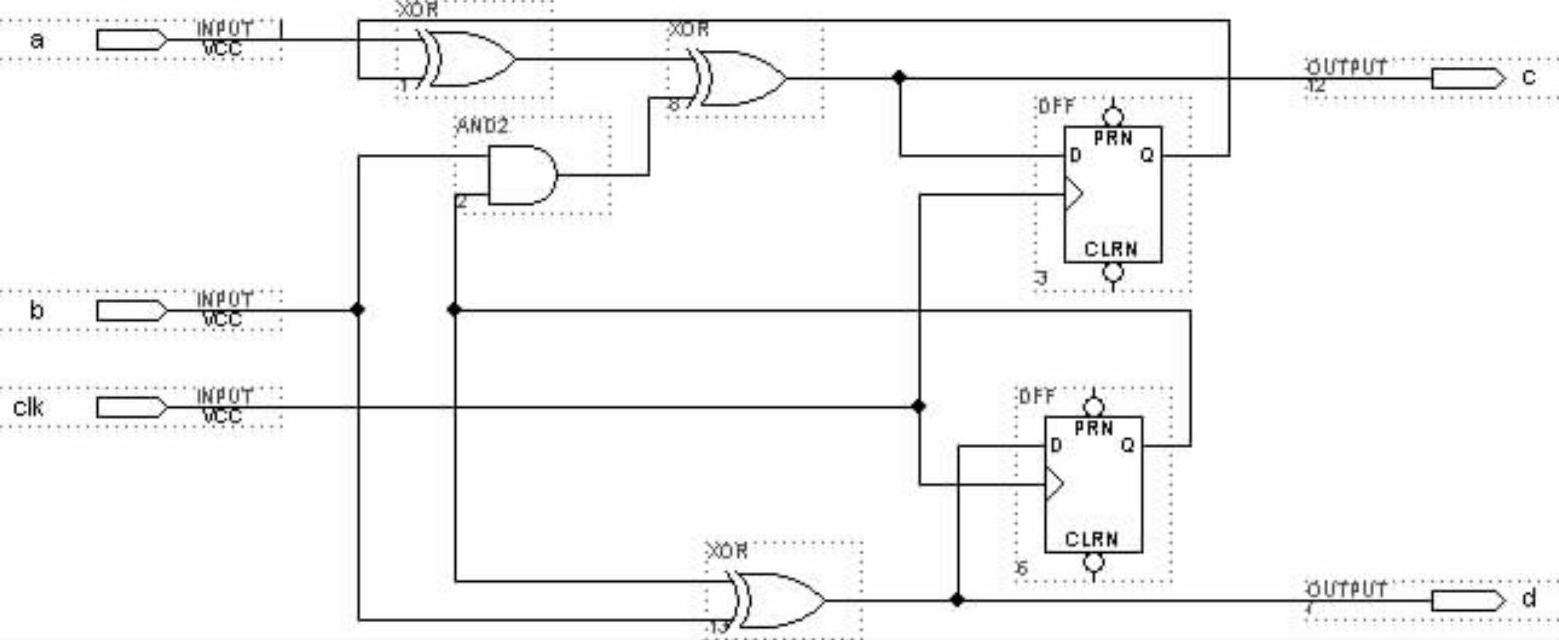

由式(5-5)得到四进制差分编码器的工作过程真值表见表5-13和四相差分编码电路如图5-53所示。

表5-13 四相差分调相(DQPSK)差分编码电路工作真值表

图5-53 四进制差分编码原理图

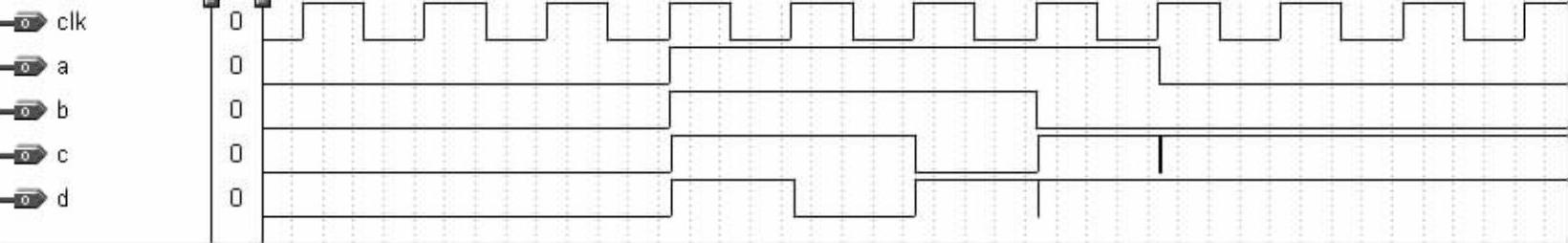

2)仿真结果。截取四进制差分编码的仿真结果局部波形如图5-54所示,clk为四进制差分编码电路的时钟,a、b分别是并行输入的绝对码,而c、d是输出的相对码。当a序列为001111,序列b为001110,输出时间延迟一个时钟,输出c为001101,d为001011。符合四进制差分编码要求。

图5-54 四进制差分编码波形图

(7)DDS

1)分析与设计。对于正弦信号发生器,它的输出可以用下式来描述

Sout=Asinwt=Asin(2πfoutt) (5-6)

式中,Sout是指信号发生器的输出信号波形;fout指输出信号对应的频率。

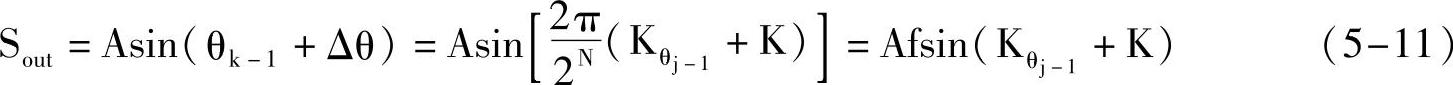

式(5-6)的表达式对于时间t是连续,为了用数字逻辑实现,必须进行离散化处理。用标准时钟clk进行抽样,令正弦信号的相位

θ=2πfoutt (5-7)

在一个clk周期Tclk内,相位θ的变化量为

式中,fclk指clk的频率,对于2π,可以理解成“满”相位。对Δθ进行数字量化,把2π切割成2N份,由此,每个clk周期的相位增量Δθ可用量化值K来表述为

且K为整数,与式(5-8)联立,可得

显然,信号发生器的输出可描述为

其中,θj-1指前一个clk周期的相位值,同样可以得出

由上面的推导可以看出,只要对相位的量化值进行简单的累加运算,就可以得到正弦信号的当前相位值;而用于累加的相位增量量化值K决定了信号的输出频率fout,并呈现简单的线性关系。DDS就是根据上述原理而设计的。

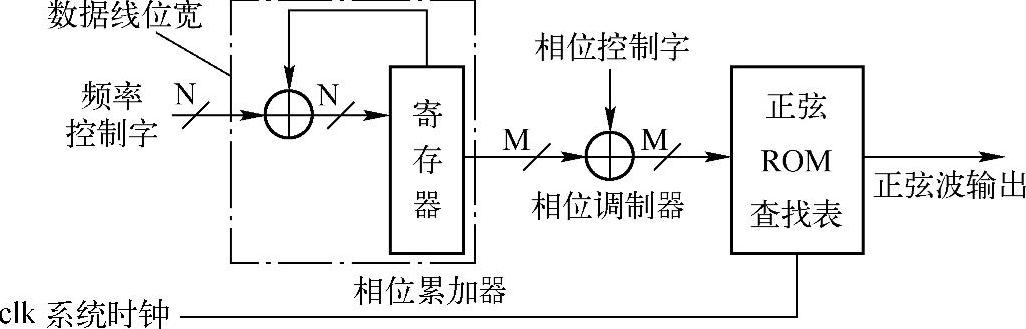

采用了Altera公司集成在QuartusⅡ5.1软件中的一些基本模块来实现DDS,整个系统主要由相位累加器、相位全加器、正弦ROM查找表3部分组成。图5-55是DDS的基本原理框图。

图5-55 DDS基本原理框图

①相位累加器。设相位累加器的初始值为0,累加步长为频率控制字K,则每一个时钟周期(1/fclk)的相位增量为K×2π/2N,一个完整正弦波周期需要进行2π/(K×2π/2N)=2N/K次累加,所以,输出信号周期Tout=(1/fclk)×2N/K,输出信号频率fout=K×fclk/2N。相位累加器在时钟的作用下,进行相位累加,当模块累加满量时就会产生一次溢出,完成一个周期性的动作,这个周期也就是DDS信号的一个频率周期。

②相位全加器。相位全加器即相位调制器,该模块把来自相位输入的8位初始相位(相位控制字)与相位累加器模块输出的累加相位相加产生新相位地址,再把相位地址作为正弦查找表ROM的地址。ROM的输出就是DDS模块产生的载波信号。当相位累加器模块的输出作为相位全加器模块的输入时,整个DDS电路就会产生频率随时间线性变化的输出。

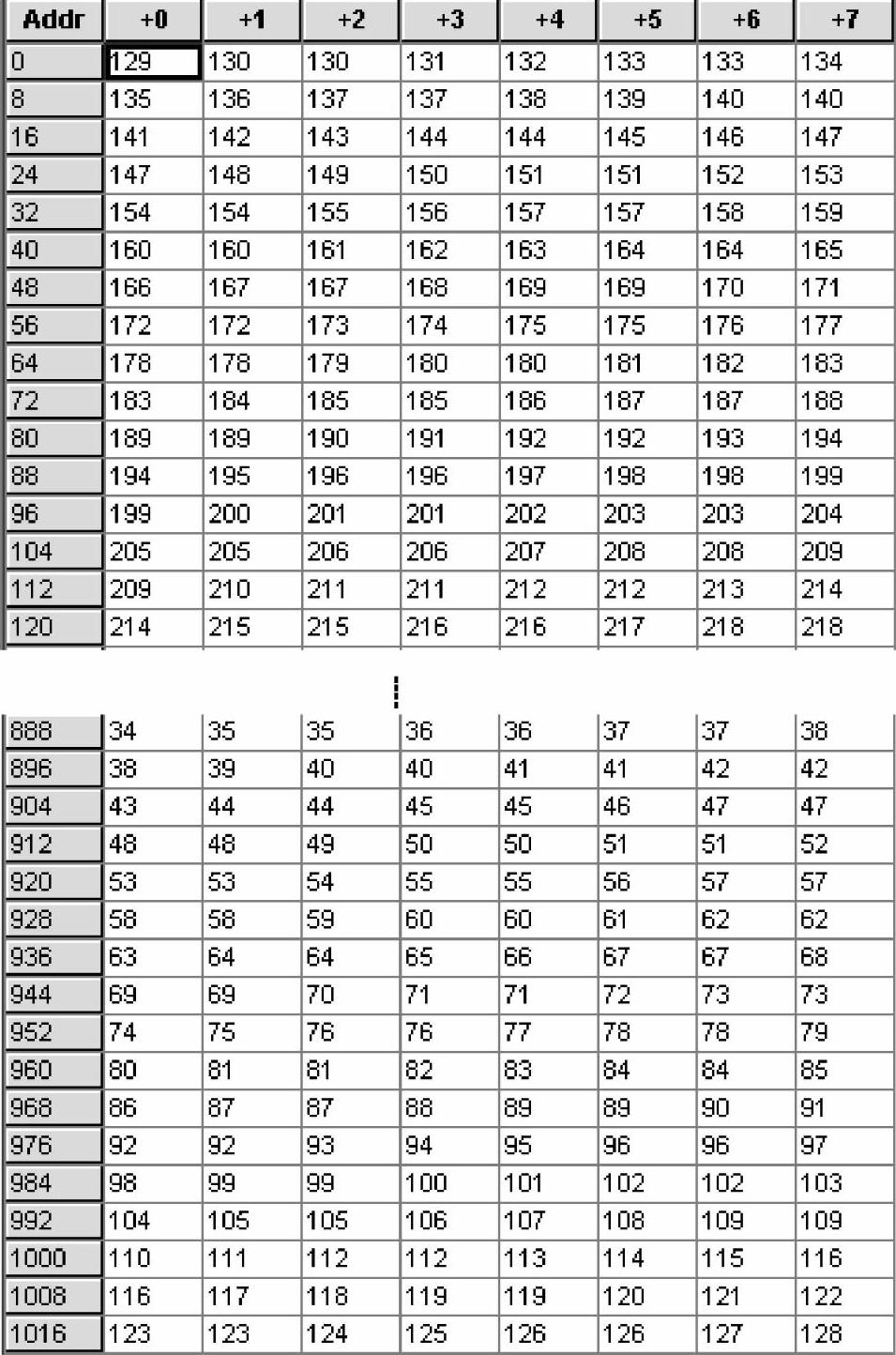

③ROM。ROM正弦查找表存储了一个完整正弦波周期的幅度值,设相位累加器的数据线宽度为10,则有2N=1024个点幅度值。先用其他工具计算出这2N=1024个点的幅度值,则相邻2个点的相位增量为2π/2N,这样各个点的位置就确定了该点的相位。以ROM依次存储2N个点的幅度值,便建立了各点相位(存储器地址)与幅值的影射关系。

本电路设计用的是8位的ROM,调用的ROM元件是用Altera公司集成在QuartusII5.1软件的LPM_ROM模块,查找表的mif文件即ROM存储的内容用hehe.mif文件提供,文件的内容由MATLAB计算得到,其内容数据如图5-56所示。

图5-56 LPM_ROM的mif文件

用相位累加器输出的数据作为波形存储器的取样地址,进行波形的相位——幅值转换,即可在给定的时间上确定输出的波形的抽样幅值。10位寻址ROM相当于把0°~360°的正弦信号离散成具有2N=1024个值的序列,若波形ROM有10位数据位,则2N=1024个点的幅值以8位二进制数值固化在ROM中,按照地址的不同可以输出相应相位的正弦信号的幅值。

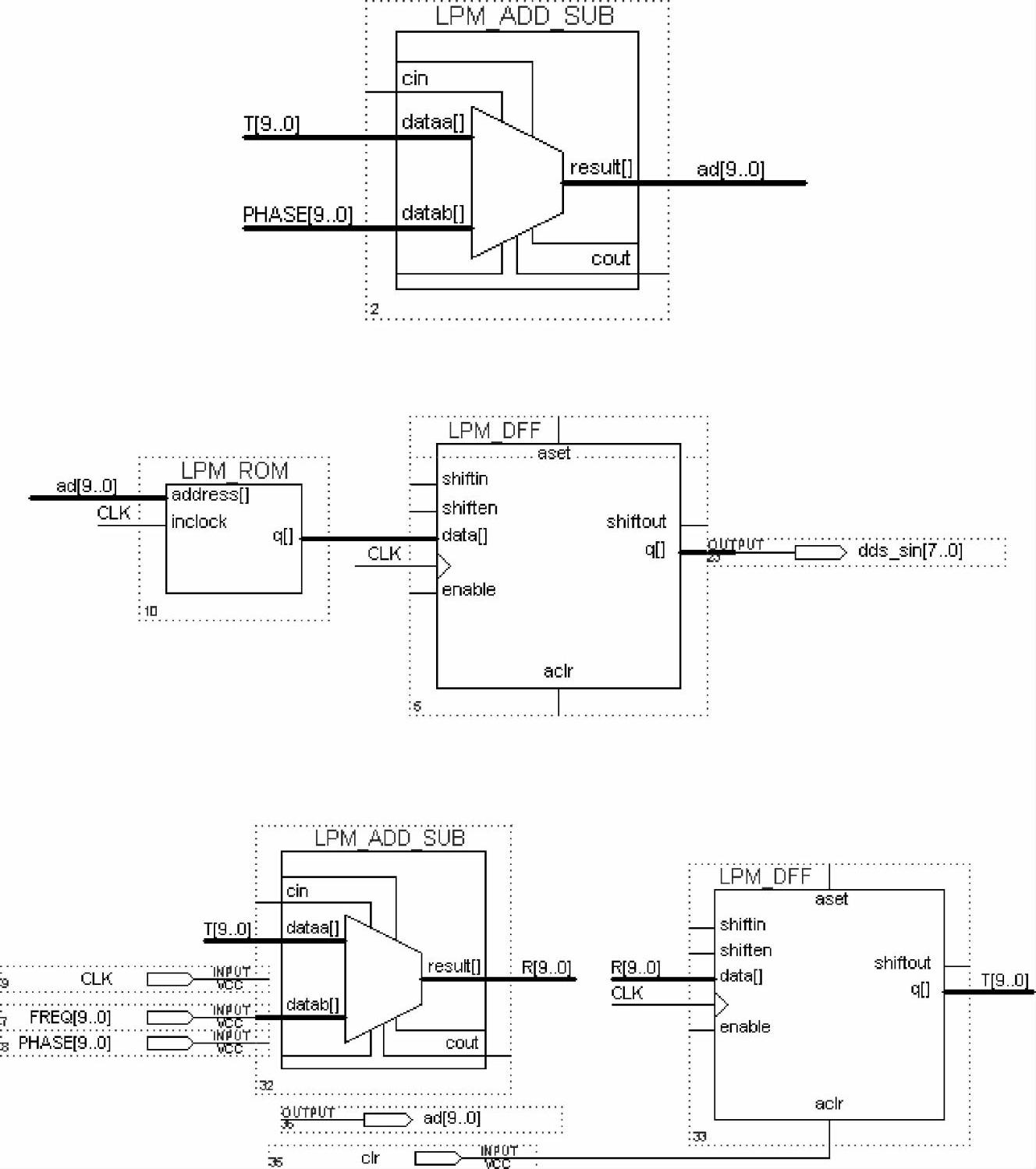

DDS完成的功能是,从相位累加器中产生相位信号,与输出的相位信号相加产生相位地址,通过相位地址从ROM表中读取相应的正弦函数值,产生输出频率信号的原理图,如图5-57所示。

图5-57 DDS原理图

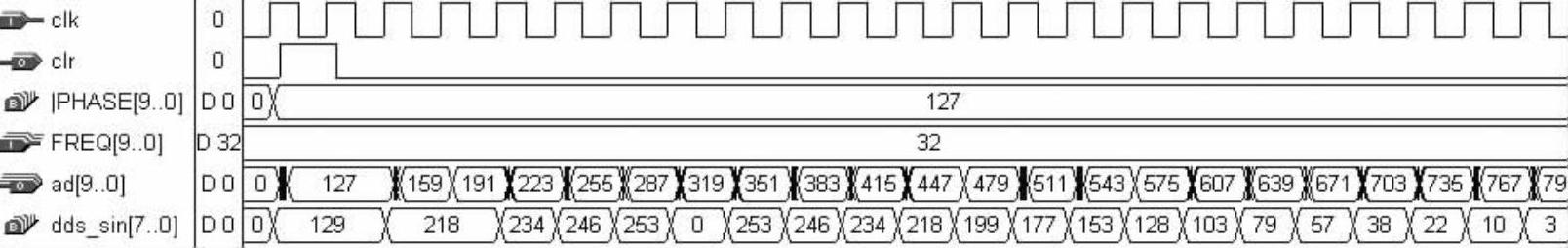

2)仿真结果。截取DDS仿真结果的局部波形,如图5-58所示。clk为系统时钟,clr为高电平有效的复位信号,FREQ[9..0]为频率控制字,可用于参考频率源对相位进行等可控间隔采样,这样可以改变输出信号的频率。PHASE[9..0]为输出的正弦信号的初始相位的地址,即相位加法器的相位控制字。T[9..0]为相位累加器的寄存器的输出端,即输出到相位加法器的输入端,ad[9..0]为相位加法器的输出端,即查找表ROM的地址。dds_sin[7..0]为整个DDS的输出信号,即数字化的正弦波。本文中要求DDS输出的正弦波信号的频率为961kHz,由于对正弦信号采样32个点,所以FREQ[9..0]频率控制字设为32,当上升沿脉冲到来时,PHASE[9..0]相位控制字设为127,则查找表地址ad[9..0]为127,dds_sin[7..0]输出值为218,当下一个上升沿脉冲到来时,相位累加器输出T[9..0]为32,ad[9..0]为127+32=159,则dds_sin[7..0]输出值为234。根据仿真结果,输出信号dds_sin[7..0]符合要求,结果正确。

图5-58 DDS波形图

(8)QPSK调制

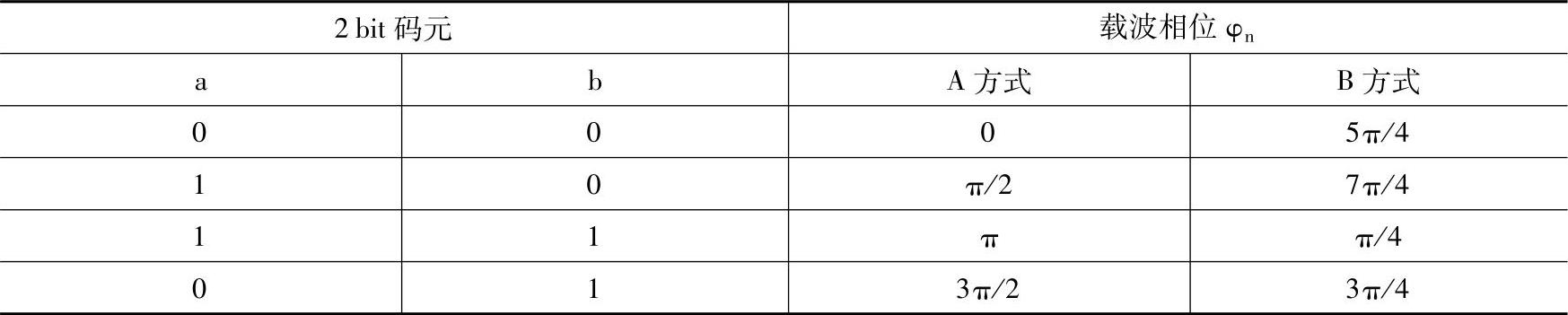

1)设计与分析。QPSK采用4种不同的载波相位来表示数字信息,每个载波相位代表2bit信息。假设前一比特用a表示,后一比特用b表示,则双比特码元ab与载波相位的关系见表5-14。

表5-14 QPSK信号载波相位与2bit码元关系

QPSK信号的实现有两种方法,相位选择法与正交调制法,相位选择法又分为A、B两种方式。采用相位选择法B方式来实现QPSK信号。

双比特序列ab作为相位控制字用于4种相位载波的选择控制。本文取N=10,先计算出这2N=1024个点的幅度值,量化为8位二进制数表示。相位为π/4和3π/4时,对应幅度值为218,存储地址分别为0001111111和0101111111;相位为5π/4和7π/4时,对应幅度值为38,存储地址分别为1001111111和1101111111。

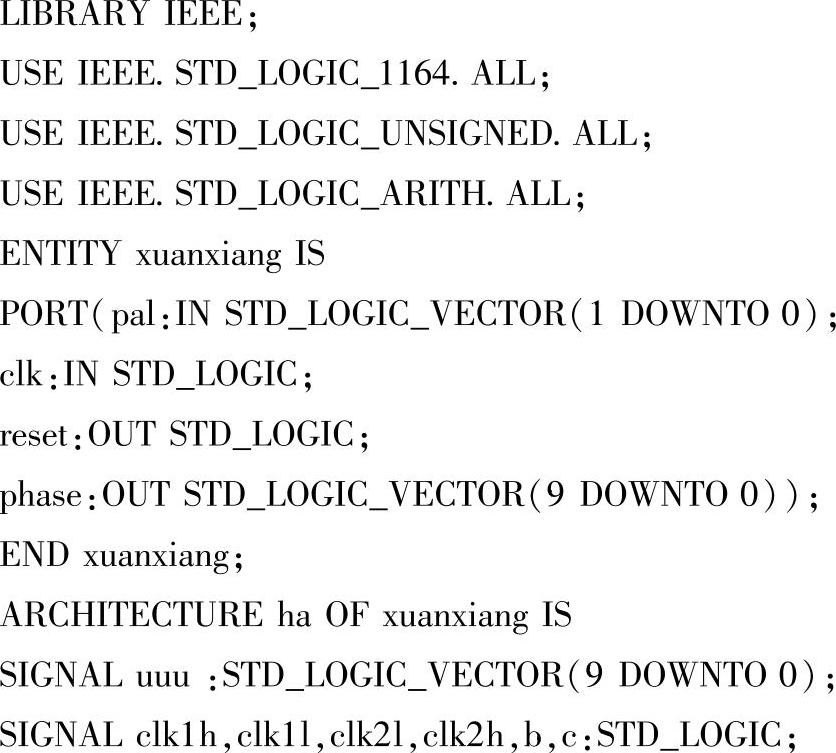

用VHDL语句来完成逻辑选相即QPSK调制,程序如下:

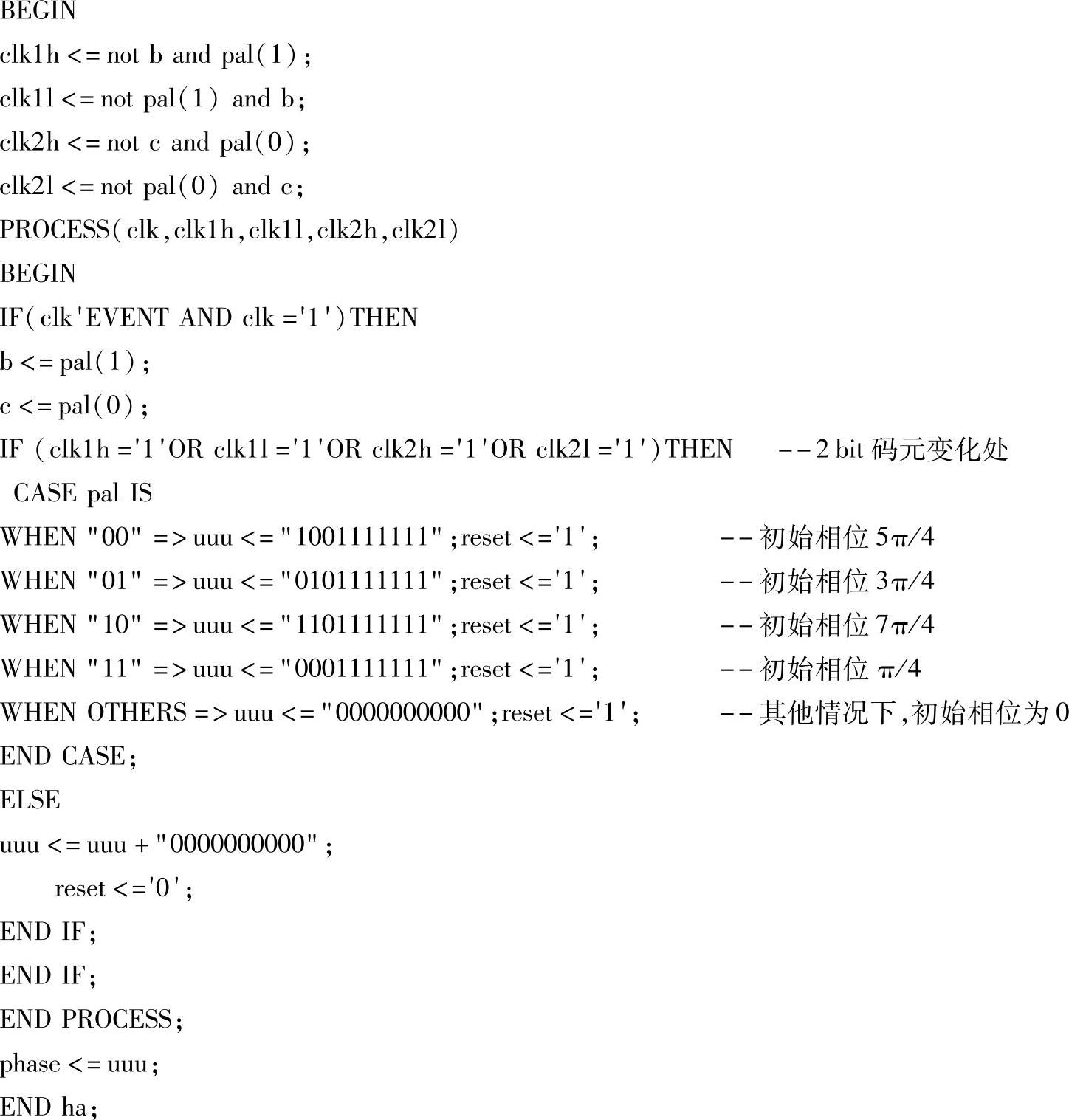

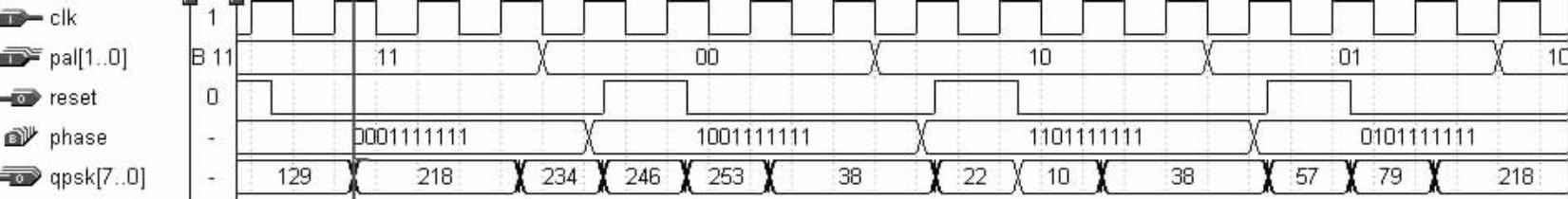

2)仿真结果。截取局部仿真波形,如图5-59所示,clk为系统时钟,reset为高电平有效的复位信号,pal为2bit码元,phase为DDS的初始相位地址即相位控制字。qpsk[7..0]为QPSK调制后输出的信号,当2bit码元pal为“11”时,phase为0001111111,qpsk[7..0]输出为218,pal为“00”时,phase为1001111111,qpsk[7..0]输出为38,pal为“10”时,phase为110111111101,qpsk[7..0]输出为38,pal为“01”时,phase为0101111111,qpsk[7..0]输出为38,仿真结果符合要求。

图5-59 QPSK调制波形图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。